Изобретение относится к области вычислительной техники и может быть использовано в контроллерах и ЭВМ.

Целью изобретения является повышение быстродействия устройства.

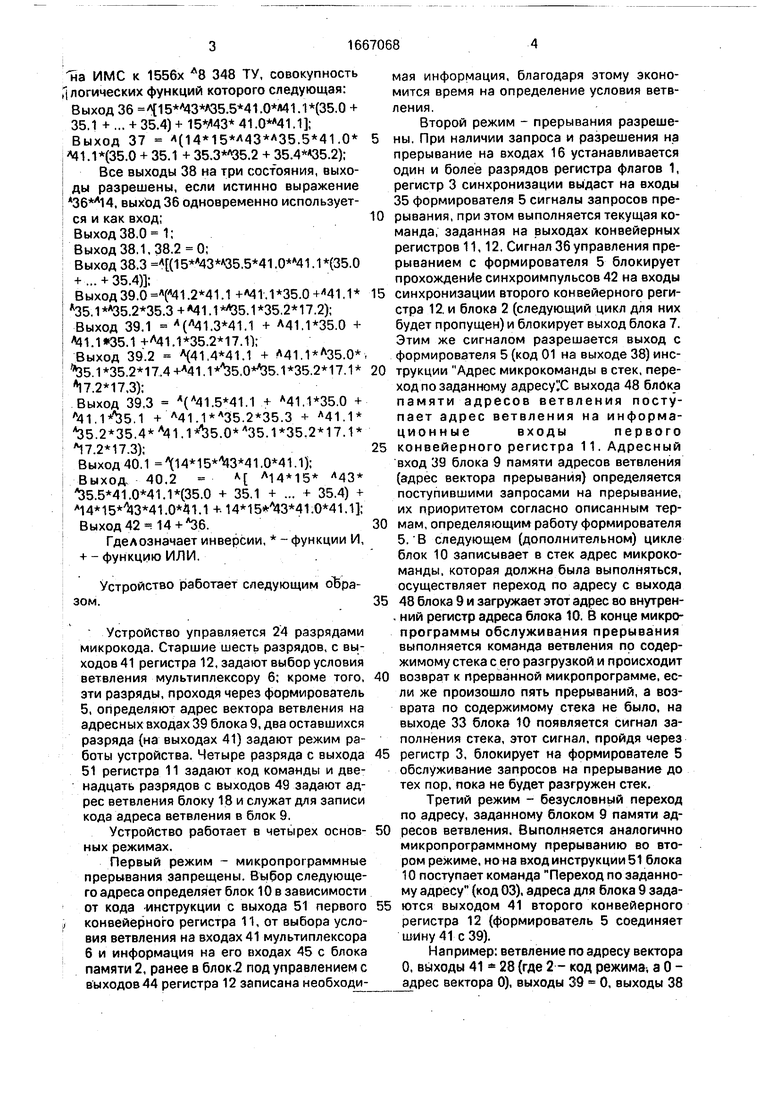

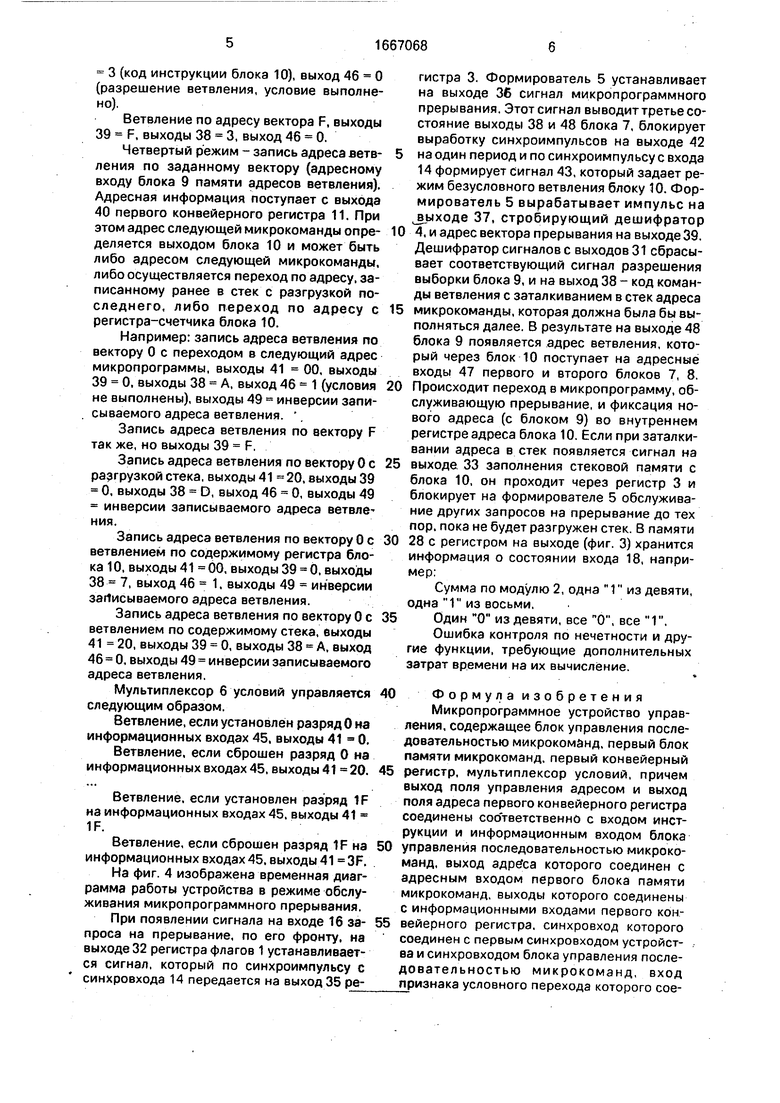

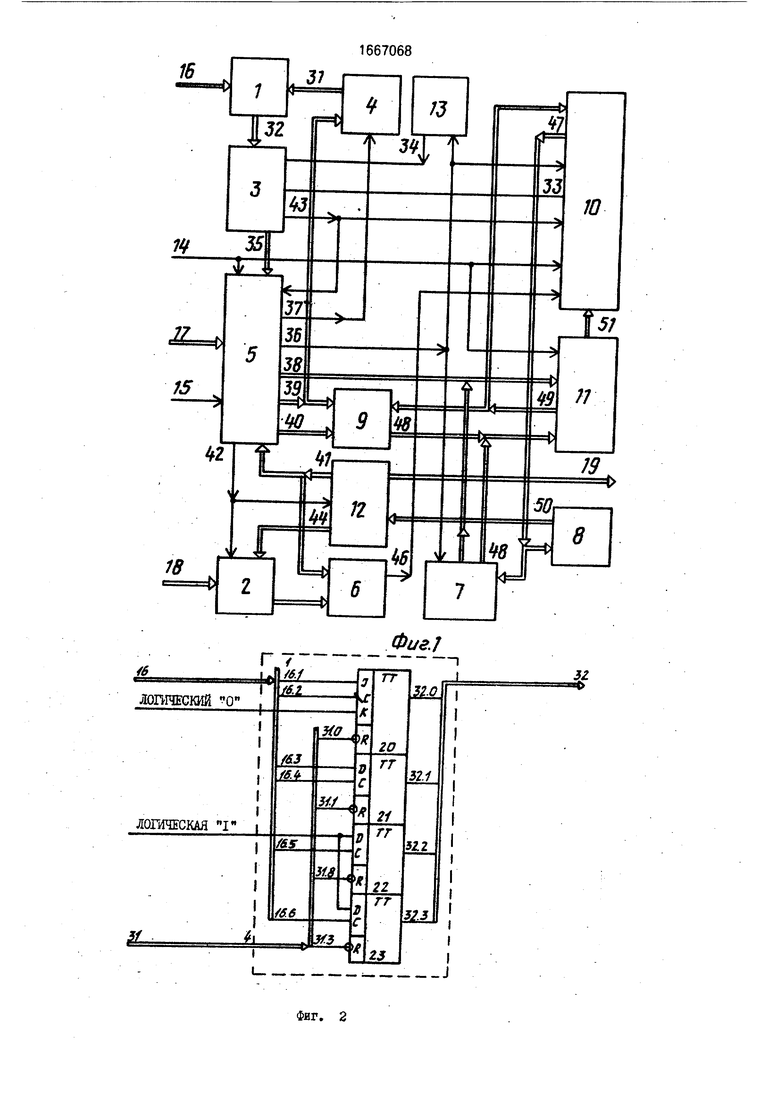

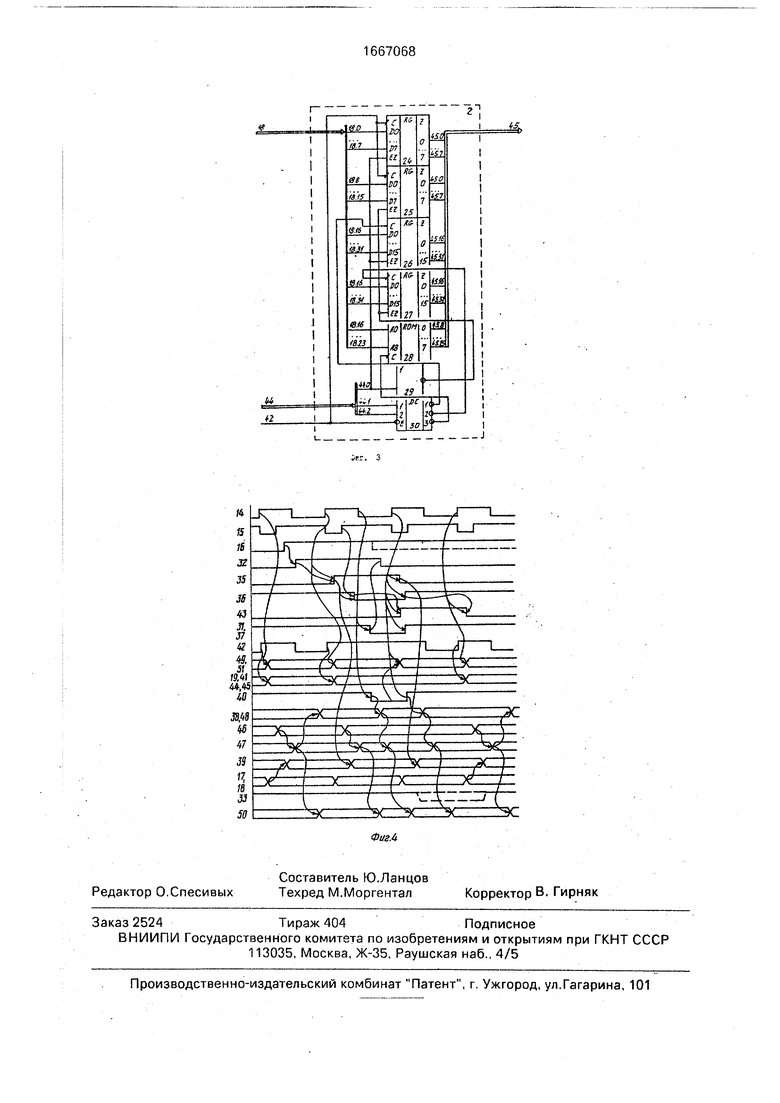

На фиг. 1 приведена схема устройства; на фиг. 2 - пример реализации регистра флагов; на фиг. 3 - пример реализации блока памяти состояний; на фиг. 4 - временные диаграммы, иллюстрирующие работу устройства.

Микропрограммное устройство управления содержит (фиг. 1) регистр 1 флагов, блок 2 памяти состояний, регистр 3 синхронизации, дешифратор 4, формирователь 5 сигналов местного управления, мультиплексор 6 условий, первый 7 и второй в блоки памяти микрокоманд, блок 9 памяти адресов ветвления, блок 10 управления последовательностью микрокоманд, первый 11 и второй 12 конвейерные регистры, элемент НЕ 13, первый 14 и второй 15 синхровходы, вход 16 запросов на прерывание, вход 17 выбора адреса прерывания, вход 18 логических условий и выход 19.

Регистр 1 флагов (фиг. 2) содержит четы- з ре триггера 20-23.Г

Блок 2 памяти состояний (фиг. 3) содер- С/) жит четыре регистра 24-27, память 28, эле- мент НЕ 29 и дешифратор 30.

Кроме того, обозначены выходы 31 де- шифратора 4, выход 32 регистра 1 флагов, выход 33 признака заполнения стековой памяти блока 10, выход 34 элемента НЕ, выход 35 регистра 3 синхронизации, выход 36 уп- О равления прерыванием формирователя 5, О4 выход 37 признака вектора прерывания xj формирователя 5, выход 38 инструкции, вы- Ј} ход 39 адреса вектора прерывания и выход ф 40 управления формированием адресов вет- лл влений формирователя 5, выход 41 поля анализа условий регистра 12, синхровыход 42 формирователя 5, второй выход 43 регистра 3, выход 44 поля адреса регистра 12, выход 45 блока 2 памяти, выход 46 мультиплексора 6. выход 47 адреса блока 10, выход 48 блока 7 памяти, выход 49 адреса регистра 11, выход 50 блока 8 памяти и вход 51 инструкции блока 10.

Формирователь 5 сигналов местного управления может быть выполнен в виде ПЛМ

на ИМС к 1556х Л8 348 ТУ, совокупность логических функций которого следующая: Выход 36 ...1(35.0 + 35.1 +... + 35.4)+ .. Выход 37 (..0 1.1(35.0 + 35.1 + 35..2 + 35..2);

Все выходы 38 на три состояния, выходы разрешены, если истинно выражение . выход 36 одновременно используется и как вход; Выход 38.0 1; Выход 38.1, 38.2 0;

Выход 38.3 (...1(35.0 + ... + 35.4);

Выход 39.0 Л(М1..1 +М1...1 35...3+М1....2); Выход 39.1 Х(Л41..1 + М1..0 + М1..1 +Л41...1); Выход 39.2 Л(41..1 + М1..0 - 35...4+M1.....1 17.,3);

Выход 39.3 А(Л41..1 + А41..0 + Л41..1 + Л41...3 + М1.1 35..4 А41..О А35..2 17.1 17..3):

Выход 40.1 (..1); Выход 40.2 л А43 35...1(35.0 + 35.1 + ... + 35.4) + А14 ..1 + .. Выход 42 .

Где А означает инверсии, - функции И, + - функцию ИЛИ.

Устройство работает следующим обра- зом.

Устройство управляется 24 разрядами микрокода. Старшие шесть разрядов, с выходов 41 регистра 12, задают выбор условия ветвления мультиплексору 6; кроме того, эти разряды, проходя через формирователь 5, определяют адрес вектора ветвления на адресных входах 39 блока 9, два оставшихся разряда (на выходах 41) задают режим работы устройства. Четыре разряда с выхода 51 регистра 11 задают код команды и двенадцать разрядов с выходов 49 задают адрес ветвления блоку 18 и служат для записи кода адреса ветвления в блок 9.

Устройство работает в четырех основных режимах.

Первый режим - микропрограммные прерывания запрещены. Выбор следующего адреса определяет блок 10 в зависимости от кода инструкции с выхода 51 первого конвейерного регистра 11, от выбора условия ветвления на входах 41 мультиплексора 6 и информация на его входах 45 с блока памяти 2, ранее в блок.2 под управлением с выходов 44 регистра 12 записана необходимая информация, благодаря этому экономится время на определение условия ветвления.

Второй режим - прерывания разрешены, При наличии запроса и разрешения на прерывание на входах 16 устанавливается один и более разрядов регистра флагов 1, регистр 3 синхронизации выдаст на входы 35 формирователя 5 сигналы запросов пре0 рывания, при этом выполняется текущая команда, заданная на выходах конвейерных регистров 11,12. Сигнал 36управления прерыванием с формирователя 5 блокирует прохождение синхроимпульсов 42 на входы

5 синхронизации второго конвейерного регистра 12. и блока 2 (следующий цикл для них будет пропущен) и блокирует выход блока 7. Этим же сигналом разрешается выход с формирователя 5 (код 01 на выходе 38) инс0 трукции Адрес микрокоманды в стек, переход по заданному адресуХ выхода 48 блока памяти адресов ветвления поступает адрес ветвления на информационныевходыпервого

5 конвейерного регистра 11. Адресный вход 39 блока 9 памяти адресов ветвления (адрес вектора прерывания) определяется поступившими запросами на прерывание, их приоритетом согласно описанным тер0 мам. определяющим работу формирователя 5, В следующем (дополнительном) цикле блок 10 записывает в стек адрес микрокоманды, которая должна была выполняться, осуществляет переход по адресу с выхода

5 48 блока 9 и загружает этот адрес во внутрен- . ний регистр адреса блока 10. В конце микропрограммы обслуживания прерывания выполняется команда ветвления по содержимому стека с его разгрузкой и происходит

0 возврат к прерванной микропрограмме, если же произошло пять прерываний, а возврата по содержимому стека не было, на выходе 33 блока 10 появляется сигнал заполнения стека, этот сигнал, пройдя через

5 регистр 3, блокирует на формирователе 5 обслуживание запросов на прерывание до тех пор, пока не будет разгружен стек.

Третий режим - безусловный переход по адресу, заданному блоком 9 памяти ад0 ресов ветвления. Выполняется аналогично микропрограммному прерыванию во втором режиме, нона вход инструкции 51 блока 10 поступает команда Переход по заданному адресу (код 03), адреса для блока 9 зада5 ются выходом 41 второго конвейерного регистра 12 (формирователь 5 соединяет шину 41 с 39).

Например: ветвление по адресу вектора О, выходы 41 28 (где 2 - код режима, а 0 - адрес вектора 0), выходы 39 - 0, выходы 38

3 (код инструкции блока 10), выход 46 О (разрешение ветвления, условие выполнено).

Ветвление по адресу вектора F, выходы

39 F, выходы 38 3, выход 46 0.

Четвертый режим - запись адреса ветвления по заданному вектору (адресному входу блока 9 памяти адресов ветвления). Адресная информация поступает с выхода

40первого конвейерного регистра 11. При этом адрес следующей микрокоманды определяется выходом блока 10 и может быть либо адресом следующей микрокоманды, либо осуществляется переход по адресу, записанному ранее в стек с разгрузкой последнего, либо переход по адресу с регистра-счетчика блока 10.

Например: запись адреса ветвления по вектору 0 с переходом в следующий адрес микропрограммы, выходы 41 00, выходы 39 0, выходы 38 А, выход 46 1 (условия не выполнены), выходы 49 инверсии записываемого адреса ветвления.

Запись адреса ветвления по вектору F так же, но выходы 39 F.

Запись адреса ветвления по вектору 0 с разгрузкой стека, выходы , выходы 39 0, выходы 38 D, выход 46 0, выходы 49 инверсии записываемого адреса ветвления.

Запись адреса ветвления по вектору 0 с ветвлением по содержимому регистра блока 10, выходы 41 00, выходы 39 0, выходы 38 7, выход 46 1, выходы 49 инверсии записываемого адреса ветвления.

Запись адреса ветвления по вектору 0 с ветвлением по содержимому стека, выходы

, выходы 39 0. выходы 38 А, выход 46 0, выходы 49 инверсии записываемого адреса ветвления.

Мультиплексор 6 условий управляется следующим образом.

Ветвление, если установлен разряд 0 на информационных входах 45, выходы .

Ветвление, если сброшен разряд 0 на информационных входах 45, выходы 41 20.

Ветвление, если установлен разряд 1F на информационных входах 45, выходы 41 - 1F.

Ветвление, если сброшен разряд 1F на информационных входах 45. выходы 41 3F.

На фиг. 4 изображена временная диаграмма работы устройства в режиме обслуживания микропрограммного прерывания.

При появлении сигнала на входе 16 запроса на прерывание, по его фронту, на выходе 32 регистра флагов 1 устанавливается сигнал, который по синхроимпульсу с синхровхода 14 передается на выход 35 регистра 3. Формирователь 5 устанавливает на выходе 36 сигнал микропрограммного прерывания. Этот сигнал выводит третье состояние выходы 38 и 48 блока 7, блокирует выработку синхроимпульсов на выходе 42 5 на один период и по синхроимпульсу с входа 14 формирует сигнал 43, который задает режим безусловного ветвления блоку 10. Формирователь 5 вырабатывает импульс на выходе 37, стробирующий дешифратор

10 4, и адрес вектора прерывания на выходе 39. Дешифратор сигналов с выходов 31 сбрасывает соответствующий сигнал разрешения выборки блока 9, и на выход 38 - код команды ветвления с заталкиванием в стек адреса

15 микрокоманды, которая должна была бы выполняться далее. В результате на выходе 48 блока 9 появляется адрес ветвления, который через блок 10 поступает на адресные входы 47 первого и второго блоков 7, 8.

0 Происходит переход в микропрограмму, обслуживающую прерывание, и фиксация нового адреса (с блоком 9) во внутреннем регистре адреса блока 10. Если при заталкивании адреса в стек появляется сигнал на

5 выходе 33 заполнения стековой памяти с блока 10, он проходит через регистр 3 и блокирует на формирователе 5 обслуживание других запросов на прерывание до тех пор, пока не будет разгружен стек. В памяти

0 28 с регистром на выходе (фиг. 3) хранится информация о состоянии входа 18, например:

Сумма по модулю 2, одна 1 из девяти, одна 1 из восьми.

5 Один О из девяти, все О, все 1.

Ошибка контроля по нечетности и другие функции, требующие дополнительных затрат времени на их вычисление.

0Формула изобретения

Микропрограммное устройство управления, содержащее блок управления последовательностью микрокоманд, первый блок памяти микрокоманд, первый конвейерный

5 регистр, мультиплексор условий, причем выход поля управления адресом и выход поля адреса первого конвейерного регистра соединены соответственно с входом инструкции и информационным входом блока

0 управления последовательностью микрокоманд, выход адреса которого соединен с адресным входом первого блока памяти микрокоманд, выходы которого соединены с информационными входами первого кон5 вейерного регистра, синхровход которого соединен с первым синхровходом устройства и синхровходом блока управления после- довательностью микрокоманд, вход признака условного перехода которого соединен с выходом мультиплексора условий. отличающееся тем, что, с целью повышения быстродействия, устройство содержит второй блок памяти микрокоманд, блок памяти состояний, блок памяти адресов ветвлений, элемент НЕ, формирователь сигналов местного управления, регистр флагов, дешифратор, регистр синхронизации и второй конвейерный регистр, выход поля адреса и выход поля микроопераций которого соединены соответственно с адресным входом блока памяти состояний и выходом устройства, вход выбора адреса прерывания и второй синхровход которого подключены соответственно к первому информационному и первому стробирующему входам формирователя сигналов местного управления, вторые информационный и стробирующий входы которого подключены соответственно к первому выходу регистра синхронизации и первому синхровходу устройства, входы запросов на прерывание которого подключены к установочным входам регистра флагов, выход которого соединен с первым информационным входом регистра синхронизации, второй информационный и вход записи которого соединены соответственно с выходом признака заполнения стековой памяти блока управления последовательностью микрокоманд и выходом элемента НЕ, вход которого соединен с входом разрешения наращивания адреса блока управления последовательностью микрокоманд, выходом управления прерыванием формирователя сигналов местного управления и входом выборки первого блока памяти микрокоманд, второй выход регистра синхронизации соединен с входом

разрешения анализа условий блока управления последовательностью микрокоманд и третьим информационным входом формирователя сигналов местного управления,

выход адреса вектора прерывания которого соединен с адресным входом блока памяти адресов ветвлений и информационным входом дешифратора, выходы и стробирующий вход которого соединен соответственно с

входами сброса регистра флагов и выходом признака вектора прерывания формирователя сигналов местного управления, выход инструкций и выход управления формированием адресов ветвлений которого соединены соответственно с информационным входом первого конвейерного регистра и входом записи-чтения блока памяти адресов ветвлений, информационный вход и выход которого соединены соответственно с

выходом поля адреса и информационным входом первого конвейерного регистра,, синхровыход формирователя сигналов местного управления соединен с входом записи второго конвейерного регистра и входом

чтения-записи блока памяти состояний, информационный вход и выход которого подключены соответственно к входу логических условий устройства и информационному входу мультиплексора условий, управляющий вход которого соединен с четвертым информационным входом формирователя сигналов местного управления и выходом поля анализа условий второго конвейерного регистра, информационный вход которого

соединен с выходом второго блока памяти микрокоманд, адресный вход которого соединен с выходом адреса блока управления последовательностью микрокоманд.

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство управления накопителями на магнитных дисках | 1988 |

|

SU1532956A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

Изобретение относится к вычислительной технике и может быть использовано в контроллерах и ЭВМ. Цель изобретения - повышение быстродействия. Устройство включает блок управления последовательностью микрокоманд, два блока памяти микрокоманд, два конвейерных регистра, мультиплексор условий, блок памяти состояний, регистр флагов, регистр синхронизации, дешифратор, элемент НЕ, формирователь сигналов местного управления и блок памяти адресов ветвления. 4 ил.

Фиг. 2

w

j

irr. 3

| Дж | |||

| Мик, Дж | |||

| Брик | |||

| Проектирование микропроцессорных устройств с разрядномодульной организацией, кн | |||

| I | |||

| M: Мир, 1984, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| СЧЕТНЫЙ ДИСК ДЛЯ РАСЧЕТА СОСТАВНЫХ ЧАСТЕЙ ПИЩИ | 1919 |

|

SU284A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1988-09-01—Подача