оэ со со со со

СЛ

Изобретение относится к вычислительной Tf-хннке и может быть использовано при разработке быстродействующих устройств деления чисел с контролен по четности.

Целью изобретения является повышение достоверности формируемых в устройстве результатов.

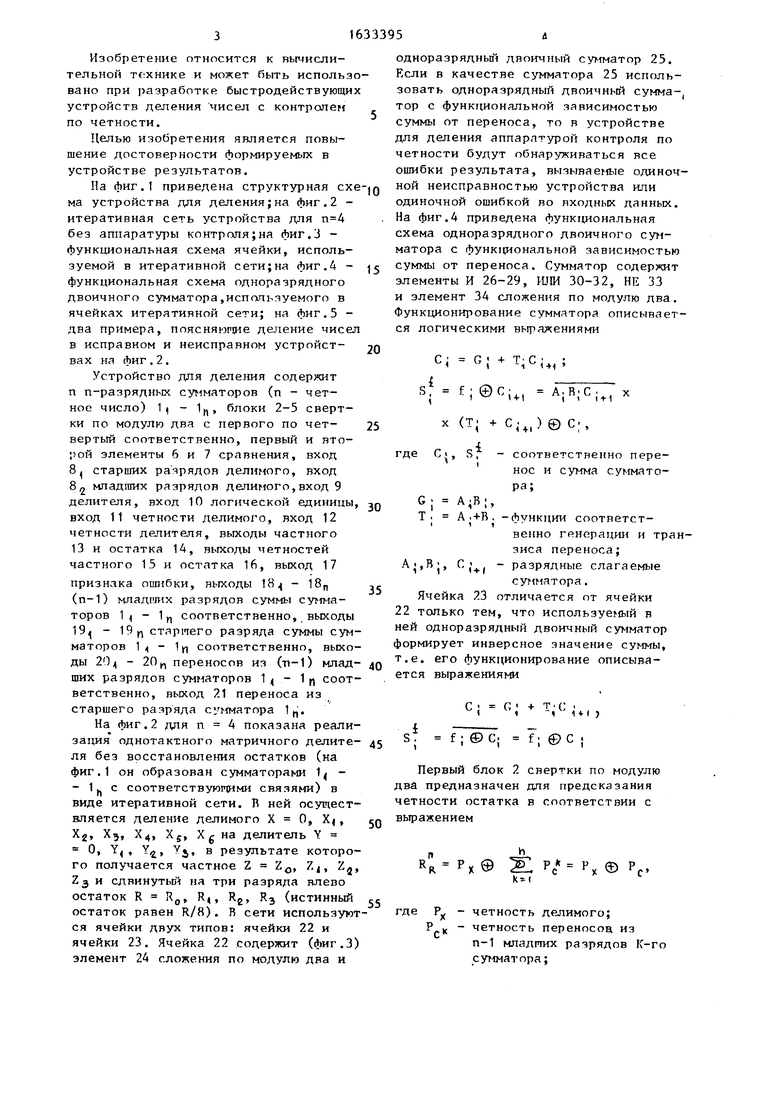

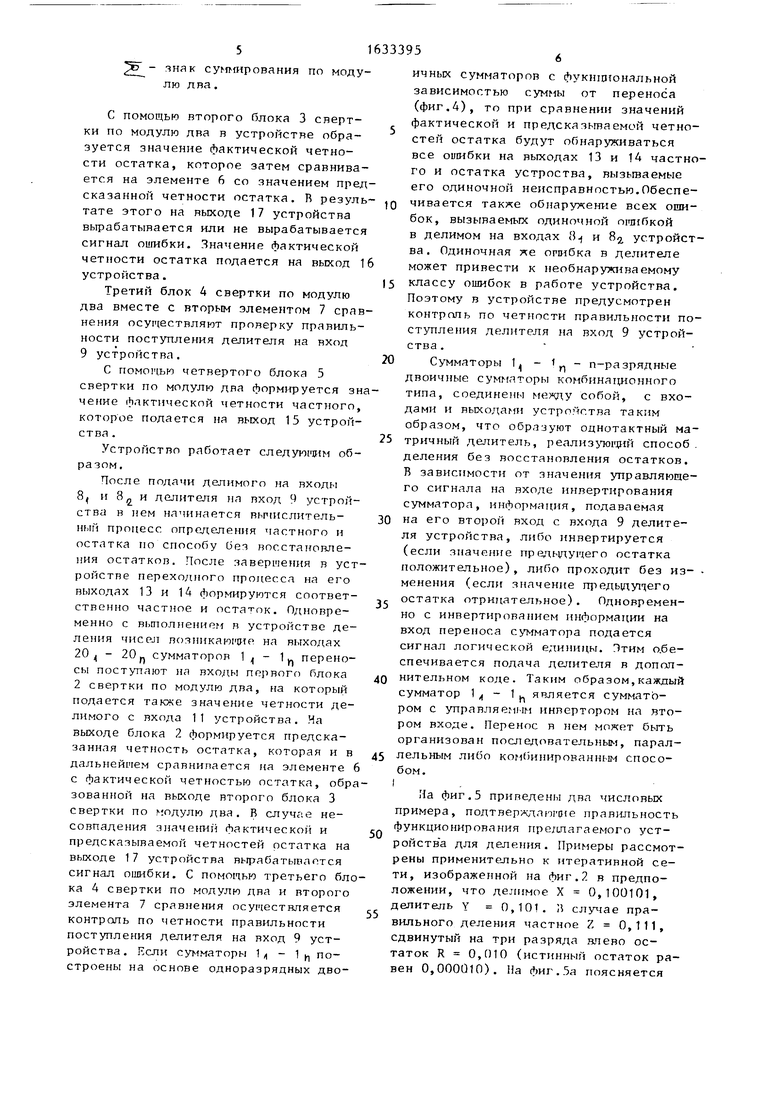

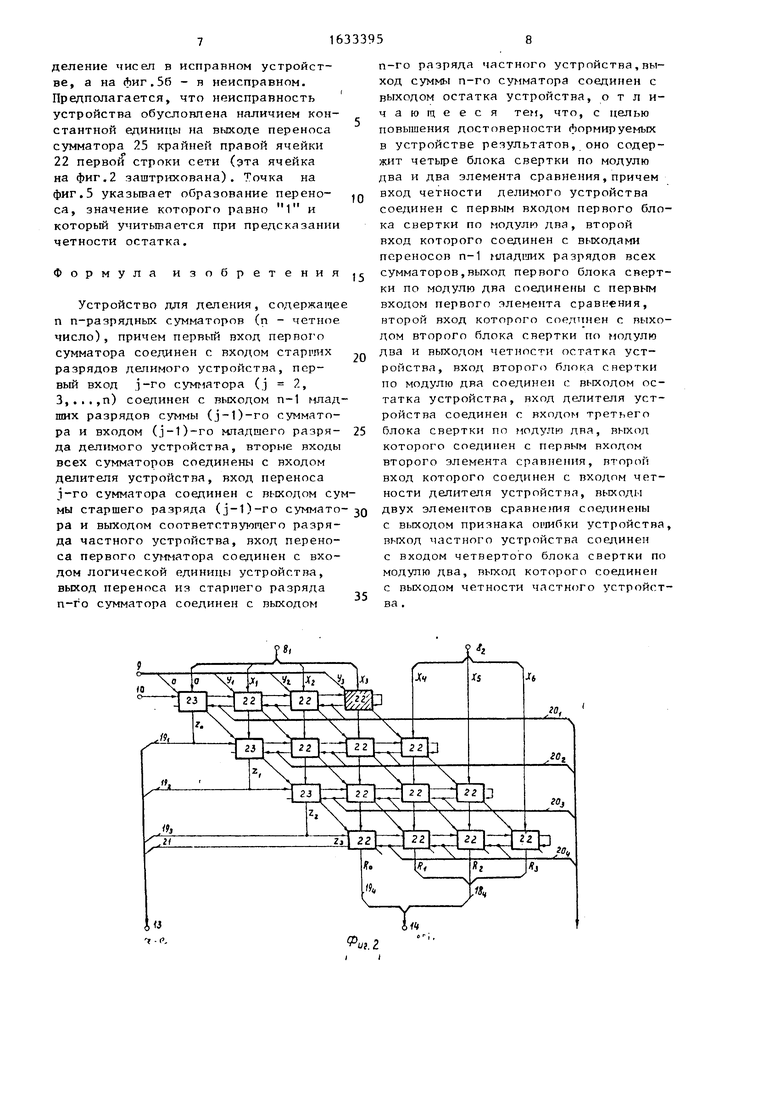

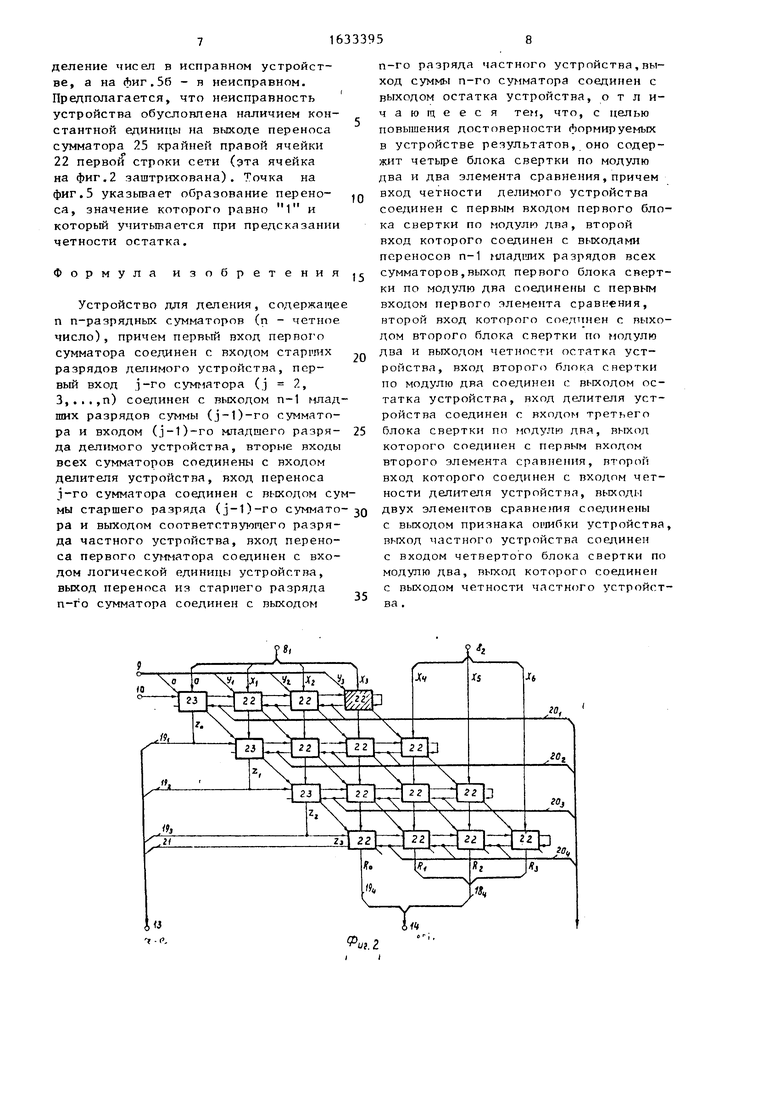

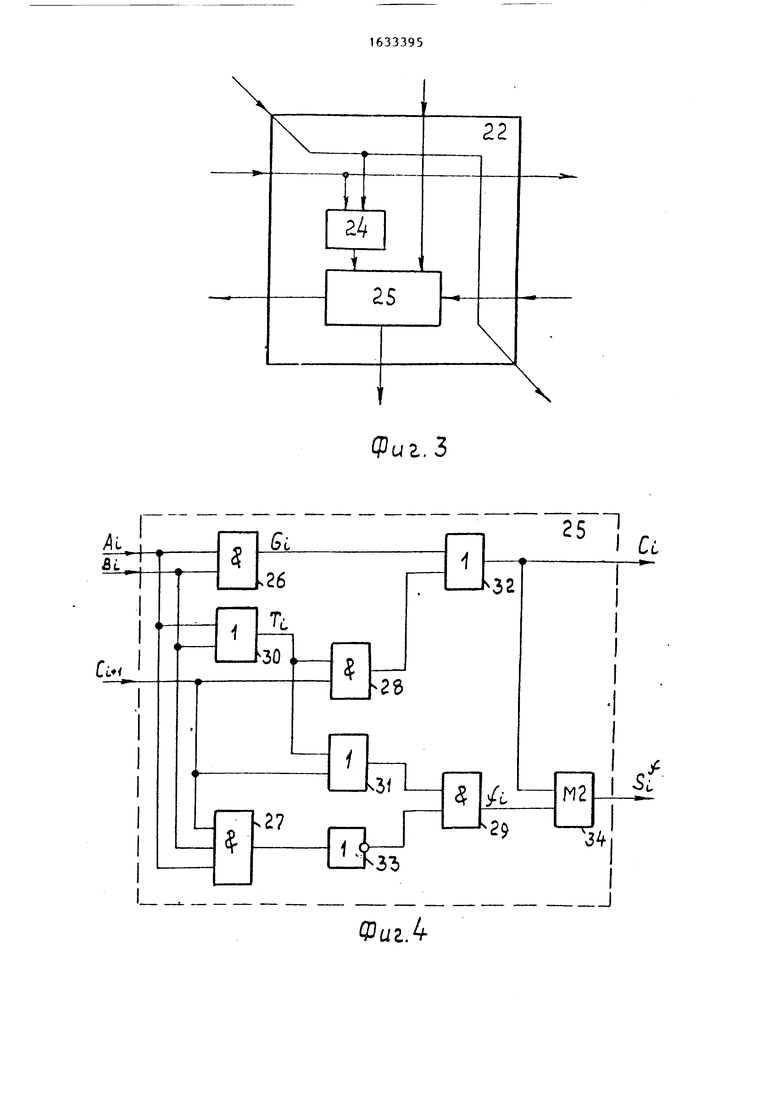

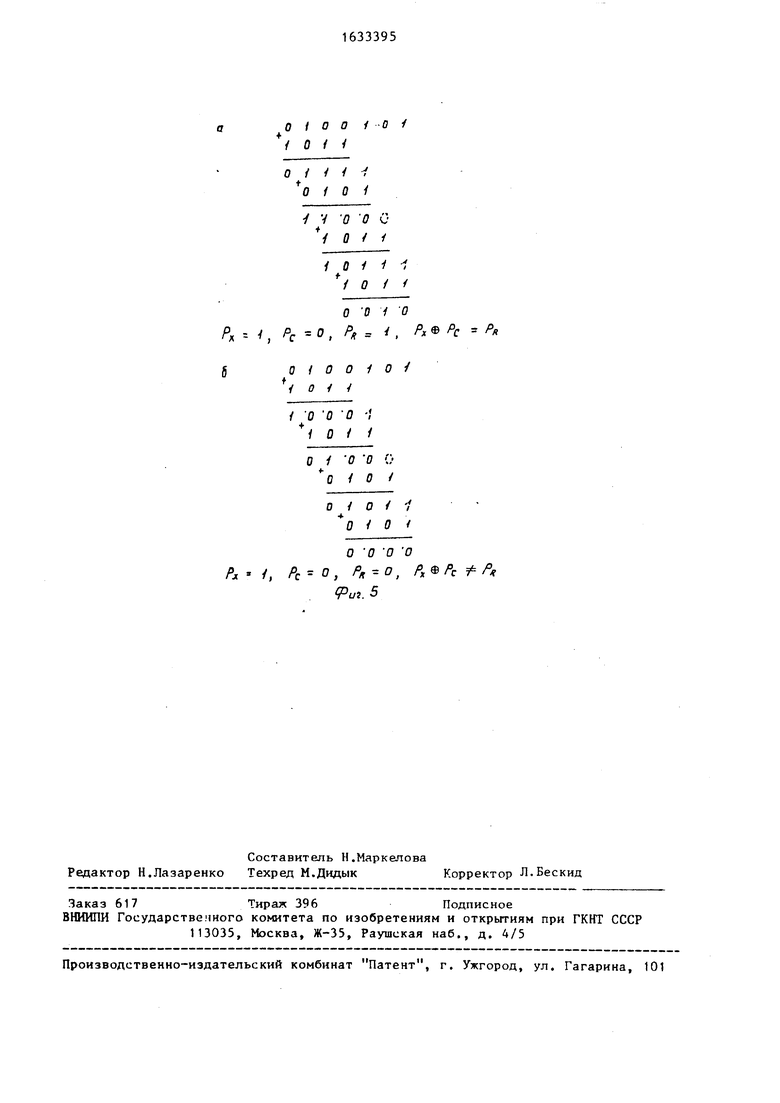

На фиг. 1 приведена структурная cxe ма устройства для деления;на фиг.2 - итеративная сеть устройства для без аппаратуры контроля;на фиг.З - функциональная схема ячейки, используемой в итеративной сети;на фиг.4 - функциональная схема одноразрядного двоичного сумматора.используемого в ячейках итеративной сети; на фиг.З - два примера, поясняюгдее деление чисел в исправном и неисправном устройст- вах на фиг.2.

Устройство для деления содержит п n-разрядных сумматоров (п - четное число) 1 - 1П, блоки 2-5 свертки по модулю два с первого по чет- вертый соответственно, первый и второй элементы 6 и 7 сравнения, вход 8 старших разрядов делимого, вход 8„ младших разрядов делимого,вход 9 делителя, вход 10 логической единицы, вход 11 четности делимого, вход 12 четности делителя, выходы частного 13 и остатка 14, выходы четностей частного 15 и остатка 16, выход 17 признака ошибки, выходы 18 - 18П (п-1) младших разрядов суммы сумматоров 1 - 1П соответственно, выходы № 1е П старпего разряда суммы сумматоров 1 4 - 1ц соответственно, выходы 204 - 20 п переносов из (п-1) млад- ших разрядов сумматоров 1 - 1 ц соответственно, выход 21 переноса из старшего разряда сумматора 1.

На фиг.2 для п 4 показана реализация однотактного матричного делите- ля без восстановления остатков (на фиг.1 он образован сумматорами 1 - - 1 с соответствующими связями) в виде итеративной сети. В ней осуществляется деление делимого X О, Х, Х2, Х, Х4, Xs, X f на делитель Y О, Y, YЈ, в результате которого получается частное Z Zo, 7.j, Z, Z и сдвинутый на три разряда влево остаток R R0, R4, Re, R3 (истинный остаток равен R/8). В сети используются ячейки двух типов: ячейки 22 и ячейки 23. Ячейка 22 содержит (фиг.З) элемент 24 сложения по модулю два и

одноразрядный двоичный сумматор 25. Если в качестве сумматора 25 использовать одноразрядный двоичный сумма-( тор с функциональной зависимостью суммы от переноса, то в устройстве для деления аппаратурой контроля по четности будут обнаруживаться все ошибки результата, вызываемые одиночной неисправностью устройства или одиночной ошибкой во входных данных. На фиг.4 приведена функциональная схема одноразрядного двоичного сумматора с функциональной зависимостью суммы от переноса. Сумматор содержит элементы И 26-29, ИЛИ 30-32, НЕ 33 и элемент 34 сложения по модулю два. Функционирование сумматора описывается логическими выражениями

нос и сумма сумматора;

где

: А.В

А,В;,

А .+В . -функции соответственно генерации и тран- зиса переноса; С( +1 разрядные слагаемые

сумматора.

Ячейка 23 отличается от ячейки 22 только тем, что используемый в ней одноразрядный двоичный сумматор формирует инверсное значение суммы, т.е. его функционирование описывается выражениями

G;

Т с

Ч 14-1)

f J © С; f; ©С

Первый блок 2 свертки по модулю два предназначен для предсказания четности остатка в соответствии с выражением

h

Ж.

рс

где Р - четность делимого;

Р к - четность переносов, из

п-1 младпих разрядов К-го сумматора;

- знак суммирования по модулю два.

С помощью второго блока 3 свертки по модулю два в устройстве образуется значение фактической четности остатка, которое затем сравнивается на элементе 6 со значением предсказанной четности остатка. R результате этого на выходе 17 устройства вырабатывается или не вырабатывается сигнал ошибки. Значение фактической четности остатка подается на выход 1 устройства.

Третий блок 4 свертки по модулю два вместе с вторым элементом 7 сравнения осуществляют проверку правильности поступления делителя на вход 9 устройства.

С помощью четвертого блока 5 свертки по модулю два формируется знчение фактической четности частного, которое подается на выход 15 устройства .

Устройство работает следующим образом.

После подачи делимого на входы 8, и 8Ј и делителя на вход Ч устройства в нем начинается вьпислитель- ным процесс определения частного и остатка по способу без восстановления остатков. После завершения в устройстве переходного процесса на его выходах 13 и 14 формируются соответственно частное и остаток. Одновременно с выполнением в устройстве деления чисел возникающей на выходах 20 ,, - 20 сумматоров 1 ц - 1 переносы поступают на входы первого блока 2 свертки по модулю два, на который подается также значение четности делимого с входа 11 устройства. На выходе блока 2 формируется предсказанная четность остатка, которая и в дальнейшем сравнипается па элементе 6 с фактической четностью остатка, образованной на выходе второго блока 3 свертки по модулю два. В случае несовпадения значений фактической и предсказываемой четностей остатка на выходе 17 устройства вырабатывается сигнал ошибки. С помощью третьего блока 4 свертки по модулю два и второго элемента 7 сравнения осуществляется контроль по четности правильности поступления делителя на вход 9 устройства. Если сумматоры 1,1 - 1 построены на основе одноразрядных дво

0

ичных сумматоров с функциональной зависимостью суммы от переноса (фиг.4), то при сравнении значений фактической и предсказываемой четностей остатка будут обнаруживаться все ошибки на выходах 13 и 14 частного и остатка устроства, вызываемые его одиночной неисправностью.Обеспеg чивается также обнаружение всех ошибок, вызываемых одиночной ошибкой в делимом на входах Ц и 8 устройства . Одиночная же ошибка в делителе может привести к необнаруживаемому

5 классу ошибок в работе устройства. Поэтому в устройстве предусмотрен контроль по четности правильности поступления делителя на вход 9 устройства ,

Сумматоры 1 ,| - 1 - п-разрядные двоичные сумматоры комбинационного типа, соединены между собой, с входами и выходами устройства таким образом, что образуют однотактный ма5 тричный делитель, реализующий способ деления без восстановления остатков. В зависимости от значения управляющего сигнала на входе инвертирования сумматора, информация, подаваемая

0 на его второй вход с входа 9 делителя устройства, либо инвертируется (если значение предьщущего остатка положительное), либо проходит без из- - менения (если значение предыдущего остатка отрицательное). Одновременно с инвертированием информации на вход переноса сумматора подается сигнал логической единицы. Г)тим обеспечивается подача делителя в допол0 нительном коде. Таким образом,каждый сумматор 1 ,( - 1 является сумматором с управляемым инвертором на втором входе. Перенос в нем может быть организован последовательным, парал5 лельным либо комбинированным способом.

5

0

5

I

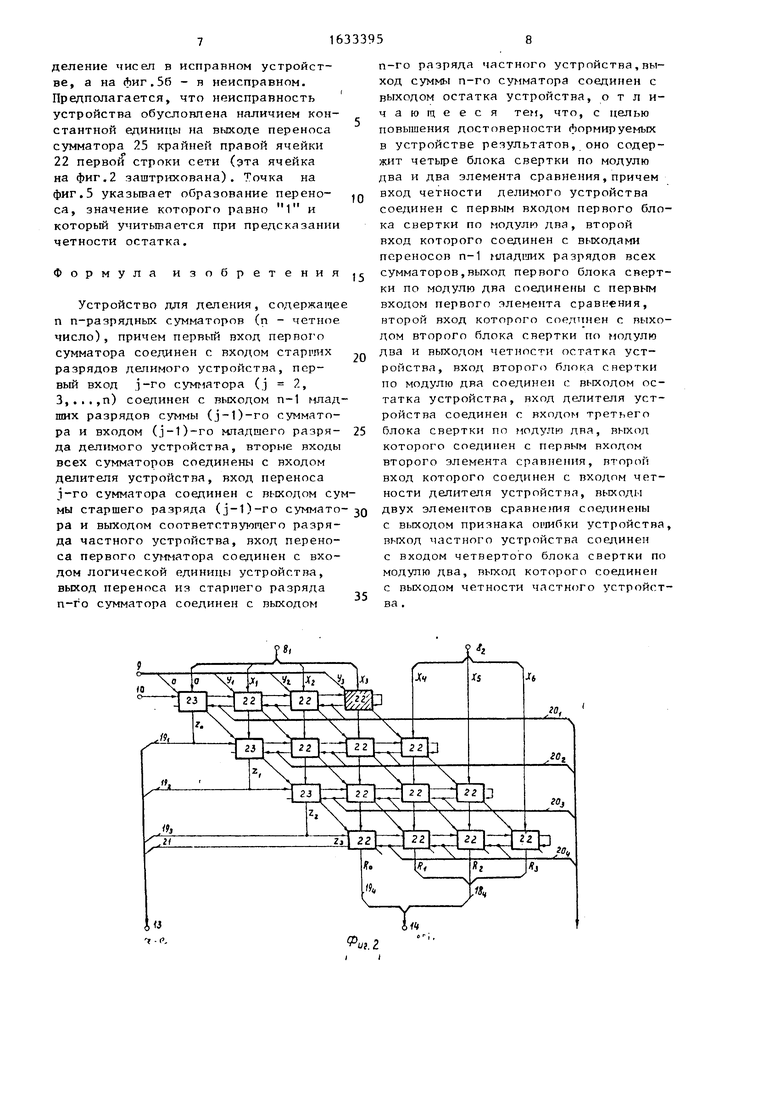

Па фиг.5 приведены два числовых

примера, подтверждающие правильность функционирования предлагаемого устройства для деления. Примеры рассмотрены применительно к итеративной сети, изображенной на фиг.2 в предположении, что делимое X 0,100101, делитель Y 0,101. 1 случае правильного деления частное Z 0,111, сдвинутый на три разряда влево остаток R 0,010 (истинный остаток равен 0,000010). На фиг.5а поясняется

деление чисел в исправном устройстве, а на Лиг. 56 - в неисправном. Предполагается, что неисправность устройства обусловлена наличием константной единицы на выходе переноса сумматора 25 крайней правой ячейки 22 первой строки сети (эта ячейка на фиг.2 заштрихована). Точка на фиг.5 указывает образование переноса, значение которого равно 1 и который учитывается при предсказании четности остатка.

Формула изобретения

Устройство для деления, содержащее п n-разрядных сумматоров (п - четное число), причем первый вход первого сумматора соединен с входом старших разрядов делимого устройства, первый вход j-ro сумматора (j 2, 3,...,п) соединен с выходом п-1 младших разрядов суммы (j-l)-ro сумматора и входом (j-l)-ro младшего разряда делимого устройства, вторые входы всех сумматоров соединены с входом делителя устройства, вход переноса j-ro сумматора соединен с выходом суммы старшего разряда (j-1)-ro суммато- ра и выходом соответствующего разряда частного устройства, вход переноса первого сумматора соединен с входом логической единицы устройства, выход переноса из старшего разряда п-г о сумматора соединен с выходом

5

n-го разряда частного устройства,выход суммы n-го сумматора соединен с выходом остатка устройства, отличающееся тем, что, с целью повышения достоверности формируемых в устройстве результатов, оно содержит четыре блока свертки по модулю два и два элемента сравнения,причем вход четности делимого устройства соединен с первым входом первого блока свертки по модулю два, второй вход которого соединен с выходами переносов п-1 младших разрядов всех сумматоров,выход первого блока свертки по модулю два соединены с первым входом первого элемента сравнения, второй вход которого соединен с выходом второго блока свертки по модулю два и выходом четности остатка устройства, вход второго блока снертки по модулю два соединен с выходом остатка устройства, вход делителя устройства соединен с входом третьего блока свертки по модули два, выход которого соединен с первым входом второго элемента сравнения, второй вход которого соединен с входом четности делителя устройства, выходы двух элементов сравнения соединены с выходом признака ошибки устройства, вьгход частного устройства соединен с входом четвертого блока свертки по модулю два, выход которого соединен с выходом четности частного устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1721603A1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

| Устройство для деления | 1989 |

|

SU1667077A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Асинхронное матричное устройство для деления | 1982 |

|

SU1022157A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств деления чисел с контролем по четности. Целью изобретения является повышение достоверности формулируемых в устройстве результатов. Устройство содержит п n-разрядных сумматоров 1 х-п (п - четное число), а также нововведенные четыре блока 2-5 свертки по модулю два и дпа элемента 6 и 7 сравнения. 5 ил.

56eee9i

о I о а 1 о 1 + / О i /

о / У//

fo /о1

I У О О О

/0/ 1

1 0 11 ,

1 01

О 0i О

1 , РС ° , Л ® Р

0 / О О 1 0 / % и / /

/ 0 0 0 /

+ У 0//

О 1 О О

о/о

«

010

о о

О О О О

Л /, Рс- о, , Яф/9с

f иг. 5

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| -М.: Наука, 1969, с.494, рис.5.1 | |||

| Dean K.I | |||

| Cellular arrays for binary division - Proceedings.of che institution of Kluctrical Engineers | |||

| May, 1970, vol | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-06—Подача