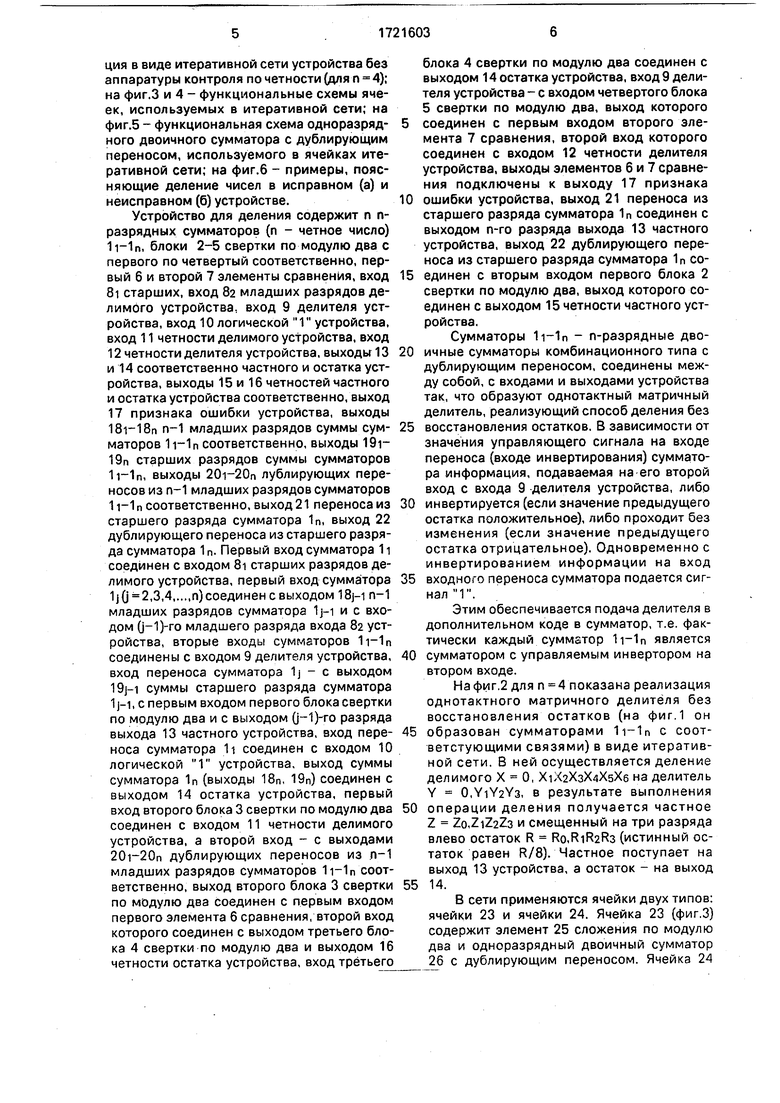

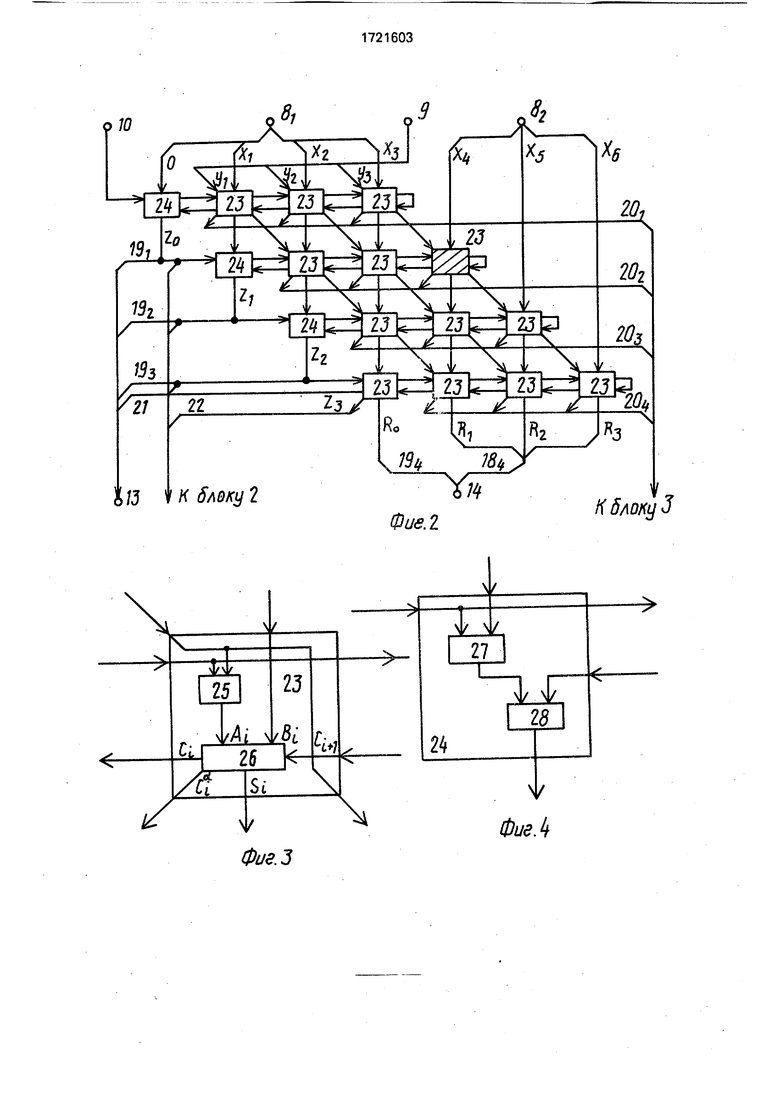

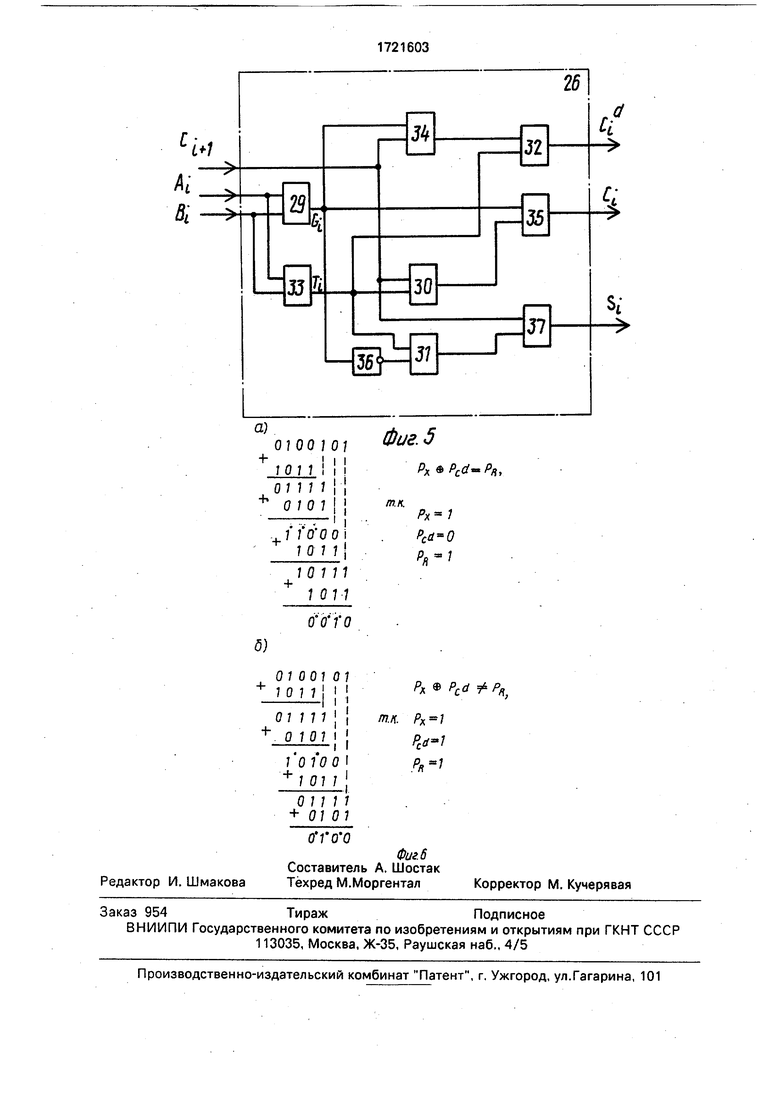

ция в виде итеративной сети устройства без аппаратуры контроля по четности (для п 4); на фиг.З и 4 - функциональные схемы ячеек, используемых в итеративной сети; на фиг.5 - функциональная схема одноразрядного двоичного сумматора с дублирующим переносом, используемого в ячейках итеративной сети; на фиг.6 - примеры, поясняющие деление чисел в исправном (а) и неисправном (б) устройстве.

Устройство для деления содержит п п- разрядных сумматоров (п - четное число) , блоки 2-5 свертки по модулю два с первого по четвертый соответственно, первый 6 и второй 7 элементы сравнения, вход 8i старших, вход 82 младших разрядов делимого устройства, вход 9 делителя устройства, вход 10 логической 1 устройства, вход 11 четности делимого устройства, вход 12 четности делителя устройства, выходы 13 и 14 соответственно частного и остатка устройства, выходы 15 и 16 четностей частного и остатка устройства соответственно, выход 17 признака ошибки устройства, выходы n-1 младших разрядов суммы сумматоров 1t-1n соответственно, выходы 19i- 19П старших разрядов суммы сумматоров 1i-1n, выходы лублирующих переносов из п-1 младших разрядов сумматоров 11-1 п соответственно, выход 21 переноса из старшего разряда сумматора 1П, выход 22 дублирующего переноса из старшего разряда сумматора 1 п. Первый вход сумматора 11 соединен с входом 8t старших разрядов делимого устройства, первый вход сумматора

1j(,3,4п)соединен с выходом 18j-i n-1

младших разрядов сумматора 1j-i и с входом (j-1)-ro младшего разряда входа 82 устройства, вторые входы сумматоров 1i-1n соединены с входом 9 делителя устройства, вход переноса сумматора 1j - с выходом 19j-i суммы старшего разряда сумматора 1 j-1, с первым входом первого блока свертки по модулю два и с выходом (j-1)-ro разряда выхода 13 частного устройства, вход переноса сумматора 1ч соединен с входом 10 логической 1 устройства, выход суммы сумматора 1П (выходы 18п, 19п) соединен с выходом 14 остатка устройства, первый вход второго блока 3 свертки по модулю два соединен с входом 11 четности делимого устройства, а второй вход - с выходами 20i-20n дублирующих переносов из л-1 младших разрядов сумматоров 1i-1n соответственно, выход второго блока 3 свертки по модулю два соединен с первым входом первого элемента 6 сравнения/второй вход которого соединен с выходом третьего блока 4 свертки по модулю два и выходом 16 четности остатка устройства, вход третьего

блока 4 свертки по модулю два соединен с выходом 14 остатка устройства, вход 9 делителя устройства- с входом четвертого блока 5 свертки по модулю два, выход которого

соединен с первым входом второго элемента 7 сравнения, второй вход которого соединен с входом 12 четности делителя устройства, выходы элементов 6 и 7 сравнения подключены к выходу 17 признака

0 ошибки устройства, выход 21 переноса из старшего разряда сумматора 1 п соединен с выходом n-го разряда выхода 13 частного устройства, выход 22 дублирующего переноса из старшего разряда сумматора 1п со5 единен с вторым входом первого блока 2 свертки по модулю два, выход которого соединен с выходом 15 четности частного устройства.

Сумматоры - n-разрядные дво0 ичные сумматоры комбинационного типа с дублирующим переносом, соединены между собой, с входами и выходами устройства так, что образуют однотактный матричный делитель, реализующий способ деления без

5 восстановления остатков. В зависимости от значения управляющего сигнала на входе переноса (входе инвертирования) сумматора информация, подаваемая на его второй вход с входа 9 делителя устройства, либо

0 инвертируется (если значение предыдущего остатка положительное), либо проходит без изменения (если значение предыдущего остатка отрицательное). Одновременно с инвертированием информации на вход

5 входного переноса сумматора подается сигнал 1.

Этим обеспечивается подача делителя в дополнительном коде в сумматор, т.е. фактически каждый сумматор является

0 сумматором с управляемым инвертором на втором входе.

На фиг.2 для п 4 показана реализация однотактного матричного делителя без восстановления остатков (на фиг.1 он

5 образован сумматорами 1i-1n с соот- ветстующими связями) в виде итеративной сети. В ней осуществляется деление делимого X О, X1X2X3X4X5X5 на делитель Y 0,YiY2Y3, в результате выполнения

0 операции деления получается частное Z Zo,ZiZ2Zs и смещенный на три разряда влево остаток R Ro,RiR2R3 (истинный остаток равен R/8). Частное поступает на выход 13 устройства, а остаток - на выход

5 14.

В сети применяются ячейки двух типов: ячейки 23 и ячейки 24. Ячейка 23 (фиг.З) содержит элемент 25 сложения по модулю два и одноразрядный двоичный сумматор 26 с дублирующим переносом. Ячейка 24

(фиг.4) содержит элемент 27 сложения по модулю два и элемент 28 сложения по модулю два с инверсным выходом.

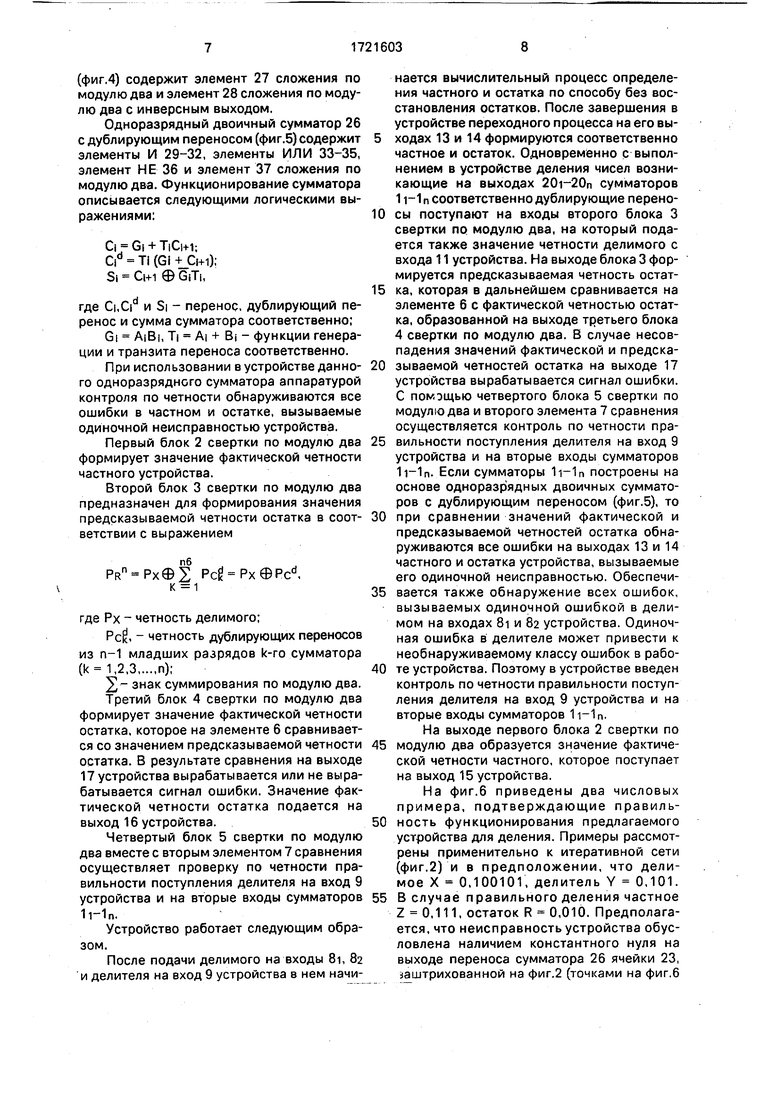

Одноразрядный двоичный сумматор 26 с дублирующим переносом (фиг.5) содержит элементы И 29-32, элементы ИЛИ 33-35, элемент НЕ 36 и элемент 37 сложения по модулю два. Функционирование сумматора описывается следующими логическими выражениями:

Ci - Gi + TiCi+1; Cid Ti (Gi ); Si Ci+1 0 GiTi,

где Ci,Cid и Si - перенос, дублирующий перенос и сумма сумматора соответственно;

Gi AiBi, TI Ai + Bj - функции генерации и транзита переноса соответственно.

При использовании в устройстве данного одноразрядного сумматора аппаратурой контроля по четности обнаруживаются все ошибки в частном и остатке, вызываемые одиночной неисправностью устройства.

Первый блок 2 свертки по модулю два формирует значение фактической четности частного устройства.

Второй блок 3 свертки по модулю два предназначен для формирования значения предсказываемой четности остатка в соответствии с выражением

пб

Рвп РхФЕ PcK Px®Pcd,

К 1

где Рх четность делимого;

Рс, - четность дублирующих переносов из п-1 младших разрядов k-ro сумматора (k 1,2,3п);

2 знак суммирования по модулю два.

Третий блок 4 свертки по модулю два формирует значение фактической четности остатка, которое на элементе 6 сравнивается со значением предсказываемой четности остатка. В результате сравнения на выходе 17 устройства вырабатывается или не вырабатывается сигнал ошибки. Значение фактической четности остатка подается на выход 16 устройства.

Четвертый блок 5 свертки по модулю два вместе с вторым элементом 7 сравнения осуществляет проверку по четности правильности поступления делителя на вход 9 устройства и на вторые входы сумматоров

11-1 л.

Устройство работает следующим образом.

После подачи делимого на входы 8i, 82 и делителя на вход 9 устройства в нем начинается вычислительный процесс определения частного и остатка по способу без восстановления остатков. После завершения в устройстве переходного процесса на его выходах 13 и 14 формируются соответственно частное и остаток. Одновременно с выполнением в устройстве деления чисел возникающие на выходах 20i-20n сумматоров 11-1 п соответственно дублирующие перено0 сы поступают на входы второго блока 3 свертки по модулю два, на который подается также значение четности делимого с входа 11 устройства. На выходе блока 3 формируется предсказываемая четность остат5 ка, которая в дальнейшем сравнивается на элементе 6 с фактической четностью остатка, образованной на выходе третьего блока 4 свертки по модулю два. В случае несовпадения значений фактической и предска0 зываемой четностей остатка на выходе 17 устройства вырабатывается сигнал ошибки. С помэщью четвертого блока 5 свертки по модулю два и второго элемента 7 сравнения осуществляется контроль по четности пра5 вильности поступления делителя на вход 9 устройства и на вторые входы сумматоров 1i-1n. Если сумматоры 1i-1n построены на основе одноразрядных двоичных сумматоров с дублирующим переносом (фиг.5), то

0 при сравнении значений фактической и предсказываемой четностей остатка обнаруживаются все ошибки на выходах 13 и 14 частного и остатка устройства, вызываемые его одиночной неисправностью. Обеспечи5 вается также обнаружение всех ошибок, вызываемых одиночной ошибкой в делимом на входах 8i и 82 устройства. Одиночная ошибка в делителе может привести к необнаруживаемому классу ошибок в рабо0 те устройства. Поэтому в устройстве введен контроль по четности правильности поступления делителя на вход 9 устройства и на вторые входы сумматоров 1 i-1n.

На выходе первого блока 2 свертки по

5 модулю два образуется значение фактической четности частного, которое поступает на выход 15 устройства.

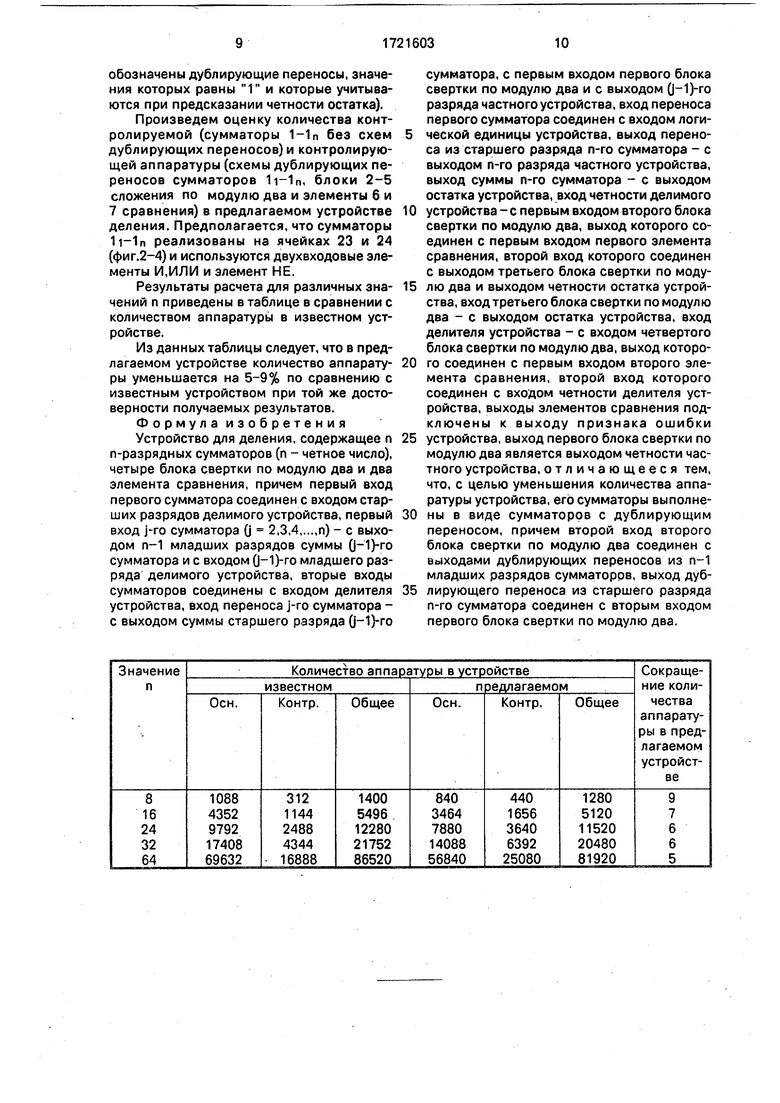

На фиг.6 приведены два числовых примера, подтверждающие правиль0 ность функционирования предлагаемого устройства для деления. Примеры рассмотрены применительно к итеративной сети (фиг.2) и в предположении, что делимое X 0,100101, делитель Y 0,101.

5 В случае правильного деления частное Z 0,111, остаток R 0,010. Предполагается, что неисправность устройства обусловлена наличием константного нуля на выходе переноса сумматора 26 ячейки 23, заштрихованной на фиг.2 (точками на фиг.6

обозначены дублирующие переносы, значения которых равны 1 и которые учитываются п ри п ре дс каза н и и четности остатка).

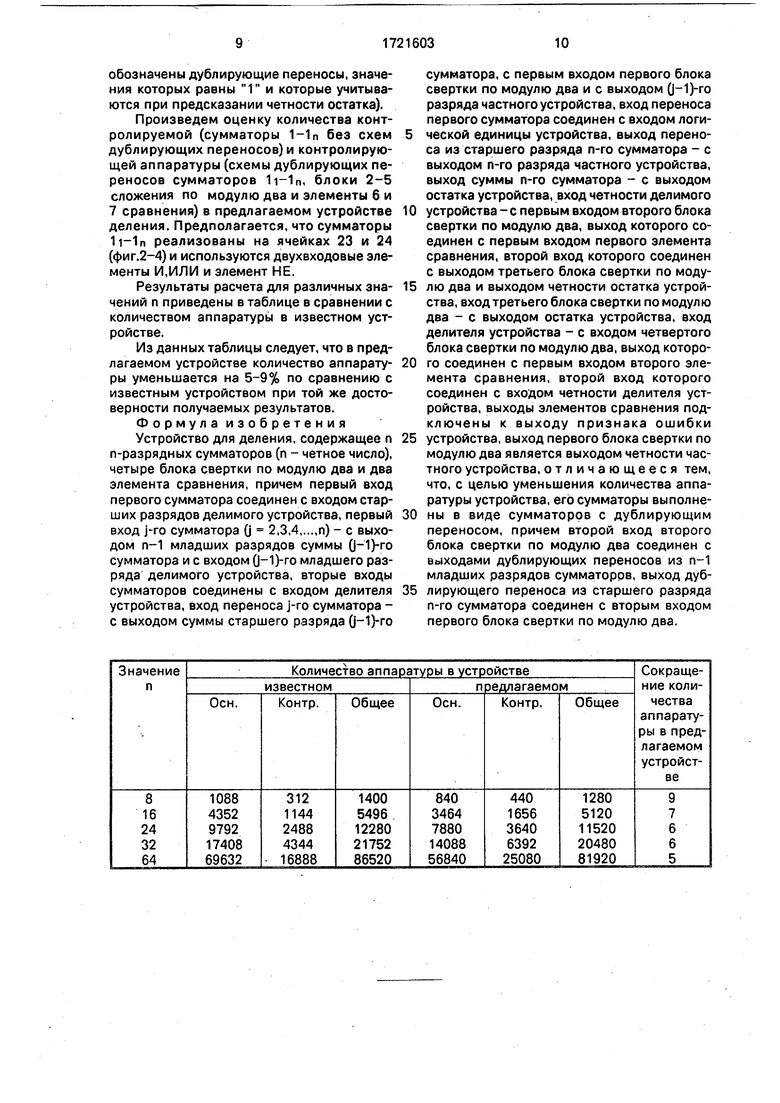

Произведем оценку количества контролируемой (сумматоры 1-1 п без схем дублирующих переносов) и контролирующей аппаратуры (схемы дублирующих переносов сумматоров 1i-1n, блоки 2-5 сложения по модулю два и элементы 6 и 7 сравнения) в предлагаемом устройстве деления. Предполагается, что сумматоры реализованы на ячейках 23 и 24 (фиг.2-4) и используются двухвходовые элементы И,ИЛИ и элемент НЕ.

Результаты расчета для различных зна- чений п приведены в таблице в сравнении с количеством аппаратуры в известном устройстве.

Из данных таблицы следует, что в предлагаемом устройстве количество аппарату- ры уменьшается на 5-9% по сравнению с известным устройством при той же достоверности получаемых результатов.

Ф о р м у л а и з о б р е т е н и я

Устройство для деления, содержащее п n-разрядных сумматоров (п - четное число), четыре блока свертки по модулю два и два элемента сравнения, причем первый вход первого сумматора соединен с входом старших разрядов делимого устройства, первый вход j-ro сумматора (j 2,3,4п) - с выходом п-1 младших разрядов суммы (j-1)-ro сумматора и с входом (j-1)-ro младшего разряда делимого устройства, вторые входы сумматоров соединены с входом делителя устройства, вход переноса j-ro сумматора - с выходом суммы старшего разряда (j-1)-ro

сумматора, с первым входом первого блока свертки по модулю два и с выходом (|-1)-го разряда частного устройства, вход переноса первого сумматора соединен с входом логической единицы устройства, выход переноса из старшего разряда n-го сумматора - с выходом п-го разряда частного устройства, выход суммы n-го сумматора - с выходом остатка устройства, вход четности делимого устройства - с первым входом второго блока свертки по модулю два, выход которого соединен с первым входом первого элемента сравнения, второй вход которого соединен с выходом третьего блока свертки по модулю два и выходом четности остатка устройства, вход третьего блока свертки по модулю два - с выходом остатка устройства, вход делителя устройства - с входом четвертого блока свертки по модулю два, выход которого соединен с первым входом второго элемента сравнения, второй вход которого соединен с входом четности делителя устройства, выходы элементов сравнения под- ключены к выходу признака ошибки устройства, выход первого блока свертки по модулю два является выходом четности частного устройства,отличающееся тем, что, с целью уменьшения количества аппаратуры устройства, его сумматоры выполнены в виде сумматоров с дублирующим переносом, причем второй вход второго блока свертки по модулю два соединен с выходами дублирующих переносов из п-1 младших разрядов сумматоров, выход дублирующего переноса из старшего разряда n-го сумматора соединен с вторым входом первого блока свертки по модулю два.

Фие.2

КблйкуЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1991 |

|

SU1784974A1 |

| Устройство для деления | 1989 |

|

SU1667077A1 |

| Устройство для деления | 1989 |

|

SU1633395A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Асинхронное матричное устройство для деления | 1982 |

|

SU1022157A1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Устройство для деления п-разрядных двоично-десятичных чисел | 1982 |

|

SU1026139A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

Авторы

Даты

1992-03-23—Публикация

1990-04-09—Подача