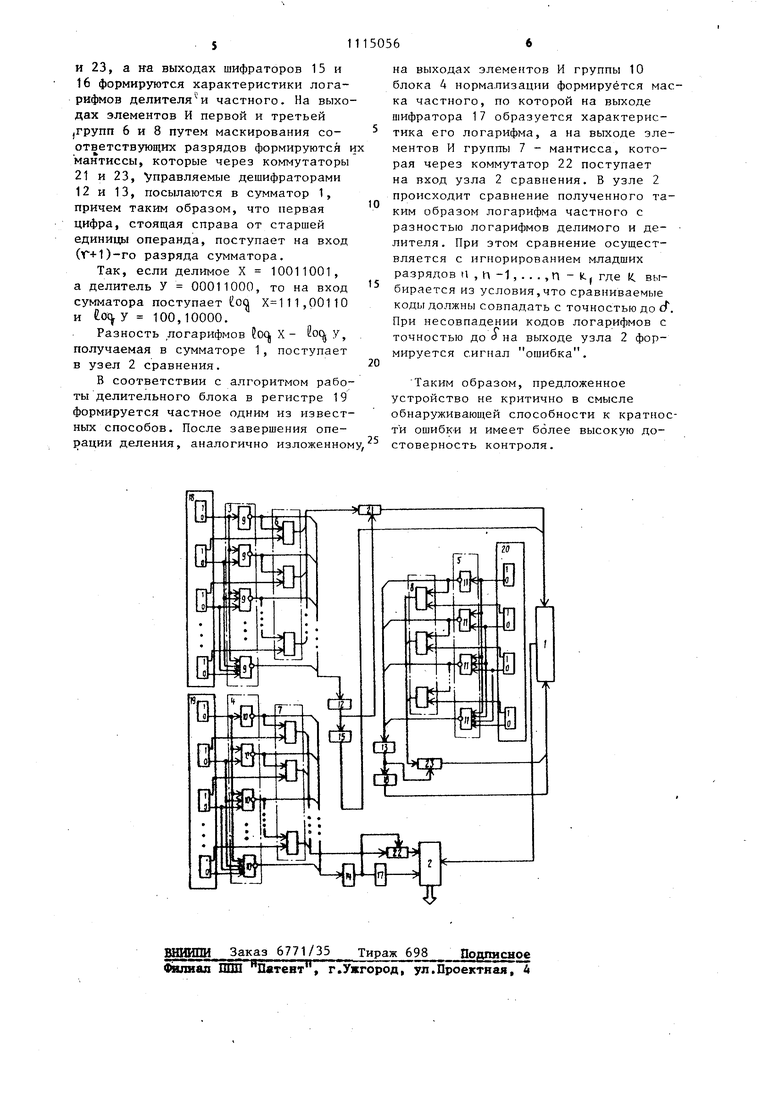

Изобретение относится к вычислительной технике и может быть использовано при постррении арифметических блоков отказоустойчивых ЦВМ. Известно устройство для обнаружения ошибок, содержащее узел сравнения, узлы свертки по модулю d и сумматоры по модулю dCll Недостатками устройства являются сложность, невысокая обнаруживающая способность, а также большое время, затрачиваемое на контроль операции деления, Наиболее близким к изобретению по технической сущности является ус ройство для контроля сумматора с по мощью остаточного кода, содержащее три блока формирования остатка по м дулю гп, сумматор остатков и схему сравнения, причем входы первого, второго и третьего блоков формирова ния остатков по модулюmсоединены соответственно с выходами регистров первого и второго слагаемых и регис ра суммы, выходы первого и второго блоков формирования остатков по модулю m соединены соответственно с первым и вторым входами сумматора остатков, выход которого соединен с первым входом схемы сравнения, вто|рой вход которой соединен с выходом третьего блока формирования остатко по модулю т, выход схемы сравнения является выходом неисправности устройства 121. Недостатком известного устройств является низкая достоверность контроля. Цель изобретения - повьшение дос товерности контроля. Поставленная цель достигается те что в устройство для контроля делительного блока, содержащее сумматор узел сравнения, причем выходы сумматора соединены с первой группой входов узла сравнения, выход которого является выходом ошибки устройства, введены три коммутатора, три дешифратора, три шифратора, три группы элементов И, три блока норма лизации, каждый из которых содержи группу элементов И, причем -1-е входы всех к-х элементов И группы первого, второго и третьего блоков нормализации объединены и соединены с { -ми разрядами группы инверсных входов делителя, группы инверсных выходов результата и группы инверсных входов делимого контролируемого блока соответственно ( Uiin ; И , где г - разрядность регистров), выходы элементов И группы первого, второго и третьего блоков нормализации соединены с входами соответственно первого, второго и третьего де шифрагоров, выходыгг -х элементов И группы первого блока нормализации () соединены с первыми входами т-х элементов И первой группы, вторые входы которых соединены соот- . ветственно с (гп+1)-ми разрядами группы прямых входов делителя контролируемого блока, выходы т-х элементов И группы второго блока нормализацр5и соединены с первыми входами т-х элементов И второй группы, вторые входы которых соединены соответственно с (т+1)-ми разрядами группы прямых выходов результата контролируемого блока, выходы т-х элементов И группы третьего блока нормализации соединены с первыми входами т-х элементов И третьей группы, вторые входы которых соединены соответственно с (гТ(+1)-ми разрядами группы прямых входов делимого контролируемого блока, выходы элементов И первой, второй-и третьей групп соединены соответственно с информационными входами первого, второго и третьего коммутаторов, управляющий вход первого коммутатора соединен с выходом первого дешифратора и входом первого шифратора, выходы первого коммутатора и первого шифратора соединены с группой входов первого слагаемого сумматора, группа входов второго слагаемого которого соединена с выходами третьего шифратора и третьего коммутатора, управляющий вход котоiporo соединен с выходом третьего дешифратора и входом третьего шифратора, выход второго дешифратора |соединен с управляющим входом второго коммутатора и входом второго шифратора, выходы которых соединены с второй группой входов узла сравнения. На чертеже изображена функциональная схема устройства для контроля делительного блока, соединенного с регистрами контролируемого блока, являющимися входами-выходами контролируемого блока. Устройство содержит сумматор 1, узел 2 сравнения, блоки 3-5 нормализации, группы 6-8 элементов И, группы 9-11 элементов И блоков нормализации, дешифраторы 12-1 А, шифраторы 15-17, регистр 18 делителя, регистр 19 частного, регистр 20 делимого, коммутаторы 21-23,

Принцип контроля построен на основе приближенного вычисления логарифмов делимого, делителя и частного, нахождении разности логарифмов делимого и делителя с последующим сравнением ее с логарифмом частного

Приближенное вычисление логарифма числа осуществляется Простой комбинационной схемой, позволяющей обеспечить достаточную для контроля точность при незначительных временных затратах на формирование логарифма. При этом характеристика числа принимается равной количеству двоичных разрядов этого числа, расположенных справа от наибольшей значащей единицы в числе. В качестве мантиссы принимается код этого числа, расположенный справа от старшего разряда, содержащего единицу. Например, логарифм двоичного.числа Х 10011001 и X|j 00011000 соответственно равен lo X 111,001 10 и X 100,10000, где код 111 и код 100 есть характеристики чисел Х и X|j, а код ,00110 и код ,10000 мантисс X ,( и Х, соответственно.

I.

Назначение функциональных элементов предлагаемого устройства следующее.

Блоки 3-5 нормализации предназначены для поиска старших единиц в кодах чисел, содержащихся соответственно в регистрах делителя, частного и делимого. При кодах чисел делителя, делимого и частного , равных IXXXX... 01ХХ...Х, 001ХХХ...Х, 00...01Х и 00...001, на выходах блоков 3-5 формируются соответственно коды масок 1111... 11, 0111...11, 0011...11, 00...011 и 000...001, где ,0. Дешифраторы 12-14 и шифраторы 15-17 предназначены для формирования характеристик логарифмов чисел соответственно .делителя, частного и делимого по кодам, получаемым на выходах блоков 3-5, а также для управления коммутаторами. При поступлении на вход дешифратора 12,13 или 14 кода из множества {00...01, 00...011 00. ..0111, 00..., 011... 11,111... 11} на выходе возбуждается шина, управляющая коммутатором 21,22 или 23,

а на выходе шифратора 15,16 или 17 формируется характеристика числа, содержащегося на регистрах 18, 19 или 20.

Число разрядов т, отводимое для характеристики логарифма, определяется из выражения

r to(j ГА ,

где п - разрядность числа, а скобки означают округление до ближайшего большего целого.

Группы 6-8 элементов И предназначены для вьщеления мантисс логарифмов чисел, выходы групп 6 и 8 элементов И соединены с младшими П , П+1,...,Г+1,Т разрядами входов слагаемых сумматора. 1 через коммутаторы а вьп-;оды группы 1-е узлом 2 сравнения. Это обеспечивает такую коммутацию мантисс, при которой первая цифра, расположенная справа от старшей единицы, поступает в (Г+Ю-й разряд, вторая - в (Т+2)-й разряд и т.д. Старшие разряды 1,2,..., Т сумматора 1 и узла 2 сравнения соединены с выходами шифратора 15-17. Этим обеспечивается возможность нахождения разности логарифмов делимого и делителя и сравнения этой раз;Ности с логарифмом частного.

Узел 2 сравнения предназначен для сравнения кодов, осуществляемого путем выполнения операции сложения mod 2. Он может быть выполнен на триггерах со счетным входом.

Конструктивное исполнение сумматора 1, как и делительного блока, не существенно. Их конструкция может быть любой, удовлетворяющей выбранному варианту выполнения операций деления и сложения в конкретном арифметическом устройстве.

Устройство работает следующим образом.

При поступлении делителя и делимого на регистры 18 и 20 на выходах элементов И групп 9 и 11 блоков 3 и 5 нормализации по изложенным правилам формируются коды масок. Каждая из масок представляет собой код, содержащий нули в разрядах, расположенных слева от старшей единицы в коде числа, и единицы в остальных разрядах. По кодам масок на выходах дешифраторов 12 и 13 возбуждаются шины, управляющие коммутаторами 21

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕЛИТЕЛЬНОГО БЛОКА, содержащее сумматор, узел сравнения, причем выходы сумматора соединены с первой группой входов узла сравнения, выход которого является выходом ошибки устройства, отличающееся тем, что, с целью повьшения достоверности контроля, в него введены три коммутатора, три дешифратора, три шифратора, три группы элементов И, три блока нормализации, каждый из koToрых содержит группу элементов И, причем 1 -е входы всех к-х элементов И группы первого, второго и третьего блоков нормализации объединены и соединены с i-ми разрядами группы инверсных входов делителя, группы инверсных выходов результата и группы инверсных входов делимого контролируемого блока соответственно

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Журавлев Ю.П | |||

| и др | |||

| Надежность и контроль ЭВМ | |||

| М., Советское радио, 1978,с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., Мир, 1972, с | |||

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-09-23—Публикация

1983-05-13—Подача