Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для выполнения операций деления.

Цель изобретения - повышение надежд- ности устройства.

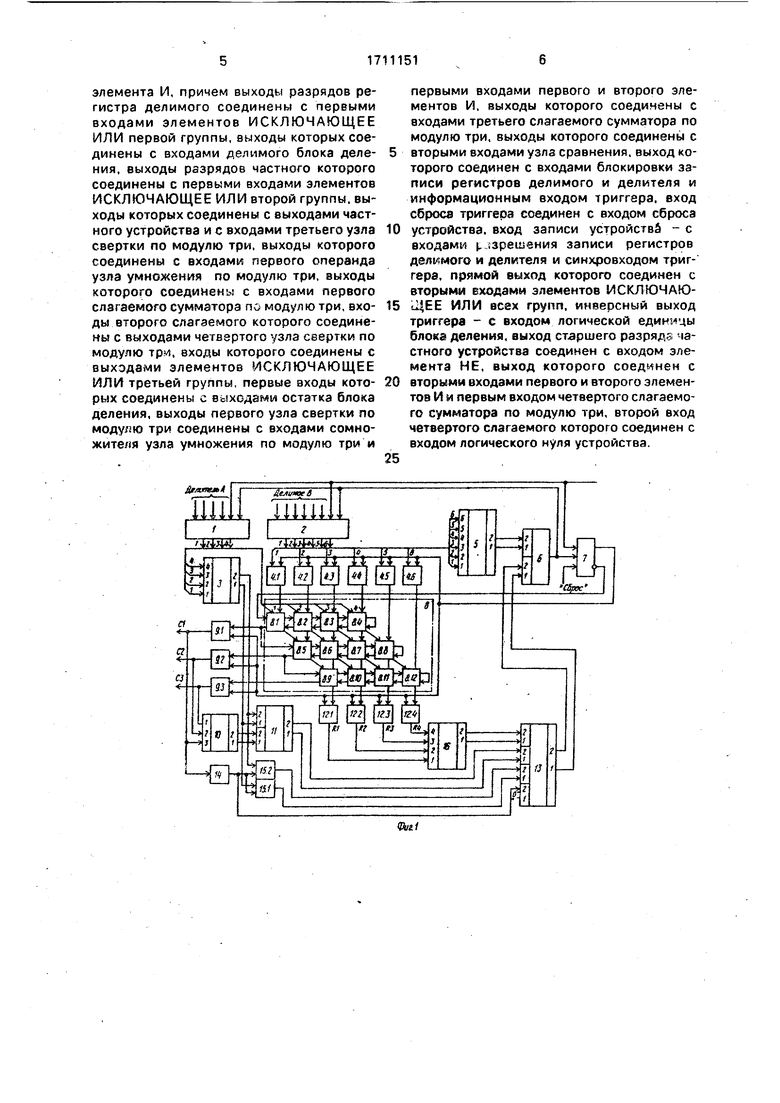

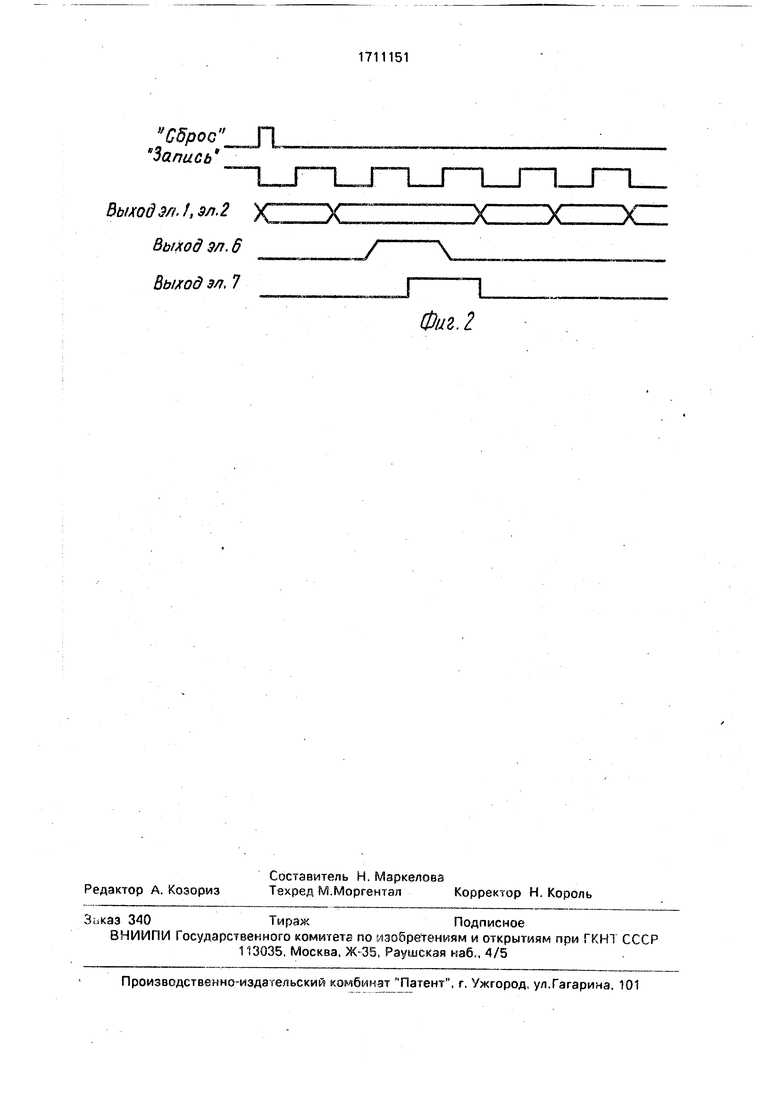

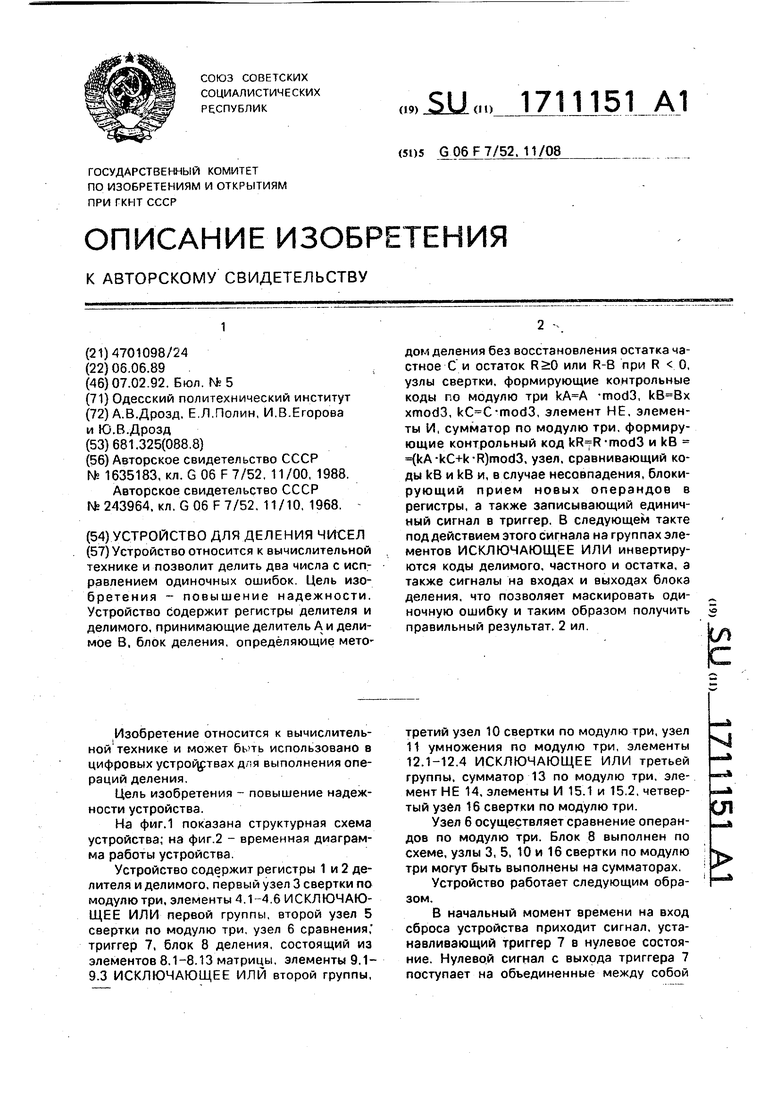

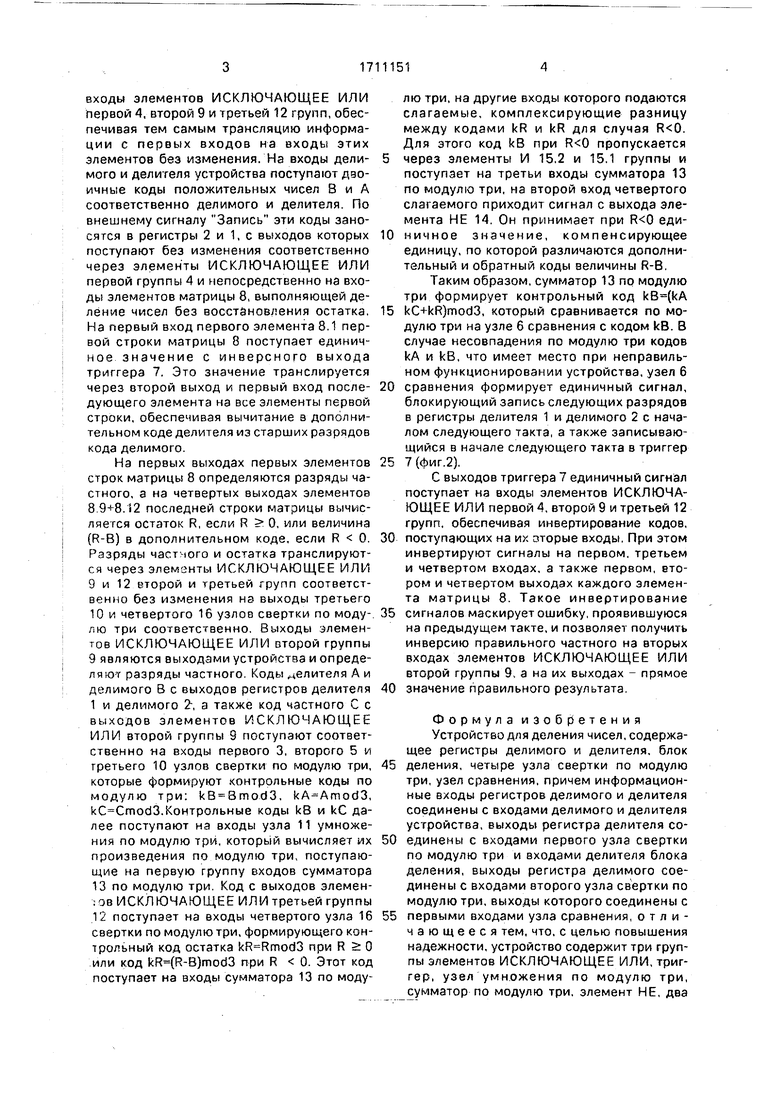

На фиг. 1 показана структурная схема устройства; на фйг.2 - временная диаграмма работы устройства.,

Устройство содержит регистры 1 и 2 делителя и делимого, первый узел 3 свертки по модулю три, элементы 4.1-4.6 ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, второй узел 5 свертки по модулю три, узел 6 сравнения; триггер 7, блок 8 деления, состоящий из элементов 8,1-8.13 матрицы, элементы 9.1- 9.3 ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы.

третий узел 10 свертки по модулю,три, узел 11 умножения по модулю три, элементы 12.1-12.4 ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы, сумматор 13 по модулю три, элемент НЕ 14, элементы И 15.1 и 15.2, четвертый узел 16 свертки по модулю три.

Узел 6 осуществляет сравнение операндов по модулю три. Блок 8 выполнен по схеме, узлы 3, 5, 10 и 16 свертки по модулю три могут быть выполнены на сумматорах.

Устройство работает следующим образом.

В начальный момент времени на вход сброса устройства приходит сигнал, устанавливающий триггер 7 в нулевое состояние. Нулевой сигнал с выхода триггера 7 поступает на объединенные между собой

№

входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой 4, второй 9 и третьей 12 групп, обеспечивая тем самым трансляцию информации с первых входов на входы этих элементов без изменения. На входы делимого и делителя устройства поступают двоичные коды положительных чисел В и А соответственно делимого и делителя. По внешнему сигналу Запись эти коды заносятся в регистры 2 и 1, с выходов которых поступают без изменения соответственно через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 4 и непосредственно на входы элементов матрицы 8, выполняющей деление чисел без восстановления остатка. На первый вход первого элемента 8.1 первой строки матрицы 8 поступает единичное значение с инверсного выхода триггера 7, Это значение транслируется через второй выход и первый вход последующего элемента на все элементы первой строки, обеспечивая вычитание в дополнительном коде делителя из старших разрядов кода делимого.

На первых выходах первых элементов строк матрицы 8 определяются разряды частного, а на четвертых выходах элементов 8.9+8.12 последней строки матрицы вычисляется остаток R, если R О, или величина (R-B) в дополнительном коде, если R 0. Разряды частного и остатка транслируются через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ

9и 12 второй и третьей групп соответственно без изменения на выходы третьего

10и четвертого 16 узлов свертки по моду-, лю три соответственно. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 9 являются выходами устройства и определяют разряды частного. Коды делителя А и делимого В с выходов регистров делителя 1 и делимого 2-, а также код частного С с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 9 поступают соответственно на входы первого 3, второго 5 и третьего 10 узлов свертки по модулю три, которые формируют контрольные коды по модулю три: kB Bmod3. kA Amod3, kC Cmod3. Контрольные коды kB и kC далее поступают на входы узла 11 умножения по модулю три, который вычисляет их произведения по модулю три, поступающие на первую группу входов сумматора 13 по модулю три. Код с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы 12 поступает на входы четвертого узла 16 свертки по модулю три, формирующего контрольный код остатка kR Rmod3 при R О или код kR(R-B)mod3 при R 0. Этот код поступает на входы сумматора 13 по модулю три, на другие входы которого подаются слагаемые, комплексирующие разницу между кодами kR и kR для случая . Для этого код kB при пропускается

через элементы И 15.2 и 15.1 группы и поступает на третьи входы сумматора 13 по модулю три, на второй вход четвертого слагаемого приходит сигнал с выхода элемента НЕ 14. Он принимает при единичное значение, компенсирующее единицу, по которой различаются дополнительный и обратный коды величины R-B.

Таким образом, сумматор 13 по модулю три формирует контрольный код kB(kA

kC+kR)mod3, который сравнивается по модулю три на узле 6 сравнения с кодом kB. В случае несовпадения по модулю три кодов kA и kB, что имеет место при неправильном функционировании устройства, узел 6

сравнения формирует единичный сигнал, блокирующий запись следующих разрядов в регистры делителя 1 и делимого 2 с началом следующего такта, а также записывающийся в начале следующего такта в триггер

7(фиг.2).

С выходов триггера 7 единичный сигнал поступает на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой 4, второй 9 и третьей 12 групп, обеспечивая инвертирование кодов,

поступающих на их вторые входы. При этом инвертируют сигналы на первом, третьем и четвертом входах, а также первом, втором и четвертом выходах каждого элемента матрицы 8. Такое инвертирование

сигналов маскирует ошибку, проявившуюся на предыдущем такте, и позволяет получить инверсию правильного частного на вторых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 9, а на их выходах - прямое

значение правильного результата.

Формул а изобретения Устройство для деления чисел, содержащее регистры делимого и делителя, блок

деления, четыре узла свертки по модулю три, узел сравнения, причем информационные входы регистров делимого и.делителя соединены с входами делимого и делителя устройства, выходы регистра делителя соединены с входами первого узла свертки по модулю три и входами делителя блока деления, выходы регистра делимого соединены с входами второго узла свертки по модулю три, выходы которого соединены с

первыми входами узла сравнения, о т л и - ч а ю щ е ее я тем, что. с целью повышения надежности, устройство содержит три группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер, узел умножения по модулю три,

сумматор по модулю три, элемент НЕ, два

элемента И, причем выходы разрядов регистра делимого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выходы которых соединены с входами делимого блока деле- ния, выходы разрядов частного которого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых соединены с выходами частного устройства и с входами третьего узла свертки по модулю три, выходы которого соединены с входами первого операнда узла умножения по модулю три, выходы которого соединены с входами первого слагаемого сумматора по модулю три, вхо- ды второго слагаемого которого соединены с выходами четвертого узла свертки по модулю три. входы которого соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы, первые входы кото- рых соединены с выходами остатка блока деления, выходы первого узла свертки по модулю три соединены с входами сомножители узла умножения по модулю три и

первыми входами первого и второго элементов И, выходы которого соединены с входами третьего слагаемого сумматора по модулю три, выходы которого соединены с вторыми входами узла сравнения, выход которого соединен с входами блокировки записи регистров делимого и делителя и информационным входом триггера, вход сброса триггера соединен с входом сброса устройства, вход записи устройства - с входами разрешения записи регистров делимого и делителя и синхровходом триггера, прямой выход которого соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех групп, инверсный выход триггера - с входом/логической единицы блока деления, выход старшего разряда частного устройства соединен с входом элемента НЕ. выход которого соединен с вторыми входами первого и второго элементов И м первым входом четвертого слагаемого сумматора по модулю три, второй вход четвертого слагаемого которого соединен с входом логического нуля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Устройство для деления на константу 2 @ - 1 | 1990 |

|

SU1714596A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1730624A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1741130A1 |

| Устройство для деления | 1989 |

|

SU1658149A1 |

| Устройство для деления чисел на константу 2 @ - 1 | 1990 |

|

SU1714594A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство цифрового интегрирования | 1988 |

|

SU1532922A1 |

Устройство относится к вычислительной технике и позволит делить два числа с исправлением одиночных ошибок. Цель изобретения - повышение надежности. Устройство Содержит регистры делителя и делимого, принимающие делитель А и делимое В, блок деления, определяющие деления без восстановления остатка частное С и остаток или R-B при R О, узлы свертки, формирующие контрольные коды по модулю три -mod3, , , элемент НЕ, элементы И, сумматор по модулю три, формирующие контрольный код mod3 и kB kA-kC+k-RJmodS, узел, сравнивающий коды kB и kB и, в случае несовпадения, блокирующий прием новых операндов в регистры, а также записывающий единичный сигнал в триггер. В следующем такте под действием этого сигнала на группах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ инвертируются коды делимого, частного и остатка, а также сигналы на входах и выходах блока деления, что позволяет маскировать одиночную ошибку и таким образом получить правильный результат. 2 ил. ё

if мае К

Сброс П Запись

Выход эл-1,эл.2 )( Выход эл. 6 Выход эл, Т

ХИ

У

Л

.Г I

Фиг. 2

| Устройство для деления | 1988 |

|

SU1635183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1992-02-07—Публикация

1989-06-06—Подача