сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1990 |

|

SU1758860A2 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1538239A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Умножитель частоты следования импульсов | 1991 |

|

SU1803970A1 |

| Умножитель частоты импульсов | 1984 |

|

SU1238222A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Счетчик-таймер | 1981 |

|

SU985944A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, измерительной и вычислительной техники. Цель изобретения - повышение точности умножения при одновременном повышении надежности - обеспечивается путем применения однотактного генератора 14 опорной частоты и образования новых функциональных связей. Кроме того, умножитель содержит счетчики 1, 2, 3, 4, 5 импульсов, элемент сравнения 6 кодов, элементы ИЛИ-НЕ и ИЛИ 7 и 8, делитель 9 частоты, блок 10 синхронизации, инвертор 11, шины 12 и 13, входную и выходную соответственно. 1 з.п.ф-лы, 2 ил.

о XJ

о

vj 00

Фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, измерительной и вычислительной техники.

Цель изобретения - повышение точности умножения при одновременном повышении надежности.

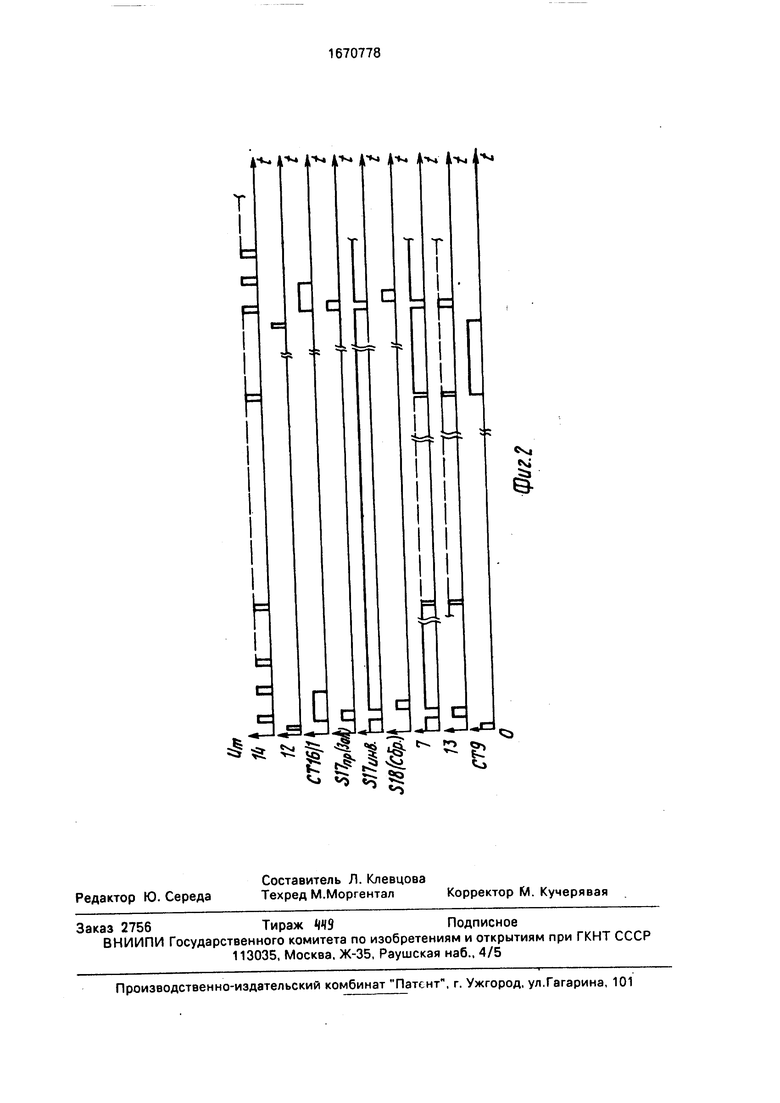

На фиг. 1 приведена электрическая структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Умножитель частоты следования импульсов, содержит первый, второй, третий, четвертый и пятый счетчики 1-5 импульсов, элемент 6 сравнения кодов, элементы ИЛИ- НЕ и ИЛИ 7 и 8, делитель 9 частоты, блок 10 синхронизации,инвертор 11,входную и выходную шины 12 и 13, выходы первого и второго счетчиков 1 и 2 импульсов поразрядно соединены соответственно с первой и второй группами информационных входов элемента 6 сравнения кодов, выход которого соединен с первым входом элемента ИЛИ-НЕ 7, счетные входы первого и пятого счетчиков 1 и 5 импульсов соединены непосредственно с выходом элемента ИЛИ-НЕ 7, а через инвертор 11 - с выходной шиной 13, с тактовым входом делителя 9 частоты и с первым входом элемента ИЛИ 8, второй вход которого соединен с выходом делителя 9 частоты, а выход-с входом сброса второго счетчика 2 импульсов, счетный вход которого соединен со счетным входом третьего счетчика 3 импульсов, с выходом генератора 14 опорной частоты и с первым входом блока 10 синхронизации, второй вход которого соединен с входной шиной 12 и входом сброса делителя 9 частоты, выходы третьего и четвертого счетчиков 3 и 4 импульсов по- разоядно соединены с информационными входами соответственно пятого и первого счетчиков 5 и 1 импульсов, выход переноса пятого счетчика 5 импульсов соединен с входом разрешения переноса первого счетчика 1 импульсов, причем выход последнего разряда третьего счетчика 3 импульсов подключен к входу разрешения счета четвертого счетчика 4 импульсов, первый выход блока 10 синхронизации соединен с входами разрешения записи первого и пятого счетчиков 1 и 5 импульсов, а второй выход блока 10 синхронизации - с входами сброса третьего и четвертого счетчиков 3 и 4 импульсов, причем первый выход блока 10 синхронизации подключен к второму входу элемента ИЛИ-НЕ 7.

Блок 10 синхронизации содержит инвертор 15, делитель 16 частоты, счетный вход которого соединен с первым входом,а вход сброса - с вторым входом блока 10

синхронизации, а выход второго разряда делителя 16 частоты соединен с его же входом разрешения счета через инвертор 15, причем вход первого формирователя 17 импульсов соединен с выходом первого разряда делителя 16 частоты, прямой выход первого формирователя 17 импульсов соединен с первым выходом блока 10 синхронизации, а инверсный выход - с входом

0 второго формирователя 18 импульсов, выход которого соединен с вторым выходом блока 10 синхронизации.

Умножитель частоты следования импульсов работает следующим образом.

5В момент появления импульса входной

частоты на шине 16 происходит установка в исходное (нулевое) состояние делителей 9 и 16. Импупьс с генератора 14 опорной частоты изменяет уровень сигнала на первом вы0 ходе делителя 16 частоты, чем запускает формирователь 17.

Сформированный импульс с прямого выхода формирователя 17 поступает на входы записи счетчиков 1 и 5, чем обеспечива5 ется запись в счетчики 1 и 5 выходных кодов счетчиков 4 и 3 соответственно, при этом в счетчики 5 и 1 записываются соответственно дробная и целая часть кода предыдущего периода импульсов на шине 12. Этот же

0 сигнал поступает через элемент ИЛИ-НЕ 7 и инвертор 11 на шину 13 и далее, через элемент ИЛИ 8 на вход сброса счетчика 2, устанавливая его в нулевое состояние.

В момент срабатывания формирователя

5 17 с его инверсного выхода по заднему фронту запускается формирователь 18, на выходе которого появляется импульс сброса, поступающий на входы сброса счетчиков 3 и 4 импульсов, устанавливая их в исходное

0 состояние.

Второй импульс с выхода генератора 14 изменяет состояние на первом и втором выходах делителя 16 и тем самым через инвертор 15 блокируется делитель 16 до прихода

5 следующего импульса входной частоты по шине 12.

В дальнейшем, до прихода импульса по шине 12 импульсы с выхода генератора 14 поступают на счетный вход счетчика 3, т.е.

0 происходит преобразование в код следующего периода входных импульсов и на счет- ный вход счетчика 2, осуществляя преобразование кода, содержащегося в счетчике 1, в период выходных импульсов.

5Импульсы выходной частоты на шине 13

вырабатываются по коду целой части, содержащейся в счетчике 1, поступающий с выхода элемента ИЛИ-НЕ 7 на счетные входы с етчиков 5 и 1 сигнал обеспечивает из- мет,.-ие упомянутого кода целой части, что

приводит к соответствующей коррекции периода выходных импульсов. Параллельный код, записанный в счетчике 1, подается на элемент 6 сравнения, на вторые одноименные входы которого подается код счетчика 2, Импульсы на выходе элемента 6 сравнения будут появляться каждый раз при равенстве кодов счетчиков 1 и 2 импульсов. Емкость делителя 9 определяет коэффициент умножения и равна емкости счетчика 3.

Цикл работы устройства повторяется после поступления на входную шину 12 следующего импульса входной частоты.

Применение двух формирователей с последовательным их включением позволит сосу ществить формирование двух команд (запись и сброс) в строгой последовательности друг за другом, что повышает точность, обусловленную большей равномерностью выходных импульсов, за счет применения однотактного генератора опорной частоты, что дает возможность увеличить его частоту, прямо влияющую на равномерность выходной частоты умножителя и надежность за счет упрощения схемы.

Формула изобретения

сброса второго счетчика импульсов, счетный вход которого соединен со счетным входом третьего счетчика импульсов, с выходом генератора опорной частоты и с первым вхо- 5 дом блока синхронизации, второй вход которого соединен с входной шиной и входом сброса делителя частоты, выходы третьего и четвертого счетчиков импульсов поразрядно соединены с информационными входами

0 соответственно пятого и первого счетчиков импульсов, выход переноса пятого счетчика импульсов соединен с входом разрешения переноса первого счетчика импульсов, причем выход последнего разряда третьего

5 счетчика импульсов подключен к входу разрешения счета четвертого счетчика импульсов, первый выход блока синхронизации соединен с входами разрешения записи первого и пятого счетчиков импульсов, а

0 второй выход - с входами сброса третьего и четвертого счетчиков импульсов, отличающийся тем, что, с целью повышения точности умножения при одновременном повышении надежности, первый выход бло5 ка синхронизации подключен к второму входу элемента ИЛИ-НЕ.

0 которого соединен с первым входом, а вход сброса - с вторым входом блока синхронизации, а выход второго разряда делителя частоты соединен с его же входом разрешения счета через инвертор, отличающий5 с я тем, что в него введены первый и второй формирователи импульсов, причем вход первого формирователя импульсов соединен с выходом первого разряда делителя частоты, прямой выход первого формирова0 теля импульсов соединен с первым выходом блока синхронизации, а инверсный выход- -.. с входом второго формирователя импульсов, выход которого соединен с вторым выходом блока синхронизации.

5

Т

| Авторское свидетельство СССР кл | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шланговое соединение | 0 |

|

SU88A1 |

Авторы

Даты

1991-08-15—Публикация

1989-03-30—Подача