(54) СЧЕТЧИК-ТАЙМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления аналого-цифровым преобразователем | 1978 |

|

SU748399A1 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1171795A1 |

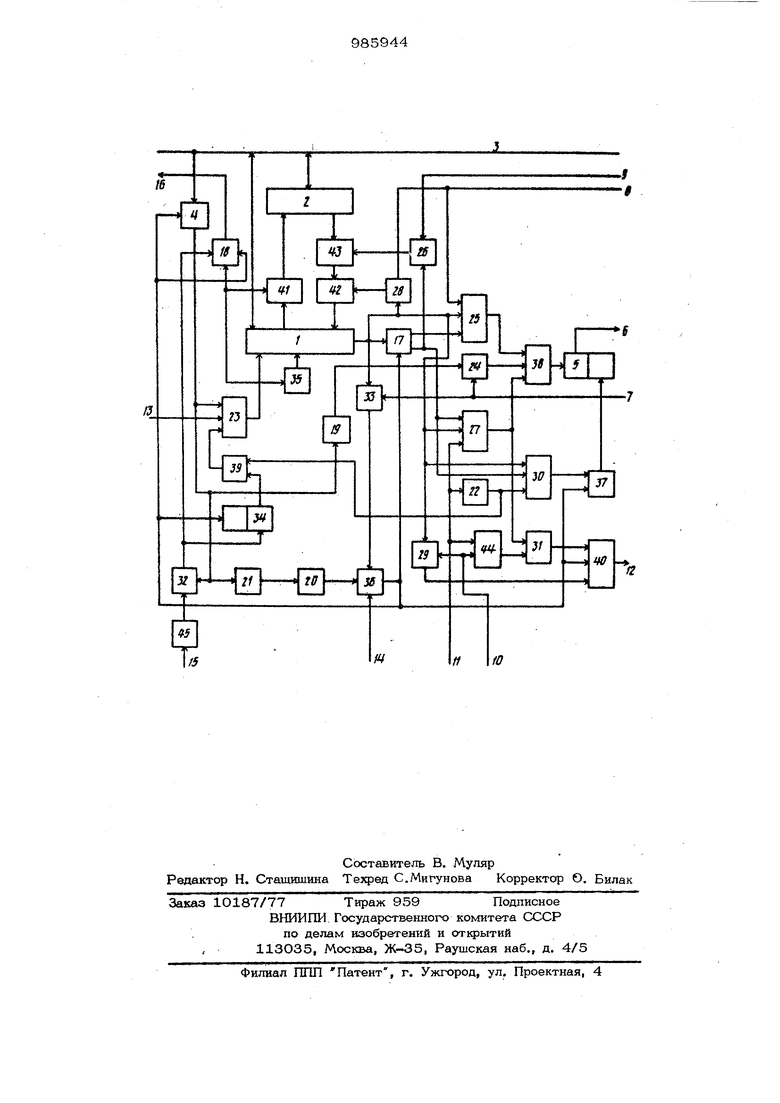

Изобретение относится к импульсной технике и автоматическому управлению и может быть использовано для формирования управляемых задержек различного тина, аналого-цифрового преобразования (А1Ш), двухшагового интегрирования и преобразования частота-код. Известно устройство управления аналого-цифровым преобразователем, которое может быть использовано как сча-р чик-накопитель, содержащее счетчик, блок пуска, триггер, вентили считьшания управляющие щины 11 Недостатком такого устройства является то, что его нельзя использовать дл формирования управляемых задержек и пре образования частота-код. Помимо этого длительность первого шага интегрирован НИИ у него фиксирована,, что требует для отстройки от помех промыщланн(Л сети использовать, внешнкзю схему АПЧ (автоподстройки частоты), что услоя. няет преобразователь в целом. Наиболее близким к предлагаемому по конструкции и функциональным является счетник-таймер, содержащий счетчик, регистр, схему управления, блок пуска и триггер 2 . Недостаток устройства заключается в том, что оно не выполняет функции двухшагового интегрирования, преобразования частота-код, формирования многократных задержек. Цель изобретения - расширение функциональных возможностей счетчика-таймера. Поставленная цель достигается тем, что в устройство, содержащее инвертор щьа. формирователя, счетчик, регистр, триггер, &ГЮК пуска выход которого соединен с первым входом первого элемента И. входом первого формирователя, и через инвертор с входом второго формнр вателя, выход которого через первый, а затем второй элементы ИЛИ соединен с первым входом триггера, выход первого формирователя соединен с первым входом 398 второго элемента И, второй вход которого соединен с первой шиной перестройки, а выход - с первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом триггера, выход которого соединен с выходной шиной, а выход пер вого элемента И соединен со счетным входом счетчика, выход переноса которого соединен с первым входом третьего элемента И, второй вход которого соединен с второй шиной перестройки, а выход - с вторым входом третьего элемента ИЛИ, а интерфейсная шина соединена с установочными входами блока пуска, регистра и счетчика, третья шина перестройки соединена с первым входом чет вертого элемента И, дополнительно введ ны семь элементов И, три триггера, фор мирователь, инвертор, блок задержки, два элемента ИЛИ и один элемент ИЛИ- НЕ, два блока элементов И и блок инверсии, первый вход которого соединен с выходом регистра, второй вход - с выходом четвертого элемента И, при этом первый вход третьего элемента И соединен с первыми входами первого, второго, третьего, четвертогчэ и седьмого дополнительных элементов И и первым входом первого дополнительного три гера, первый выход которого соединен с третьим входом третьего элемента И, выход первого дополнительного элемента И соединен с третьим входом третьего элемента ИЛИ и с первым . входом пятого дополнительного элемен , та И, четвертая шина перестройки соединена с вторым входом третьего дополнительного элемента И и первым входом элемента ИЛИ-НЕ, второй вход которого соединен с пятой шиной перестройки, вторым входом первого дополнительного элемента И и входом дополнительного инвертора, выход которого соединен с первым входом первого дополнительного элемента ИЛИ и с вторым входом четвертого дополнительного эл&мента И, выход которого соединен с вто рым входом второго элемента ИЛИ, выход элемента ИЛИ-НЕ соединен с вторы входом пятого дополнительного элемента И, выход которого соединен с первьшс входом второго Дополнительного элемента ИЛИ, второй вход которого соединен с первым входом блока пуска, вторым входом первого дополнительного трнг гера, выходом первого элемента ИЛИ, и первыми входами второго и третьего дополнительных триггеров, выход второг дополнительного элемента ИЛИ соединен 44 с шшюй синхронизации, а третий его вход с выходом третьего дополнительного элемента И, причем маркерная шина через дополнительный формирователь соединена с первым входом шестого дополнительного элемента И, второй вход которого соединен с выходом блока пуска, второй вход четвертого элемента И объединен с третьими входами первого и четвертого дополнительных элементов И и вторым выходом первого дополнительноо триггера, а выход шестого дополниельного элемента И соединен с вторыьш ходами второго и третьего дополнительных триггеров, выход второго ДОПОЛНЕНтельного триггера соединен через первый дополнительный элемент ИЛИ с втЭрым входом первого элемента И, третий вход которого соединен с шиной второй частоты, дополнительная выходная шина соединена с первым выходом третьего дополнительного триггера, второй выход которого соединен с входом сброса, счетчика и непосредственно с первым входом первого блока И, второй вход которого соединен с выходом счетчика, а выход первого блока И соединен с входом регистра, выход блока инверсии соединен с первым входом второго блока И, выход которого соединен с управляющим входом счетчика, второй вход второго блока И соединен с выходом второго дополнительного элемента И, второй вход седьмого дополнительного элемента , И соединен с первой шиной перестройки, а его вызюд - с вторым входом первого элемента ИЛИ, третий вход которого соединен с шиной останова. На чертеже приведена функциональная схема предлагаемого счетчика-таймера. Схема содержит счетчик 1, регистр 2, интерфейсную шину 3, блок 4 пуска, основной триггер 5 с выходной шиной 6, шины 7-11 перестройки, шина 12 синхрониэации, шина 13 второй частоты, шина 14 останова, маркерная шина 15, дополнительная выходная шина 16, дополнительные счетные триггеры 17 и 18, формирователи 19 и 20, инвертор 21, дополнительный инвертор 22, эл&менты И 23-33, дополнительный триггер 34, блок 35 задержки, элементы ИЛИ 36-40, первый и второй блоки И 41 и 42, блок 43 инверсии, элемент ИЛИ-НЕ 44 и дополнительный формирователь 45. Приншш работы устройства - формирование очередности следующих одна аа 59 другой задержек, величины которых зада ются программно или внешним устройством, от маркерной шины 15. Перестрой ка структуры устройства производится шинами 7-11 перестройки, которые соответственно включают режимы однокраной задержки, циклической задержки, шв ротно-импульсной модуляции, Тшюгократуной задержки, двухшагового интегрирова ния (либо преобразования частотг код). Устройство работает следуюшим обра зом. Режим однократной задержки задаетс включением шины 7. После программной записи кода задержки в счетчик 1 (в дополнительном коде) н включения первого формирователя 19 от блока 4 пуска включаются элементы И 24, ИЛИ 38, и шина 6 через триггер 5. Счетный триг гер 17 обеспечивает коммутацию входов триггера 5 и участвует в формировании сигнала выходной шины 6 длительностью равной периоду импульсов входной частоты шины 13. От момента включения блока 4 пуска импульсы входной частоты поступающие на шину 13, передаются че рез элемент С 23 на счетчик 1, которы вырабатывает импульс переполнения (переноса), вьпслючающий через элементы И ЗО и ИЛИ 37 триггер 5. Одновременно через элемент И 33 выклю1чается блок 4 пуска. Разрешение счета в этом режиме поступает от первого входа эл&мента ИЛИ 39 через инвертор 22, работающего от низкого уровня шины 11. Одновременно через элемент ИЛИ 4О возбуждается шина 12, сигнал с которой идет на прерывание процессора, либо син хронизацию какой-либо другой управляющей логики. На элемент ИЛИ 4О сиг нал при этом проходит от переполнения счетчика 1 через элементы И 27 и 31, при этом шины 1О и 11 выключены и элемент ИЛИ-НЕ 44 находится В:.состоянии разрешения прохождения сигнала через элемент И 31. В режиме циклической задержки, задаваемой шиной 8, элемент ИЛИ 33 не срабатьгоает и блок 4 пуска и дополнительный триггер 34 не выключаются. Возможен программный останов через инвертор 21 и формирователь 2 О от блока пуска. Цикличность формирования задержки обеспечивается записью установки в гистр 2 и переписью ее аппаратно концом цикла через элемент И 28 и блок 42 вентилей. Блок 43 инверсии в этом режиме элементов И 26 не переключается 4 и передает содержимое регистра 2. на счетчик 1 без инверсии. Цикличность запуска триггера 5 обеспечивается эл&ментом И 25, пропускаюшит каждый второй импульсы переполнения счетчика 1за счет совместной работы со счетным триггером 17. Этот режим обеспечивает деление входной частоты на удвоенный заданный коэффициент и выдачу результата по шине 6 в виде импульсов со скважностью 2. Сигнал такой формы для управления реальными объектами является предпочтительным. Режим широтно-импульсной модул$тии выбирается шиной 9, которая, будучи включена ссжместно с шиной 8, обеспечивает модификацию режима циклической задержки, а именно, формирует паузу, не равную длительности импульсу, а являющуюся инверсной к коду задержхШ. Период импульсов при этом равен не 2 где п - разрядность счетчика, как было бы при паузе, сформированной на дополнительном коду, а 2 -1, что, однако, не влияет на точность, так как линейность сохраняется, а погрешность дисщзетно не превьиыает младшего разряда. Режим многократной задержки обеопеч шет формирование на шине 6 помимо интервалов времени включения объекта также н заданное время включейия объекта. Режим многократной задержки выбирается ссжместным включением шины . 1О и режима циклической задержки. Шина 12 синзфонизации в этом режиме возбуждается элемент И 29 от каждого импульса переполнения счетчика. По этим импульсам процессор или другая управляющая логика записывает в регистр 2по шинам 3 новый кед, соответствук ший времени включения, либо выключения шины 6. Режим, при котором активна шина, 11 перестройки, применяется при таких измерениях интервалов времени, которые иопользуют KaKyio-либо опорную базу . Такие измерения используются при вухшаговом методе преобразования ийнпряжение-код, преобразовании интервал времени-код, частота-код. Стартовый и стоповый импульсы поступают на марке{ ную шину 15. При использовании в преобразователенапр$1жени&-крд таймер интервал времени первого шага интегрирования на дополнительную шину 16, в это время происходит заряд из798мерительного коьщенсатора (во внешней схеме) от измеряемого напряжения, время второго шага интегрирования сш1мается с шины 6, в течение этого времени происходит разряд,измерительного ковденса трра эталонным током. Концу разряда со ответствует срабатьюание 1-1уль-органа во (внешней схеме), формируюш его сигнал останова на шине 14. Этот сигнал идет на шину 12 и выключает триггер 5. В качестве базы времени первого шага интегрирования используется период частоты силовой сети, помехи которой следует подавить. Для этого напряжение это сети подается через соответствующий делитель на шину 15. Нервый шаг интегрирования завершает ся о приходом Ьторого, после включения блока 4, импульса на шину 15. Этот импульс с выхода второго счетного триггера 18 переписьюает через блок 41 код первого шага интегрирования в регис 2, после чего счетчик сбрасывается чере блок задерлши 35 и производится накопление и Шyльcoв второго шага интегрирования до момента прихода на шину 14 и элемента ИЛИ 36 сигнала останова. Деление кода счетчика на код регистра, производимое процессором, дает результат измерения, не зависящий от девиации частоты и, следовательно, с максимальным подавлением помех. Таймер может быть также использоBaii для измерения напряжения по другому алгоритму. При малом уровне промышлен- ных помех период первого шага интегрировапия задается автономно, т.е. npoiраммно, а не по внешним маркерным импульсам. В этом варианте использования операция деления может быть исключена. Включение таймера в этот режим производится заданием режима циклической задержки и ги-шерсным подключением шины, б к шине 15. Время первого шага интегрирования снимается с шины 6, а второго - с дополнительной выходной Шины 16. По фронту выключения шины 6 (конец первого шага интегрирования) включается счетный триггер 18 через элемент И 32 и формирователь 45 от шины 15, выключение же его происходит по останову от шины 14. В этот же момент происходит останов, а также возникает синхроимпульс на шине 12. В регистре 2 должна быть записана нулевая информация с тем, чтобы перепись регистра, в , производимая по окончанию первого шага интегрирования, 48 подтвердила нулевой код счетчика, соопветствующий вго переполнению. , В режиме частота-код или при измерении заданного интервала времени устана шшается режим включения шины 11, на шину 15 подается импульс пуска, на шину 14 подается импульс останова. Таймер может быть использован как счетчик-накопитель, причем общее кол1ячество импульсов может превьш ать раэрядную сетку счетчика. Дпя этого ВКЛЕОчается режим многократной задержки (шины 10,8), а в регистр заносится нулевой код. Импульсы очередных переключений идут на шину 12 и могут програкфмно накапливаться, а текущий код мольно программно сосчитать со счетчика, Таким образом, таймер может быть использован как выходной преобразователь, формирующий сигналы управления реальным объектом и синхронизации, а также как входной преобразователь, осуществляюший измерение заданных интервалов времени. Рассмотренные свойства таймера позволяют использовать его в качестве однократной, циклической и многократной задержек, широтно-импульсного модулятора, для преобразования интервалов вре:мени в качестве счетчика-накопителя. Наличие двух вариантов измерения напряжения позволяет использовать пр еобразователь для исследования уровня промышленных помех. ормула изобретения Счетчик-таймер, содержащий инвертор, два формирователя, счетчик, регистр. триггер, блок пуска, выход которого сюединен с первым входом первого элемента И, входом первого формирователя к через инвертор с входом второго форь/мрователя; выход которого через последовательно соединенные первый, второй элементы ИЛИ соединен с первым входом триггера, выход первого формироЕ.агтеля соединен с первым входом второго элемента И, второй вход которого соединен с первой шиной перестройки, а выход - с первым входом третьего элемента ИЛИ, выход которого соединен с вторым входом триггера, выход котор зго соединен с выходной шиной, а выход керхвого элемента И соединен со счетным входом счетчика, выход переноса которого соединен с .первым входом третьего элемента И, второй вход которого соединен с второй шиной перестройки, а выход - с вторым входом третьего элемента ИЛИ, а интерфейсная шина соединена с установочными входами регистра счетчика и блока пуска, третья шина . перестройки соединена с первым входом четвертого элемента И, отличающ и и с я тем, что, с целью расширения функциональных возможностей счетчикатаймера, в него дополнительно введены семь элементов И, три триггера, формирователь, инвертор, блок задержки, два элемента ИЛИ, и один элемент ИЛИ НЕ, два блока элементов И и блок инверсии, первый вход которого соединен с вь1ходом регистра, второй вход соединен выходом четвёртого элемента И, при этом первый вход третьего элемента И соединен с первыми входам первого, второго, третьего, четвертого и седьмого дополнительных элементов И и первы входом первого дополнительного триггера, первый выход которого соединен с третьим входом третьего элемента И, выход первого дополнительного элемента И соединен с третьим входом третьего элемента ИЛИ и с первым входом пятого дополнительного элемента И, четвертая шина перестройки соед1шена с. вторым входом третьего дополнительного элемента И и первым входом элемента И ЛИ НЕ, второй вход которого соединен с пятой шиной перестройки, вторым входом первого дополнительного элемента И и входом дополнительного инвертора, выход которого соединен с первым входом первого дополнительного элеме;нта ИЛИ и с вторым входом четвертого дополнительного элемента И, выход которо го соединен с вторым входом второго элемента ИЛИ, выход элемента ИЛИ-НЕ соединен с вторым входом пятого ДОПОЛгнительного элемента И, выход которого соединен с первым входом второго дополнительного элемента ИЛИ, второйвхо которого соединен с первым входом блока пуска, вторым входом первого.дополнительного триггера, выходом первого эле мента ИЛИ, и первыми входами второго 9 410 й третьего дополнительных триггеров, выход второго дополнительного элемента ИЛИ соединен с шиной синхронизации, а третий его вход соединен с выходом тре« тьего дополнительного элемента И, причем маркерная шина через дополнительный формирователь соединена с первым входом шестого дополнительного элемента И, второй вход которого соединен с выходом блока пуска, второй вход четвертого элемента И соединен с третьими . входами первого и четвертого дополнительных элементов И и вторым выходом первого дополнительного триггера, а выход шестого дополнительного элемента И соединен с вторыми входами второго и третьего дополнительных триггеров, выход второго дополнительнохчэ триггера соединен через первый дополнительный элемент ИЛИ с вторым входом первого элемента И, третий вход которого соединен с шиной второй частоты, дополнительная выходная ш1ша соединена с выходом третьего дополнительного триггера, второй выход которого соединен через блок задержки со входоь- сброса счетчика и непосредственно с первым входом первого блока И, второй вход которого соединен с выходом счетчика, а выход первого блока И соединен с входом регистра, выход блока инверсии соединен с первым входом второго блока И, выход которого соединен с управляющим входом счетчика, второй вход второго блока И соединен с выходом второго дополнительного элемента И, второй вход седьмого дополнительного элемента И соединен с первой шиной перестройки, а его выход связан с вторым входом первого элемента ИЛИ, трей тий вход которого соединен с шиной останова. Источники информации, . принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 748399, кл. G Об F 1/О4, 1980. 2.Авторское свидетельство СССР № 7И689, кл. Н 03 К 23/ОО, 198О.

Авторы

Даты

1982-12-30—Публикация

1981-04-13—Подача