Изобретение относится к радиоизмерительной технике и может быть применено в системах фазовой автоподстройки частоты в качестве фазового детектора.

Цель изобретения - повышение достоверности измерения сдвига фаз двух импульсных периодических последовательностей.

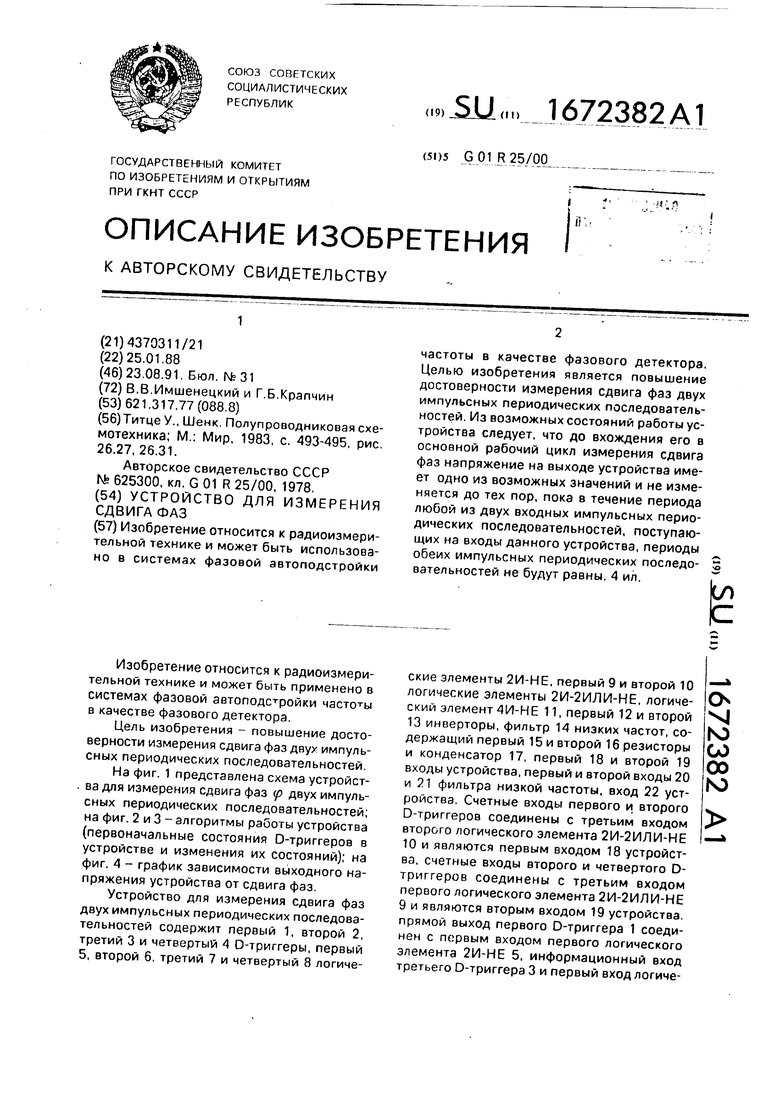

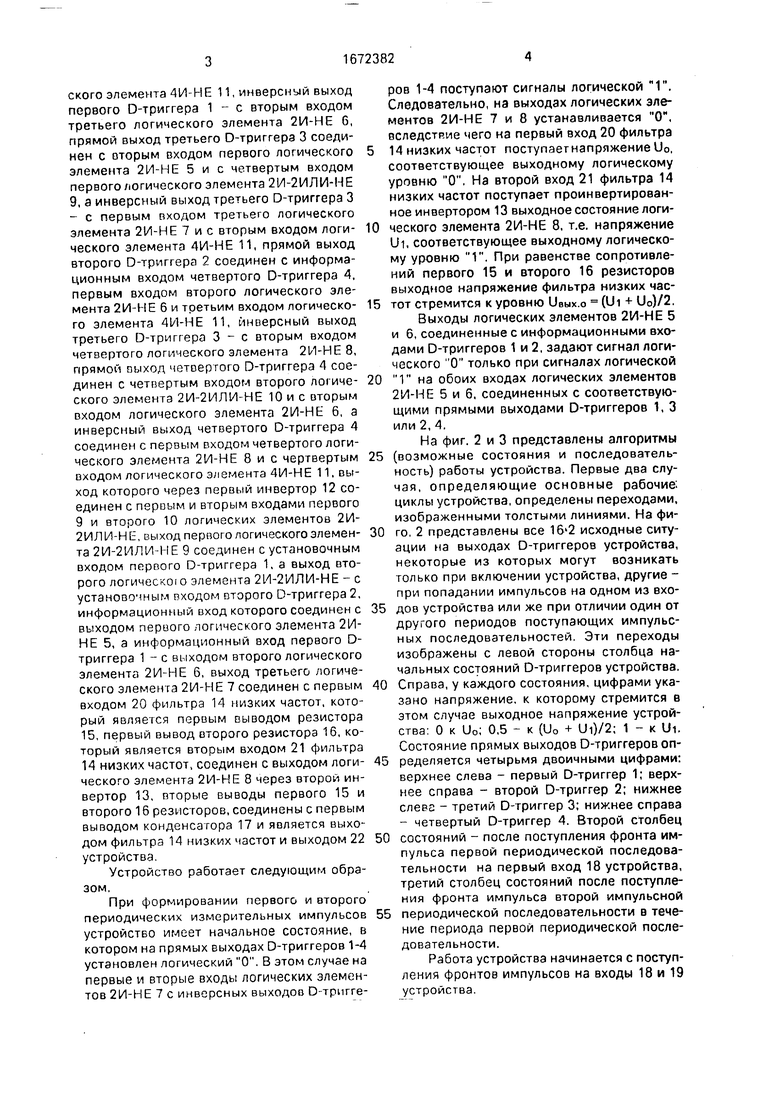

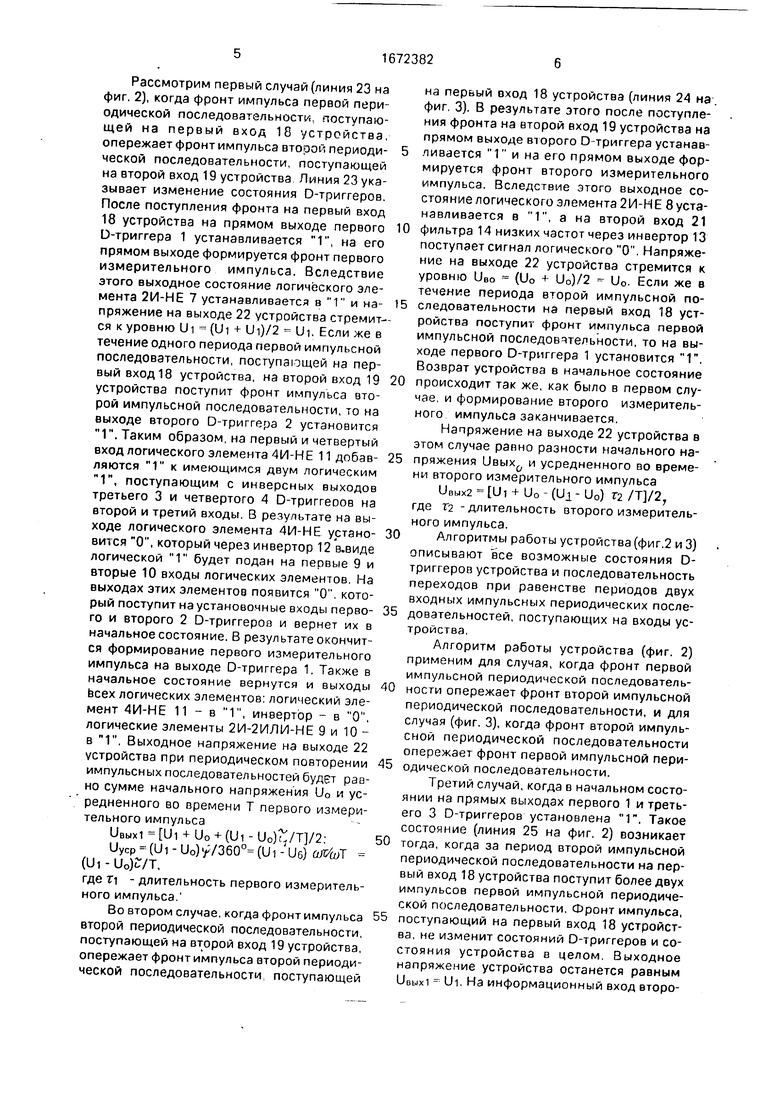

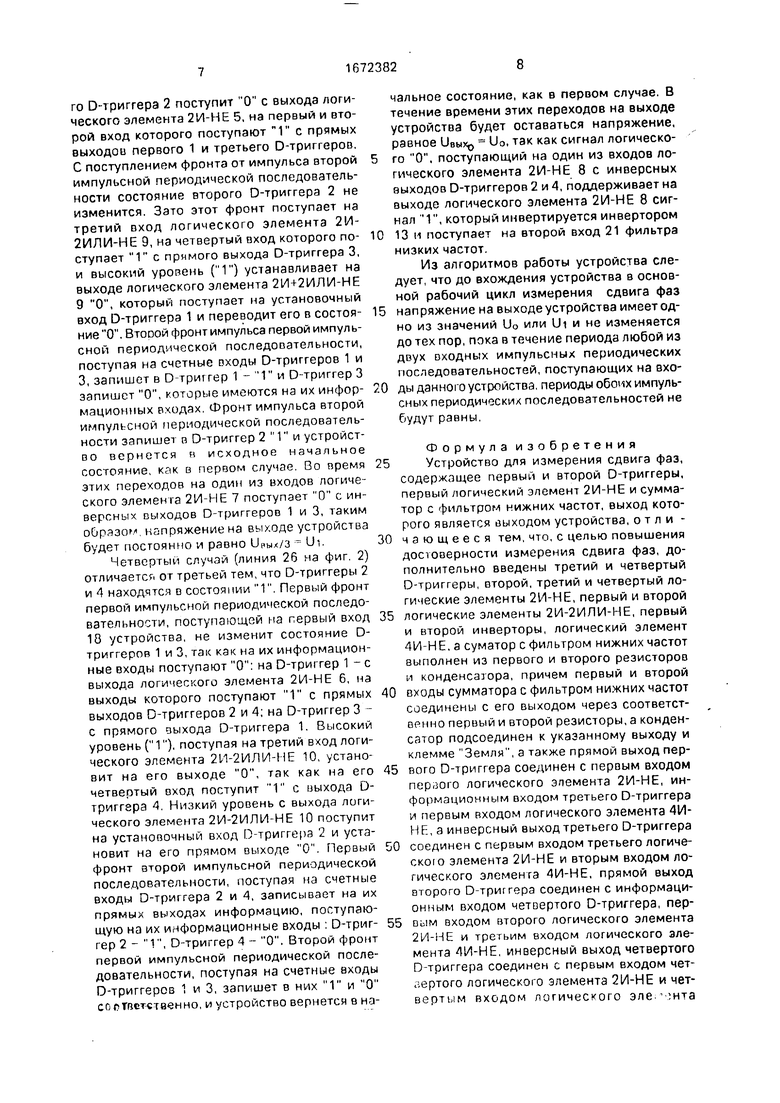

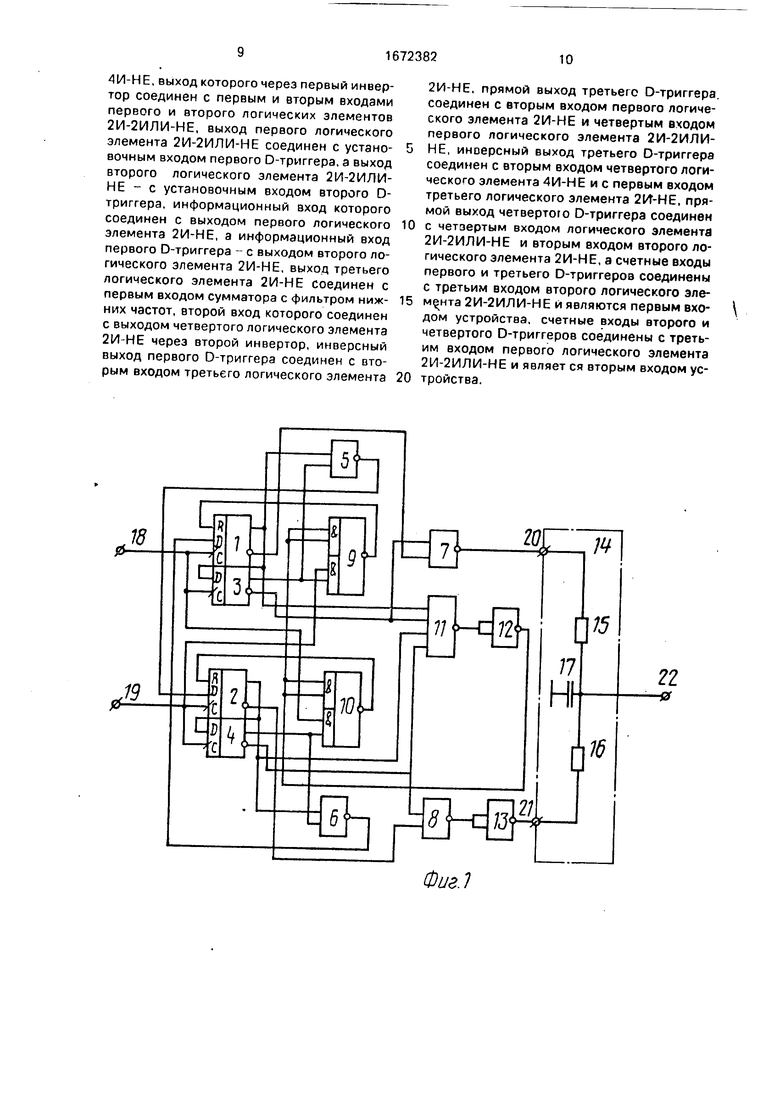

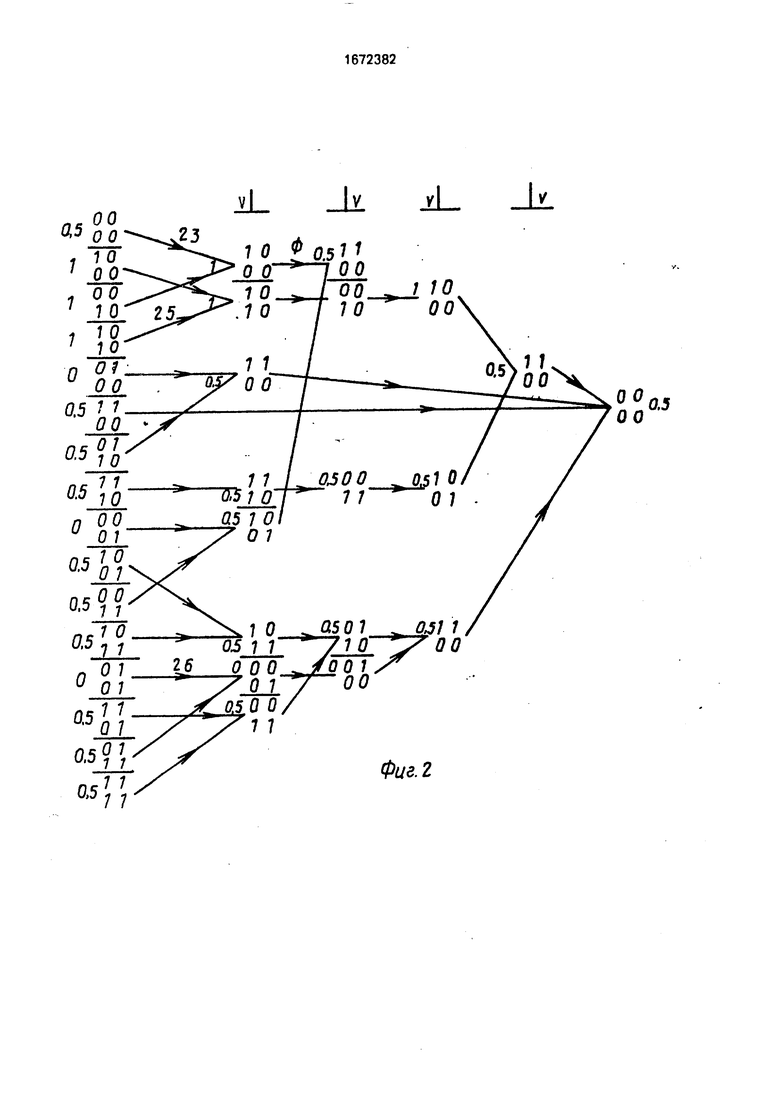

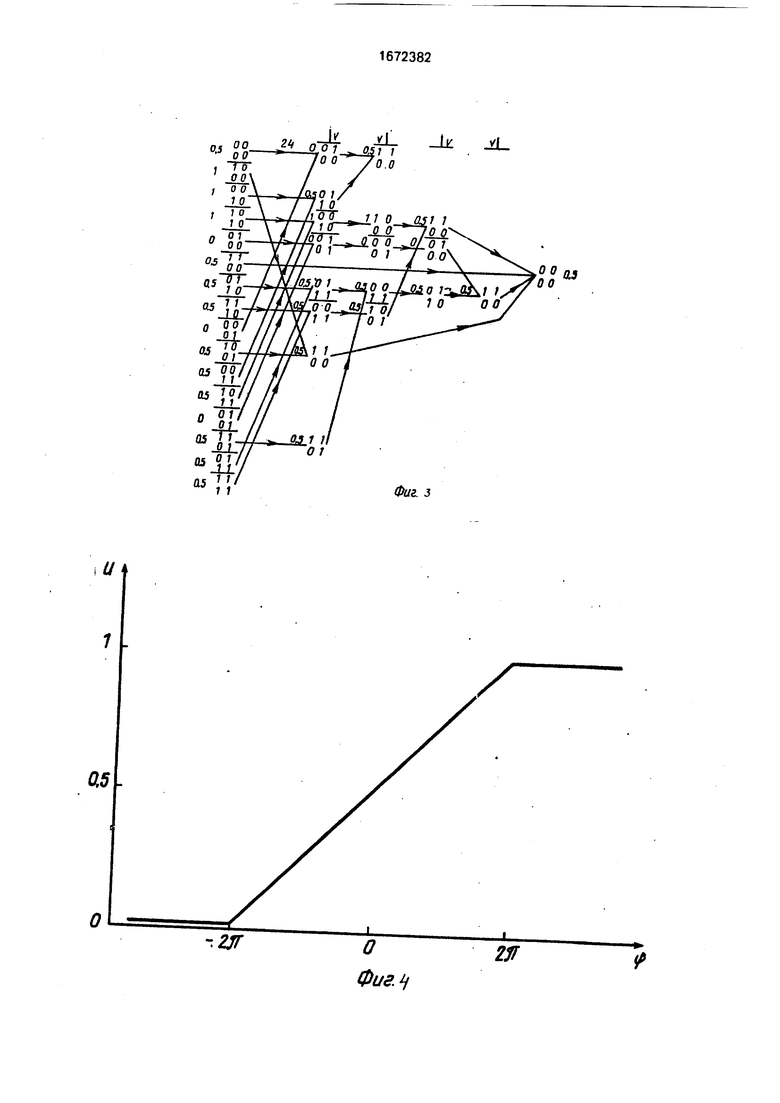

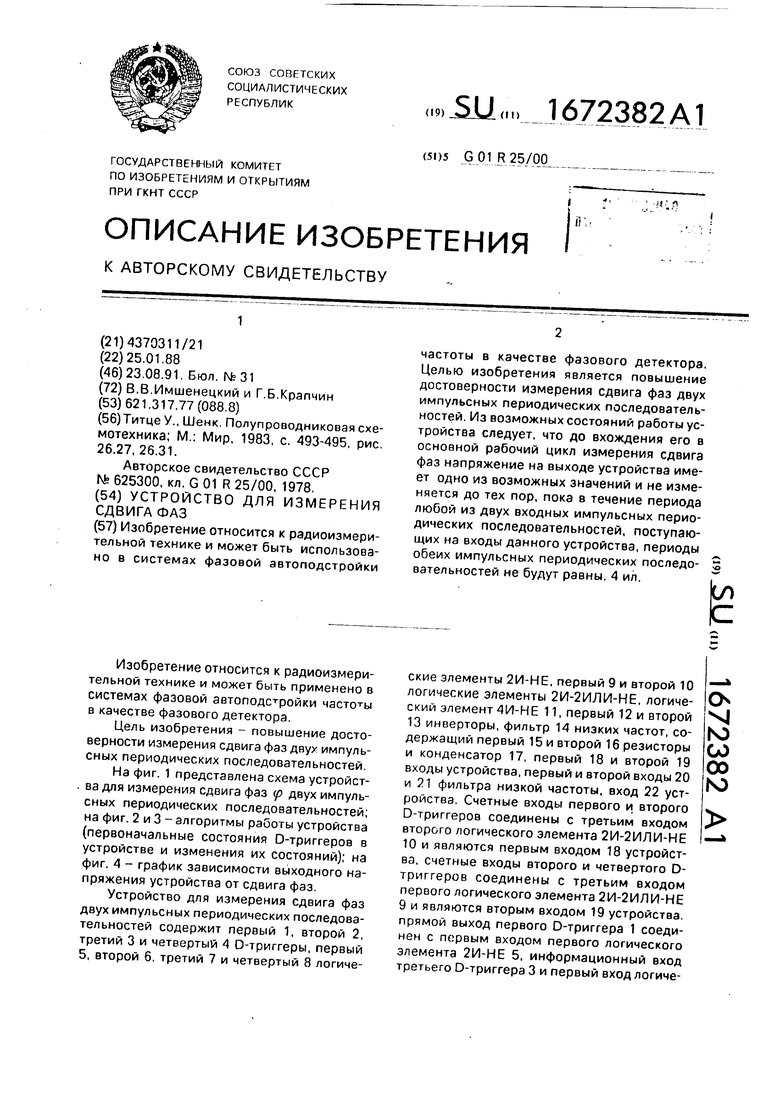

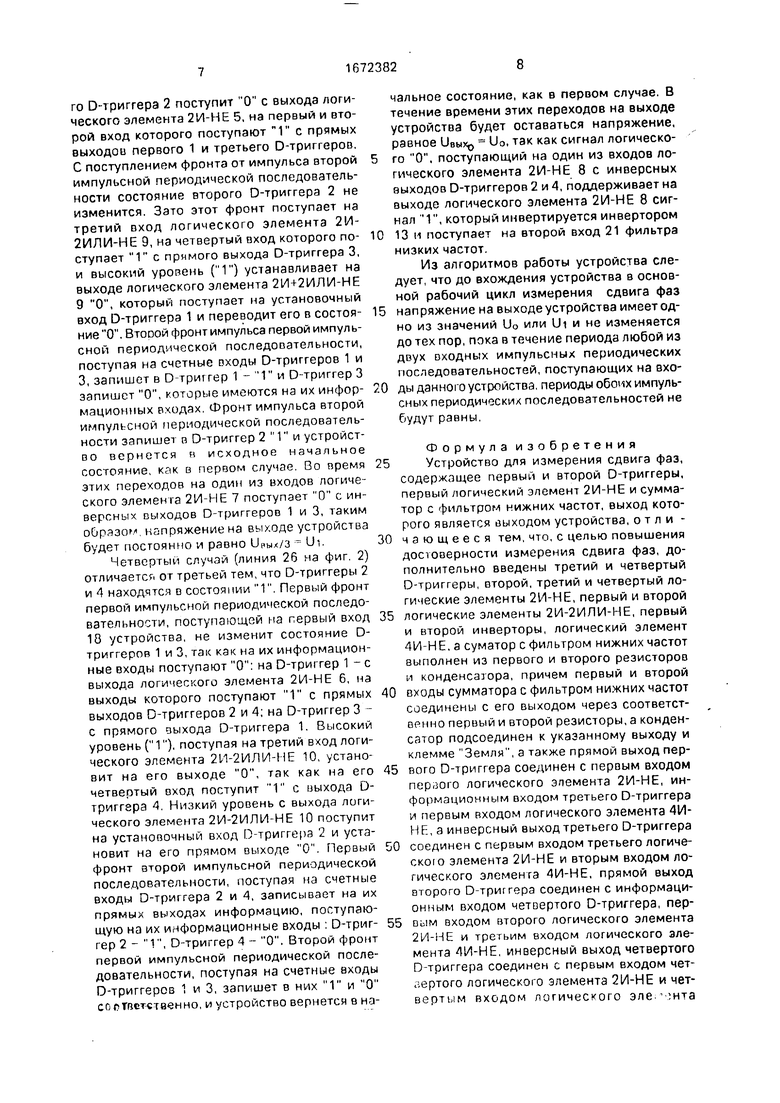

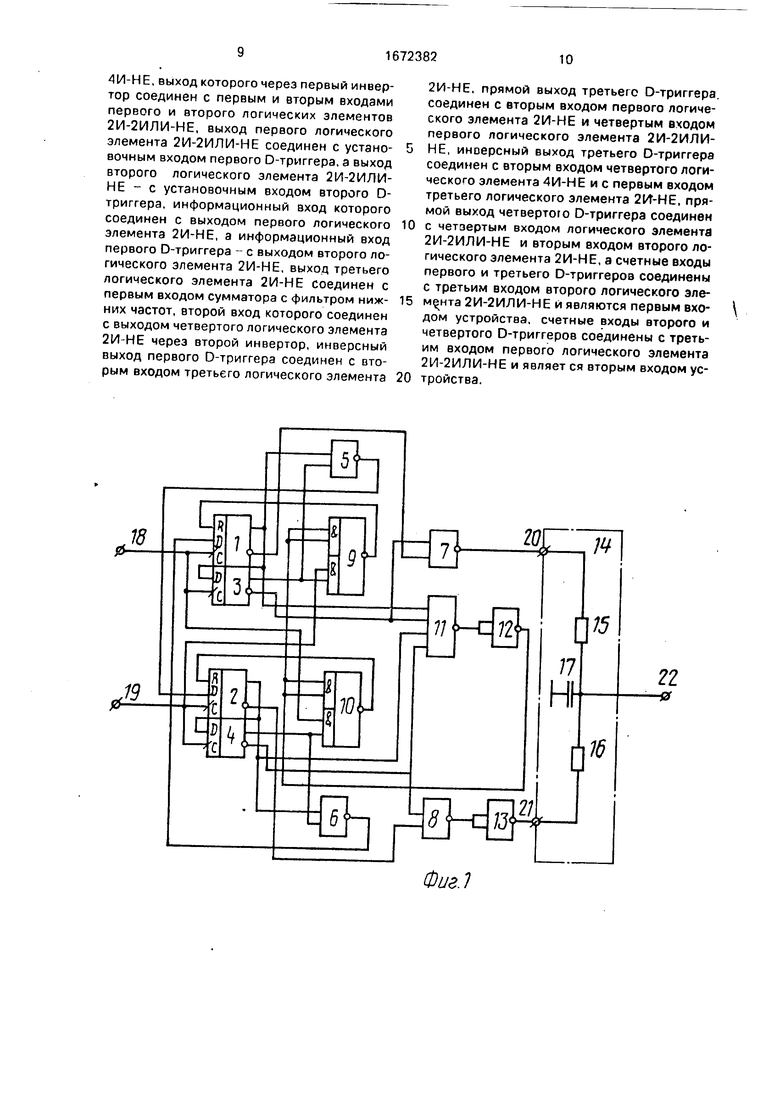

На фиг. 1 представлена схема устройства для измерения сдвига фаз р двух импульсных периодических последовательностей; на фиг. 2 и 3 - алгоритмы работы устройства (первоначальные состояния D-триггеров в устройстве и изменения их состояний); на фиг. 4 - график зависимости выходного напряжения устройства от сдвига фаз.

Устройство для измерения сдвига фаз двух импульсных периодических последовательностей содержит первый 1, второй 2, третий 3 и четвертый 4 D-триггеры, первый 5, второй б, третий 7 и четвертый 8 логические элементы 2И-НЕ, первый 9 и второй 10 логические элементы 2И-2ИЛИ-НЕ, логический элемент 4И-НЕ 11, первый 12 и второй 13 инверторы, фильтр 14 низких частот, содержащий первый 15 и второй 16 резисторы и конденсатор 17, первый 18 и второй 19 входы устройства, первый и второй входы 20 и 1 фильтра низкой частоты, вход 22 устройства. Счетные входы первого и второго D-триггеров соединены с третьим входом второго логического элемента 2И-2ИЛИ-НЕ 10 и являются первым входом 18 устройства, счетные входы второго и четвертого D- триггеров соединены с третьим входом первого логического элемента 2И-2ИЛИ-НЕ 9 и являются вторым входом 19 устройства. прямой выход первого D-триггера 1 соединен с первым входом первого логического элемента 2И-НЕ 5, информационный вход третьего D-триггера З и первый вход логичеО

N) СО 00

1ЧЭ

ского элемента 4И-НЕ 11, инверсный выход первого D-триггера 1 - с вторым входом третьего логического элемента 2И-НЕ б, прямой выход третьего D-триггера З соединен с вторым входом первого логического элемента 2И-НЕ бис четвертым входом первого логического элемента 2И-2ИЛИ-НЕ 9, а инверсный выход третьего D-триггера З - с первым входом третьего логического элемента 2И-НЕ 7 и с вторым входом логического элемента 4И-НЕ 11, прямой выход второго D-триггера 2 соединен с информационным входом четвертого D-триггера 4, первым входом второго логического элемента 2И-НЕ 6 и третьим входом логического элемента 4И-НЕ 11, инверсный выход третьего D-триггера 3-е вторым входом четвертого логического элемента 2И-НЕ 8, прямой выход четвертого D-триггера 4 соединен с четвертым входом второго логического элемента 2И-2ИЛИ-НЕ 10 и с вторым входом логического элемента 2И-НЕ 6, а инверсный выход четвертого D-триггера 4 соединен с первым входом четвертого логического элемента 2И-НЕ 8 и с чертвертым входом логического элемента 4И-НЕ 11, выход которого через первый инвертор 12 соединен с первым и вторым входами первого 9 и второго 10 логических элементов 2И- 2ИЛИ-НЕ, выход первого логического элемента 2И-2ИЛИ-НЕ 9 соединен с установочным входом первого D-триггера 1, а выход второго логическою элемента 2И-2ИЛИ-НЕ - с установочным входом второго D-триггера 2, информационный вход которого соединен с выходом первого логического элемента 2И- НЕ 5, а информационный вход первого D- триггера 1 - с выходом второго логического элемента 2И-НЕ 6, выход третьего логического элемента 2И-НЕ 7 соединен с первым входом 20 фильтра 14 низких частот, который является первым выводом резистора 15, первый вывод второго резистора 16, который является вторым входом 21 фильтра 14 низких частот, соединен с выходом логического элемента 2И-НЕ 8 через второй инвертор 13, вторые выводы первого 15 и второго 16 резисторов, соединены с первым выводом конденсатора 17 и является выходом фильтра 14 низких частот и выходом 22 устройства.

Устройство работает следующим образом.

При формировании первого и второго периодических измерительных импульсов устройство имеет начальное состояние, в котором на прямых выходах D-триггеров 1-4 установлен логический О, В этом случае на первые и вторые входы логических элементов 2И-НЕ 7 с инверсных выходов D-триггеров 1-4 поступают сигналы логической 1. Следовательно, на выходах логических элементов 2И-НЕ 7 и 8 устанавливается О, вследсткие чего на первый вход 20 фильтра

14 низких частот поступаетнапряжениеОо, соответствующее выходному логическому уровню О, На второй вход 21 фильтра 14 низких частот поступает проинвертирован- ное инвертором 13 выходное состояниелоги0 ческого элемента 2И-НЕ 8, т.е. напряжение Ui, соответствующее выходному логическому уровню 1. При равенстве сопротивлений первого 15 и второго 16 резисторов выходное напряжение фильтра низких час5 тот стремится к уровню Увых.о (Ui + Uo)/2. Выходы логических элементов 2И-НЕ 5 и 6, соединенные с информационными входами D-триггеров 1 и 2, задают сигнал логического О только при сигналах логической

0 1 на обоих входах логических элементов 2И-ИЕ 5 и 6, соединенных с соответствующими прямыми выходами D-триггеров 1, 3 или 2, 4.

На фиг. 2 и 3 представлены алгоритмы

5 (возможные состояния и последовательность) работы устройства. Первые два случая, определяющие основные рабочие, циклы устройства, определены переходами, изображенными толстыми линиями. На фи0 го, 2 представлены все исходные ситуации на выходах D-триггеров устройства, некоторые из которых могут возникать только при включении устройства, другие - при попадании импульсов на одном из вхо5 дов устройства или же при отличии один от другого периодов поступающих импульсных последовательностей, Эти переходы изображены с левой стороны столбца начальных состояний D-триггеров устройства.

0 Справа, у каждого состояния, цифрами указано напряжение, к которому стремится в этом случае выходное напряжение устройства: 0 к U0; 0,5 - к (U0 + Ui)/2; 1 - к Ui. Состояние прямых выходов D-триггеров оп5 ределяется четырьмя двоичными цифрами: верхнее слева - первый D-триггер 1; верхнее справа - второй D-триггер 2; нижнее слева - третий D-триггер З; нижнее справа - четвертый D-триггер 4. Второй столбец

0 состояний - после поступления фронта импульса первой периодической последовательности на первый вход 18 устройства, третий столбец состояний после поступления фронта импульса второй импульсной

5 периодической последовательности в течение периода первой периодической последовательности.

Работа устройства начинается с поступления фронтов импульсов на входы 18 и 19 устройства.

Рассмотрим первый случай (линия 23 на фиг. 2), когда фронт импульса первой периодической последовательности, поступающей на первый вход 16 устройства, опережает фронт импульса второй периодической последовательности, поступающей на второй вход 19 устройства Линия 23 указывает изменение состояния D-триггеров. После поступления фронта на первый вход 18 устройства на прямом выходе первого D-триггера 1 устанавливается 1, на его прямом выходе формируется фронт первого измерительного импульса. Вследствие этого выходное состояние логического элемента 2И-НЕ 7 устанавливается в 1 и напряжение на выходе 22 устройства стремится к уровню Ui (Ui + Ui)/2 UL Если же в течение одного периода первой импульсной последовательности, поступающей на первый вход 18 устройства, на второй вход 19 устройства поступит фронт импульса второй импульсной последовательности, то на выходе второго D-триггера 2 установится 1. Таким образом, на первый и четвертый вход логического элемента 4И-НЕ 11 добавляются 1 к имеющимся двум логическим 1, поступающим с инверсных выходов третьего 3 и четвертого 4 D-триггеоов на второй и третий входы. В результате на выходе логического элемента 4И-НЕ установится О, который через инвертор 12 в.виде логической 1 будет подан на первые 9 и вторые 10 входы логических элементов. На выходах этих элементов появится О, который поступит на установочные входы первого и второго 2 D-триггероа и вернет их в начальное состояние. В результате окончится формирование первого измерительного импульса на выходе D-триггера 1. Также в начальное состояние вернутся и выходы ёсех логических элементов: логический элемент 4И-НЕ 11 - в 1, инвертор - в О, логические элементы 2И-2ИЛИ-НЕ 9 и 10 - в 1. Выходное напряжение на выходе 22 устройства при периодическом повторении импульсных последовательностей будет равно сумме начального напряжения U0 и усредненного во времени Т первого измерительного импульса

ивых1 Ui + U0 + (Ui - U0)

Uycp (Ui - U0) //360° (Ui - U6) йЯЙ/Г (Ui-U0)27T,

где Т - длительность первого измерительного импульса.

Во втором случае, когда фронт импульса второй периодической последовательности, поступающей на второй вход 19 устройства, опережает фронтимпульса второй периодической последовательности поступающей

на первый вход 18 устройства (линия 24 на. фиг. 3). В результате этого после поступления фронта на второй вход 19 устройства на прямом выходе второго D-триггера устанав- ливается 1 и на его прямом выходе формируется фронт второго измерительного импульса. Вследствие этого выходное состояние логического элемента 2И-НЕ 8 устанавливается в 1, а на второй вход 21

фильтра 14 низких частот через инвертор 13 поступает сигнал логического О. Напряжение на выходе 22 устройства стремится к уровню UBO (Uo + U0)/2 U0. Если же в течение периода второй импульсной последовательности на первый вход 18 устройства поступит фронт импульса первой импульсной последовательности, то на выходе первого D-триггера 1 установится Г. Возврат устройства в начальное состояние

происходит так же, как было в первом случае, и формирование второго измерительного импульса заканчивается.

Напряжение на выходе 22 устройства в этом случае равно разности начального напряжения Квых и усредненного во времени второго измерительного импульса

ивых2 Ui + U0 - (Ui - U0) т2 , где Г2 -длительность второго измерительного импульса.

Алгоритмы работы устройства (фиг.2 и 3)

описывают все возможные состояния D- триггеров устройства и последовательность переходов при равенстве периодов двух входных импульсных периодических последовательностей, поступающих на входы устройства,

Алгоритм работы устройства (фиг. 2) применим для случая, когда фронт первой импульсной периодической последовательности опережает фронт второй импульсной периодической последовательности, и для случая (фиг. 3), когда фронт второй импульсной периодической последовательности опережает фронт первой импульсной периодической последовательности.

Третий случай, когда в начальном состоянии на прямых выходах первого 1 и третьего 3 D-триггеров установлена 1. Такое состояние (линия 25 на фиг. 2) возникает

тогда, когда за период второй импульсной периодической последовательности на первый вход 18 устройства поступит более двух импульсов первой импульсной периодической последовательности. Фронтимпульса,

поступающий на первый вход 18 устройства, не изменит состояний D-триггеров и состояния устройства в целом. Выходное напряжение устройства останется равным ивых1 Ui. На информационный вход второго D-триггера 2 поступит О с выхода логического элемента 2И-НЕ 5, на первый и второй вход которого поступают 1 с прямых выходов первого 1 и третьего D-триггеров. С поступлением фронта от импульса второй импульсной периодической последовательности состояние второго D-триггера 2 не изменится. Зато этот фронт поступает на третий вход логического элемента 2И- 2ИЛИ-НЕ 9, на четвертый вход которого поступает 1 с прямого выхода D-триггера З, и высокий уровень (1) устанавливает на выходе логического элемента 2И+2ИЛИ-НЕ 9 О, который поступает на установочный вход D-триггера 1 и переводит его в состояние О. ВТОРОЙ фронт импульса первой импул ь- сной периодической последовательности, поступая на счетные входы D-триггеров 1 и 3, запишет в D-триггер 1 - 1 и D-триггер З запишет О, которые имеются на их информационных входах. Фронт импульса второй импульсной периодической последовательности запишет о D-триггер 2 1 и устройст- во вернется в исходное начальное состояние, как в первом случае. Во время этих переходов на один из входов логического элемента 2И-НЕ 7 поступает О с инверсных выходов D-триггеров 1 и 3, таким образом напряжение на выходе устройства будет постоянно и равно УРЫХ/З Ui.

Четвертый случай (линия 26 на фиг. 2) отличается от третьей тем, что D-триггеры 2 и 4 находятся в состоянии 1. Первый фронт первой импульсной периодической последовательности, поступающей на первый вход 18 устройства, не изменит состояние D- триггеров 1 и 3, так как на их информационные входы поступают на D-триггер 1 - с выхода логического элемента 2И-НЕ 6, на выходы которого поступают 1 с прямых выходов D-триггеров 2 и 4; на D-триггер З - с прямого выхода D-триггера 1. Высокий уровень ( 1), поступая на третий вход логического элемента 2И-2ИЛИ-НЕ 10, установит на его выходе О, так как на его четвертый вход поступит 1 с выхода D- триггера 4. Низкий уровень с выхода логического элемента 2И-2ИЛИ-НЕ 10 поступит на установочный вход D-триггера 2 и установит на его прямом выходе О. Первый фронт второй импульсной периодической последовательности, поступая на счетные входы D-триггера 2 и 4, записывает на их прямых выходах информацию, поступающую на их информационные входы : D-триггер 2 - 1, D-триггер 4 - О. Второй фронт первой импульсной периодической последовательности, поступая на счетные входы D-триггеров 1 и 3, запишет в них 1 и О соответственно, и устройство вернется в начальное состояние, как в первом случае. В течение времени этих переходов на выходе устройства будет оставаться напряжение, равное Увыхо Uo, так как сигнал логического О, поступающий на один из входов логического элемента 2И-НЕ 8 с инверсных выходов D-триггеров 2 и 4, поддерживает на выходе логического элемента 2И-НЕ 8 сигнал 1, который инвертируется инвертором

13 и поступает на второй вход 21 фильтра низких частот.

Из алгоритмов работы устройства следует, что до вхождения устройства в основной рабочий цикл измерения сдвига фаз

напряжение на выходе устройства имеет одно из значений U0 или Ui и не изменяется до тех пор, пока в течение периода любой из двух входных импульсных периодических последовательностей, поступающих на входы данного устройства, периоды обоих импульсных периодических последовательностей не будут равны.

Формула изобретения

Устройство для измерения сдвига фаз,

содержащее первый и второй D-триггеры, первый логический элемент 2И-НЕ и сумматор с фильтром нижних частот, выход которого является выходом устройства, о т л и чающееся тем, что, с целью повышения достоверности измерения сдвига фаз, дополнительно введены третий и четвертый D-триггеры, второй, третий и четвертый логические элементы 2И-НЕ, первый и второй

логические элементы 2И-2ИЛИ-НЕ, первый и второй инверторы, логический элемент 4И-НЕ. а суматор с фильтром нижних частот выполнен из первого и второго резисторов и конденсатора, причем первый и второй

входы сумматора с фильтром нижних частот соединены с его выходом через соответственно первый и второй резисторы, а конденсатор подсоединен к указанному выходу и клемме Земля, а также прямой выход первого D-триггера соединен с первым входом первого логического элемента 2И-НЕ, информационным входом третьего D-триггера и первым входом логического элемента 4И- НЕ, а инверсный выход третьего D-триггера

соединен с первым входом третьего логического элемента 2И-НЕ и вторым входом логического элемента 4И-НЕ, прямой выход второго D-триггера соединен с информационным входом четвертого D-триггера, первым входом второго логического элемента 2И-НЕ и третьим входом логического элемента 4И-НЕ, инверсный выход четвертого D-триггера соединен с первым входом чет- .ертого логического элемента 2И-НЕ и четвертым входом логического эле :нта

4И-НЕ, выход которого через первый инвертор соединен с первым и вторым входами первого и второго логических элементов 2И-2ИЛИ-НЕ, выход первого логического элемента 2И-2ИЛИ-НЕ соединен с устано- вочным входом первого D-триггера, а выхо/д второго логического элемента 2И-2ИЛИ- НЕ - с установочным входом второго D- триггера, информационный вход которого соединен с выходом первого логического элемента 2И-НЕ, а информационный вход первого D-триггера - с выходом второго логического элемента 2И-НЕ, выход третьего логического элемента 2И-НЕ соединен с первым входом сумматора с фильтром ниж- них частот, второй вход которого соединен с выходом четвертого логического элемента 2И-НЕ через второй инвертор, инверсный выход первого D-триггера соединен с вторым входом третьего логического элемента

2И-НЕ, прямой выход третьего D-триггера соединен с вторым входом первого логического элемента 2И-НЕ и четвертым входом первого логического элемента 2И-2ИЛИ- НЕ, иноерсный выход третьего D-триггера соединен с вторым входом четвертого логического элемента 4И-НЕ и с первым входом третьего логического элемента 2W-HE, прямой выход четвертого D-триггера соединен с четвертым входом логического элемента 2И-2ИЛИ-НЕ и вторым входом второго логического элемента 2И-НЕ, а счетные входы первого и третьего D-триггеров соединены с третьим входом второго логического эле- 2И-2ИЛИ-НЕ и являются первым входом устройства, счетные входы второго и четвертого D-триггеров соединены с третьим входом первого логического элемента 2И-2ИЛИ-НЕ и являет ся вторым входом устройства.

Jv

bf&i

/ДОТУХ

T oo

Q3

7 7

Q31 1 00

.2

0.5

Фиг. з

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для приема последовательного кода | 1977 |

|

SU705494A1 |

| Устройство для контроля напряжения | 1989 |

|

SU1613964A1 |

| Широтно-импульсный модулятор для управления усилителем мощности | 1989 |

|

SU1718375A1 |

| Устройство для синхронизации преобразователей,включаемых параллельно на общую нагрузку | 1985 |

|

SU1319182A1 |

| Электропривод | 1990 |

|

SU1830611A1 |

| Преобразователь экстремумов периодического сигнала в постоянное напряжение | 1989 |

|

SU1674002A1 |

| Реверсивный распределитель импульсов | 1981 |

|

SU953728A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОТКАЗОВ В ШАГОВОМ ЭЛЕКТРОПРИВОДЕ | 1992 |

|

RU2037264C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

Изобретение относится к области радиоизмерительной техники и может быть использовано в системах фазовой автоподстройки частоты в качестве фазового детектора. Целью изобретения является повышение достоверности измерения сдвига фаз двух импульсных периодических последовательностей. Из возможных состояний работы устройства следует, что до вхождения устройства в основной рабочий цикл измерения сдвига фаз напряжение на выходе устройства имеет одно из возможных значений и не изменяется до тех пор, пока в течение периода любой из двух входных импульсных периодических последовательностей, поступающих на входы данного устройства периоды обоих импульсных периодических последовательностей не будут равны. 3 ил.

0.5 .

| Титце У., Шенк | |||

| Полупроводниковая схемотехника; М.: Мир, 1983, с | |||

| Катодная лампа с внешним подогревом | 1923 |

|

SU493A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Частотно-фазовый дискриминатор | 1975 |

|

SU625300A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-23—Публикация

1988-01-25—Подача