Изобретение относится к регулирующим и управляющим системам, в частности к устройствам для электрического контроля, и может быть использовано в системах диагностирования сложных технических обьектов, не имеющих точной математической модели.

Целью изобретения является повышение точности обработки информации за счет учета характера изменения анализируемых параметров.

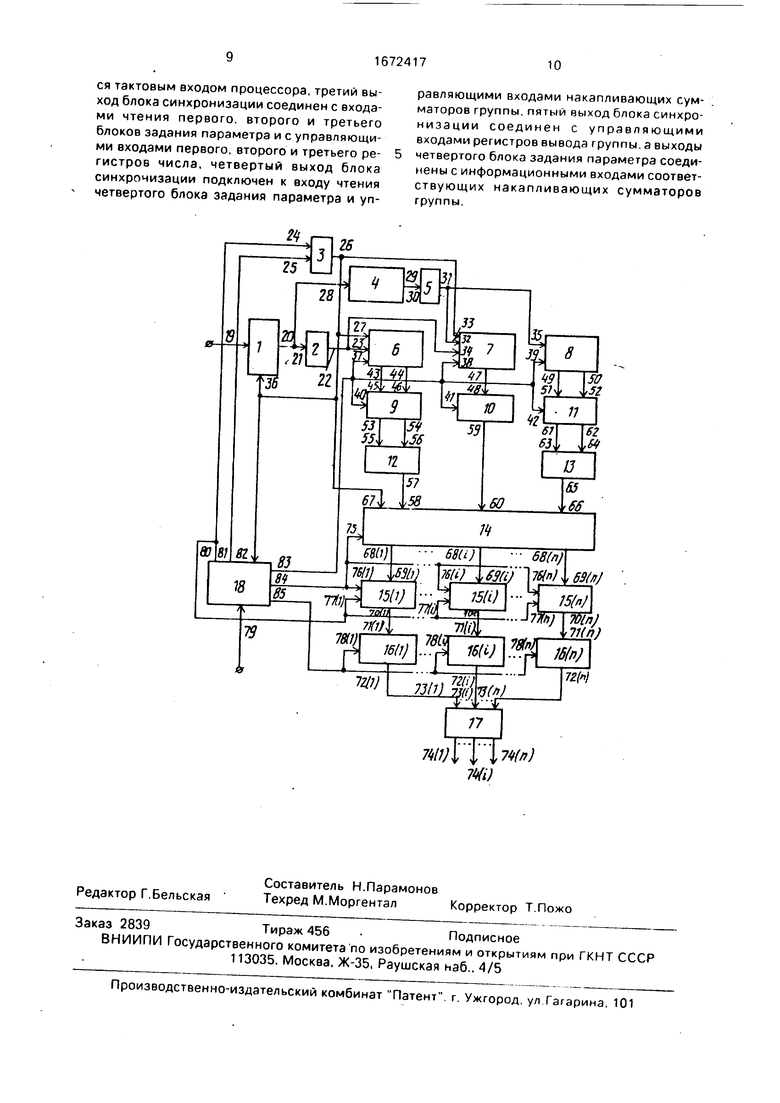

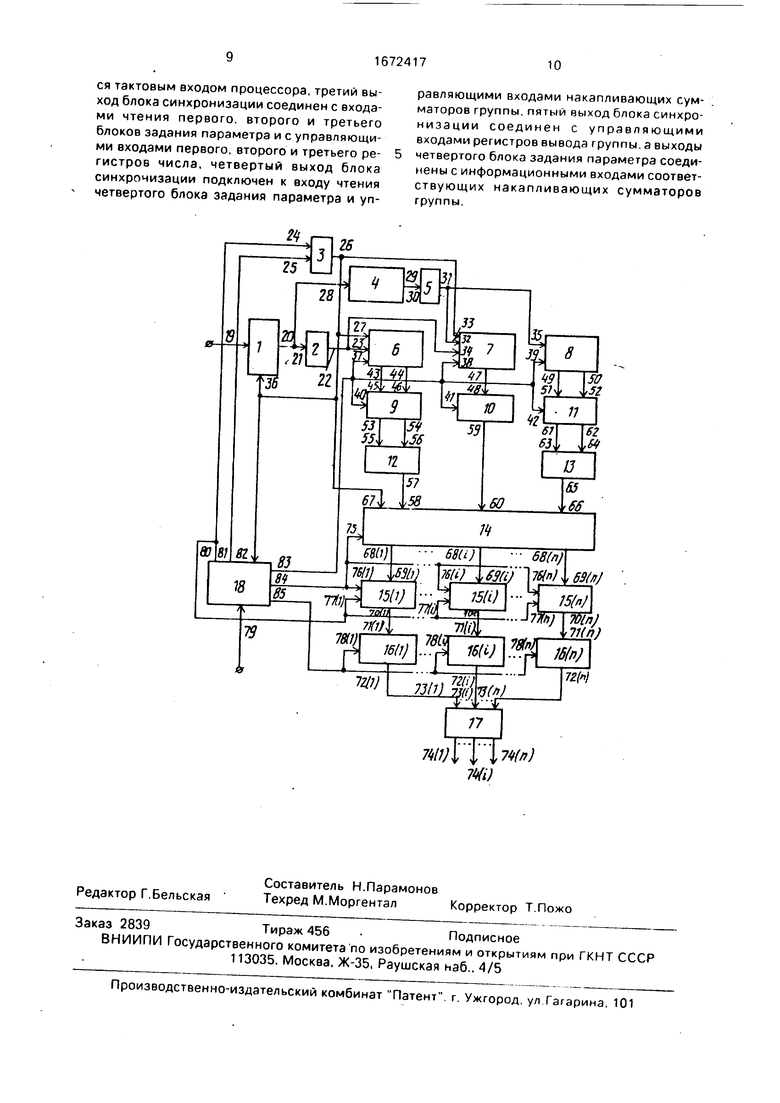

На чертеже представлена функциональная схема предлагаемого процессора.

Процессор содержит мультиплексор 1. первый регистр 2 адреса, счетчик 3 адреса, блок 4 дифференцирования, второй регистр 5 адреса, с первого по третий блоки 6-8 задания параметров (блоки памяти), выполненные в виде блоков памяти, с первого по третий регистры 9-11 числа, первый 12 и второй 13 блоки вычитания, четвертый блок 14 задания параметра (блок памяти), выполненный в виде блока памяти, группу накапливающих сумматоров 15, группу регистров 16 вывода, блок 17 выделения максимума, блок 18 синхронизации. На чертеже также обозначены информационный вход 19 и выход 20 мультиплексора 1. вход 21 и виход 22 регистра 2, второй адресный вход 23 блока 6, установочный 24 и счетный 25 входы и выход 26 счетчика 3, первый адресный вход 27 блока 6, вход 28 и выход 29 блока 4, вход 30 и выход 31 регистра 5, первый 32, второй 33 и третий 34 адресные входы блока 7. адресный вход 35 блока 8, управляющий вход 36 мультиплексора 1. входы 37-39 разрешения обращения блоков 6-8 соответственно, управляющие входы регистров 9-11 соответственно, первый 43 и второй 44 выходы блока 6, первый 45 и второй 46 информационные входы регистра 9, выход 47 блока 7, информационный вход 48 регистра 10, первый 49 и второй 50 выходы блока 8, первый 51 и второй 52 информационные входы регистра 11, первый 53 и второй 54 выходы регистра 9, первый 55 и второй 56

ё

О

ю

1

входы и выход 57 блока 12, второй адресный вход 58 блока 14, выход 59 регистра 10, третий адресный вход 60 блока 14, первый 61 и второй 62 выходы регистра 11, первый 63 и второй 64 входы и выход 65 блока 13, четвертый адресный вход 66 блока 14, первый адресный вход 67 блока 14, выходы 68(1)-68(п) блока 14, информационные входы 69(1)- 69(п) и выходы 70(1)-70(п) соответствующих сумматоров 15(1)-15(п), информационные входы 71(1)-71(п) и выходы 72(1)- 72(п) соответствующих регистров 16(1)-16(п), входы 73(1)-73(п) и выходы 74((п) блока 17, вход 75 разрешения обращения блока 14, управляющие 76(1)-76(п) и установочные 77(1)-77(п) входы соответствующих сумматоров 15(1)-15(п), управляющие входы 78(1)- 78(п) соответствующих регистров 16(1)-16(п), тактовый вход 79, первый 80 и второй 81 выходы, вход 82 пуска, третий 83, четвертый 84 и пятый 85 выходы блока 18.

Мультиплексор 1 предназначен для no- очередного подключения анализируемых параметров к своему выходу.

Первый регистр 2 адреса предназначен для записи адресного кода, поступающего с выхода 20 мультиплексора 1.

Счетчик 3 адреса предназначен для формирования адресного кода, поступающего на входы 27, 32, 67, 36, 82 блоков 6, 7, 14, 1, 18 соответственно.

Блок 4 дифференцирования предназначен для формирования кода, пропорционального производной сигнала, поступающего с выхода 20 мультиплексора 1.

Второй регистр 5 адреса предназначен для записи адресного кода, поступающего с выхода 29 блока 4.

Первый блок 6 памяти предназначен для хранения кодов функций принадлежности числовых значений входного сигнала лингвистическим терм-значениям.

Второй блок 7 памяти предназначен для хранения кодов наименьших терм-значений, для которых входные числовые значения сигнала и его производной имеют ненулевые степени принадлежности.

Третий блок 8 памяти предназначен для хранения кодов функций принадлежности числовых значений производной входного сигнала лингвистическим терм-значениям.

Регистры 9-11 числа предназначены для записи кодов, поступающих с блоков 6-8 соответственно.

Первый 12 и второй 13 блоки вычитания предназначены для получения разности сигналов на своих первых и вторых входах.

Четвертый блок 14 памяти предназначен для хранения весовых коэффициентов,

выражающих ассоциативную связь между лингвистическими терм-значениями, характеризующими входные параметры, а также направление и скорость их изменения с одной стороны и каждой из п возможных альтернатив с другой стороны.

Накапливающие сумматоры 15(1)-15(п) предназначены для получения суммарных по всем входным параметрам весовых коэф0 фициентов для каждой из п альтернатив.

Регистры 16(1)-16(п) вывода предназначены для записи суммарных весовых коэффициентов для каждой из п альтернатив. Блок 17 предназначен для принятия ди5 агностического решения, состоящего в выборе наибольшего суммарного весового коэффициента.

Блок 18 синхронизации предназначен для тактирования работы процессора.

0Лингвистический процессор для обработки диагностической информации работает следующим образом.

Первый 6, второй 7 и четвертый 14 блоки памяти имеют страничную организацию.

5 Номер страницы первого 6, второго 7 и четвертого 14 блоков памяти определяется содержимым счетчика 3 адреса, т.е. номером входного параметра. Номер ячейки в странице для первого блока 6 памяти определя0 ется содержимым регистра 2 адреса, на который заносится числовое значение входного параметра.

Слово первого блока 6 памяти состоит из М полей, где М - число лингвистических

5 значений (терм-значений), имеющих ненулевую степень принадлежности к числовому значению входной переменной. Предполагается, что числовое значение параметра может одновременно относиться к двум

0 терм-значениям. Степень его принадлежности к остальным терм-значениям близка к нулю или равна ему. Таким образом, М 2. Содержимое каждого из двух полей представляет собой значение степени принэд5 лежности входного числового значения к соответствующему терм-значению.

В третьем блоке 8 памяти в каждой ячейке хранятся степени принадлежности числового значения сигнала на выходе 29 блока

0 4 дифференцирования к лингвистическим терм:значениям, характеризующим направление и скорость изменения входного сигнала. Слово третьего блока 8 памяти также состоит из двух полей, содержащих ненуле5 вые степени принадлежности

Номер ячейки в странице для второго блока 7 памяти определяется содержимым регистров 2 и 5 адреса. В каждой ячейке блока 7 хранятся наименьшие терм-значения, для которых числовое значение входного параметра и числовое значение, характеризующее направление и скорость его изменения, имеют ненулевую степень принадлежности. Слово второго блока 7 памяти содержит четыре разряда, причем пер- вые два из них представляют собой наименьшее терм-значение с ненулевой степенью принадлежности для числового значения параметра, а вторые два разряда - наименьшее терм-значение для числового значения, характеризующего направление и скорость изменения этого параметра. Так, если на выходе блока 7 имеется код 0000, это значит, что для данного числового значения параметра и числового значения, ха- рактеризующего направление и скорость его изменения, минимальными терм-значениями с ненулевой степенью принадлежности являются первые терм-значения При коде 0001 для числового значения парамет- ра минимальное ненулевое терм-значение - первое (00), а для числового значения, характеризующего направление и скорость изменения этого параметра минимальным ненулевым терм-значением является вто- рое терм-значение (01), при коде 0100 - соответственно - второе и первое и т.п. При этом имеется в виду, что терм-значения упорядочены согласно их смысловому значению. Например, для входного значения вибрации терм-значения упорядочены следующим образом: очень низкая, низкая, средняя, высокая, очень высокая, а терм-значения, характеризующие изменения входного значения, упорядочены так: уменьшается быстро, уменьшается, не меняется, растет, растет быстро.

С помощью четвертого блока 14 памяти осуществляется ассоциативная связь между полученными терм-значениями параметров и терм-значениями их изменения, с одной стороны, и каждой из п возможных альтернатив (диагностических решений), с другой стороны. Связь наблюдаемых терм-значений с каждой альтернативой выражается в виде весового коэффициента. Каждая ячейка блока 14 разбита на п зон, в каждой из которых содержится значение весового коэффициента, выражающего связь наблюдаемой входной ситуации с соответствующей альтернативой. Адрес ячейки в странице определяется состояниями второго 58,третьего 60 и четвертого 66 адресных входов.

В первом такте по сигналу с выхода 80 блока 18 в счетчик 3 адреса заносится число Р. Значение на выходе счетчика 3 уменьшается в каждом такте на единицу при наличии единичного сигнала на входе 25 счетчика. В этом же такте устанавливаются в нулевое состояние все сумматоры 15. Выходное значение счетчика 3 адреса поступает на входы 27, 32, 67 соответственно первого 6, второго

7и четвертого 14 блоков памяти с выбором страницы, а также на вход 82 блока 18 и на вход 36 мультиплексора 1 с пропуском значения Р-го параметра через мультиплексор 1. С выхода 20 мультиплексора 1 значение Р-го параметра поступает на вход 28 блока 4 дифференцирования и на вход 21 первого регистра 2 адреса. При наличии 1 на управляющем входе регистра 2 в него записывается новое состояние. Если на его упрапляющем входе О, то осуществляется хранение предыдущего состояния. Это же относится и ко второму регистру 5 адреса, к регистрам 9-11 числа и к регистрам 16 вывода. Для первого 2 и второго 5 регистров адреса управляющий вход соединен с шиной логической единицы С выхода 22 .первого регистра 2 адреса информация поступает на вход 23 блока 6 памяти с выбором соответствующей ячейки и на вход 34 блока 7 памяти.

В этом же такте продифференцированный входной сигнал с выхода 29 блока 4 поступает на вход 30 второго регистра 5 адреса. С выхода 31 регистра 5 информация поступает на вход 33 блока 7 памяти, выбирая совместно с информацией на входе 33 соответствующую ячейку, и на вход 35 блока

8памяти, также выбирая соответствующую ячейку Выбором ячеек в блоках 6-8 заканчивается первый такт

Во втором такте по сигналу с выхода 83 блока 18 синхронизации, поступающему на входы 37-39 блоков 6-8 памяти и на входы 40-42 регистров 9-11, происходит чтение информации из блоков 6-8 памяти соответственно на регистры 9-11. На регистре 9 - ненулевые значения функций принадлежности числового значения входного параметра к термам Р-й лингвистической переменной. На регистре 11 - ненулевые значения функций принадлежности числового значения, характеризующего направление и скорость изменения этого входнггс параметра, к лингвистическим термам изменения входного значения. На регистре 10 - меньшие из терм-значений, имеющих ненулевую степень принадлежности к входному значению и ненулевую степень принадлежности к изменению входного значения. Информация с выходов 53, 54 регистра 9 поступает соответственно на входы 55, 56 блока 12, а с выходов 61, 62 регистра 11 - соответственно на входы 63, 64 блока 13. Смысл преобразования, осуществляемого блоком 12, состоит в следующем. На входц55, 56 блока 12 поступают две ненулевые функции принадлежности числового значения входного

параметра к термам Р-й лингвистической переменной. Знак разности, получаемой на выходе 57 блока 12, сообщает о том, к какому из двух термов А и В (фиг. 6) входное числовое значение параметра принадлежит в большей степени. Величина этой разности однозначно определяет положение числового значения входного параметра относительно центра этого терм-значения. Работа блока 13 полностью аналогична работе блока 12. С выхода 57 блока 12, выхода 59 регистра 10, выхода 65 блока 13 информация поступает соответственно на входы 58, 60, 66 блока 14 памяти, определяя соответствующую ячейку в странице.

В третьем такте по сигналу с выхода 84 блока 18, поступающему на вход 75 блока 14 памяти и на входы 76 сумматоров 15, осуществляется чтение информации, поступающей из блока 14 памяти на сумматоры 15. где она суммируется с ранее накопленной в сумматорах 15.

В четвертом такте по сигналу с выхода 81 блока 18, поступающему на вход 25 счетчика 3, осуществляется вычитание единицы из его содержимого, т.е. переход к следующему входному параметру и, соответственно, к следующей странице блоков 6, 7, 14 памяти. Содержимое счетчика 3 поступает на вход 82 блока 18, где производится его анализ на нуль. При неравенстве содержимого счетчика 3 нулю управление передается второму такту, т.е. происходит ввод и анализ следующего параметра. Если содержимое счетчика 3 равно нулю, т.е. анализ всех параметров произведен, управление передается пятому такту.

В пятом такте по сигналу с выхода 85 блока 18 информация из сумматоров 15 записывается в соответствующие регистры

16.В регистры 16 записываются суммарные весовые коэффициенты, выражающие степень связи состояний всех Р входных параметров, представленных в виде лингвистических терм-значений, с соответствующей альтернативой. С выходов 72 регистров 16 суммарные весовые коэффициенты поступают на входы 73 блока

17.Блок 17 выявляет максимальный из поступающих на его входы 73 суммарных весовых коэффициентов. Блок 17 имеет разрядность выхода, равную числу своих входов, На том разрядном выходе 74, где суммарный весовой коэффициент будет наибольшим, появится сигнал логической единицы, что означает выбор соответствующей альтернативы.

Формула изобретения Лингвистический процессор для обработки диагностической информации, содержащий мультиплексор, первый регистр

адреса, счетчик адреса, четыре блока задания параметра, три регистра числа и блок синхронизации, отличающийся тем, что, с целью повышения точности обработки информации, в него введены последова0 тельно соединенные блок дифференцирования и второй регистр адреса, первый и второй блоки вычитания, последовательно соединенные группа накапливающих сумматоров, группа регистров вывода, блок вы5 деления максимума, выходы которого являются диагностическими выходами процессора, информационный вход которого подключен к информационному входу мультиплексора, выход которого соединен с вхо0 дом блока дифференцирования и входом первого регистра адреса, выход которого соединен с вторым адресным входом первого блока задания параметров и с третьим адресным входом второго блока задания па5 раметра, выход которого соединен с информационным входом второго регистра числа, выход которого соединен с третьим адресным входом четвертого блока задания параметра, первый и второй выходы первого

0 блока задания параметра соединены соответственно с первым и вторым информационными входами первого регистра числа, первый и второй выходы которого соединены соответственно с первым и вторым вхо5 дами первого блока вычитания,выход которого соединен с вторым адресным входом четвертого блока задания параметра, выход второго регистра адреса соединен с вторым адресным входом второго блока за0 дания параметра и адресным входом третьего блока задания параметра, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами третьего регистра числа,

5 первый и второй выходы которого соединены соответственно с первым и вторым входами второго блока вычитания, выход которого соединен с четвертым адресным входом четвертого блока задания парамет0 ра, первый выход блока синхронизации соединен с установочными входами накапливающих сумматоров группы и установочным входом счетчика адреса, второй выход блока синхронизации соединен со

5 счетным входом счетчика адреса, выход которого соединен с первыми адресными входами первого, второго и четвертого блоков задания параметра, с адресным входом мультиплексора и входом пуска блока синхронизации, тактовый вход которого является тактовым входом процессора, третий выход блока синхронизации соединен с входами чтения первого, второго и третьего блоков задания параметра и с управляющими входами первого, второго и третьего регистров числа, четвертый выход блока синхронизации подключен к входу чтения четвертого блока задания параметра и управляющими входами накапливающих сумматоров группы, пятый выход блока синхро- низации соединен с управляющими входами регистров вывода группы, а выходы четвертого блока задания параметра соединены с информационными входами соответствующих накапливающих сумматоров группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический процессор | 1985 |

|

SU1305704A1 |

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

Изобретение относится к регулирующим и управляющим системам. Цель изобретения - повышение точности обработки информации за счет учета характера изменения анализируемых параметров. Для этого в процессор введен блок дифференцирования, что позволяет определить скорость изменения анализируемого параметра групп накапливающих сумматоров и регистров ввода, которые вместе с решающим блоком определяют наиболее вероятную гипотезу принадлежности параметра. 1 ил.

7«//;Г | 17 / ;

М)

| Логический процессор | 1985 |

|

SU1305704A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-08-23—Публикация

1989-05-24—Подача