Изобретение относится к вычис- лительной технике и может быть использовано для реализации логических алгоритмов, заданных в лингвистической форме.

Цель изобретения - расширение функциональных возможностей процессора за счет реализации алгоритмов, заданных в лингвистической форме с произвольной комбинацией входных и выходных переменных.

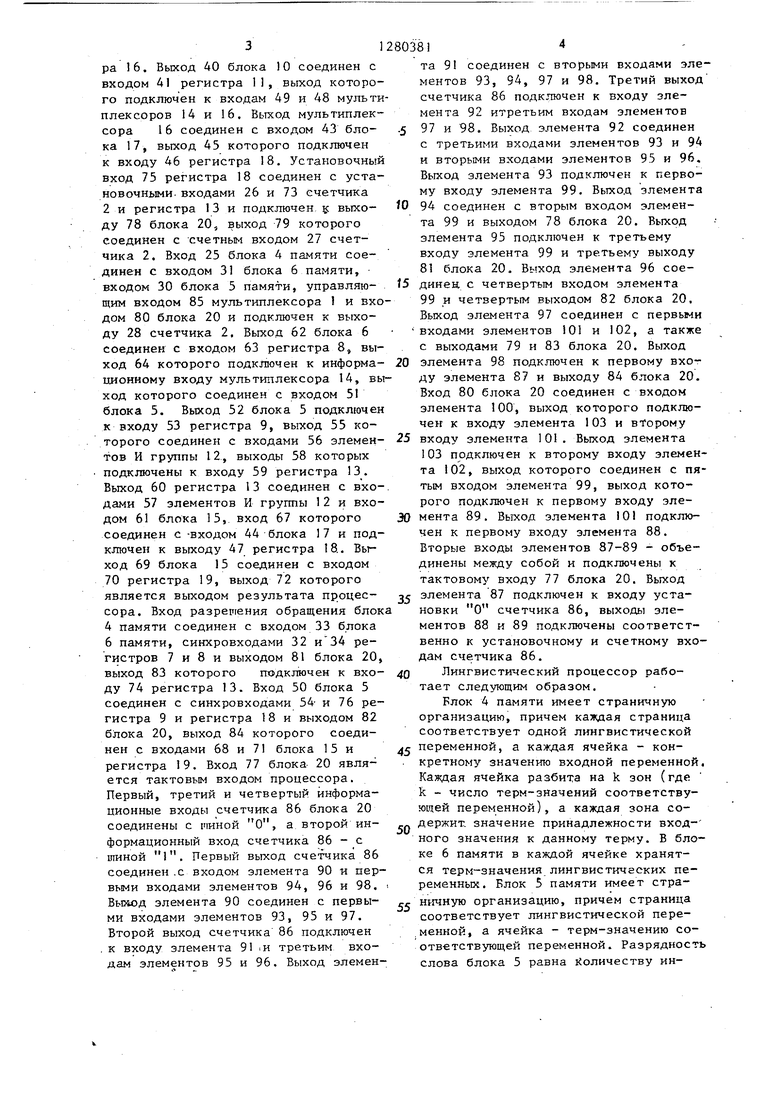

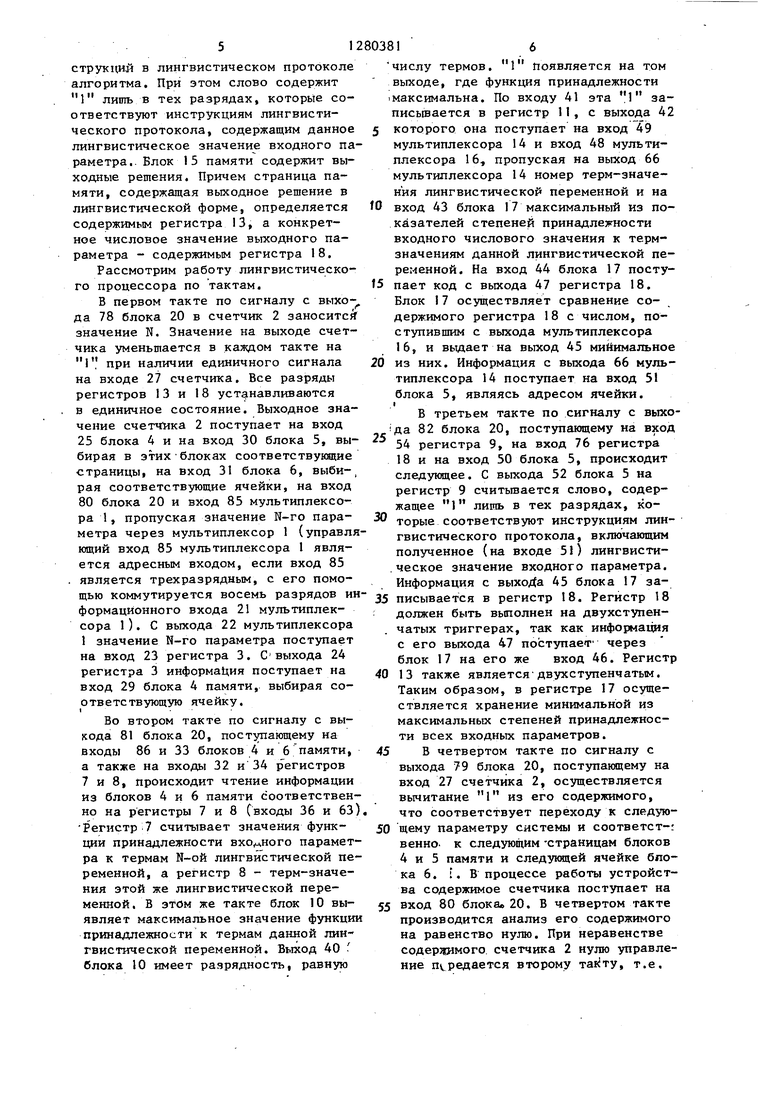

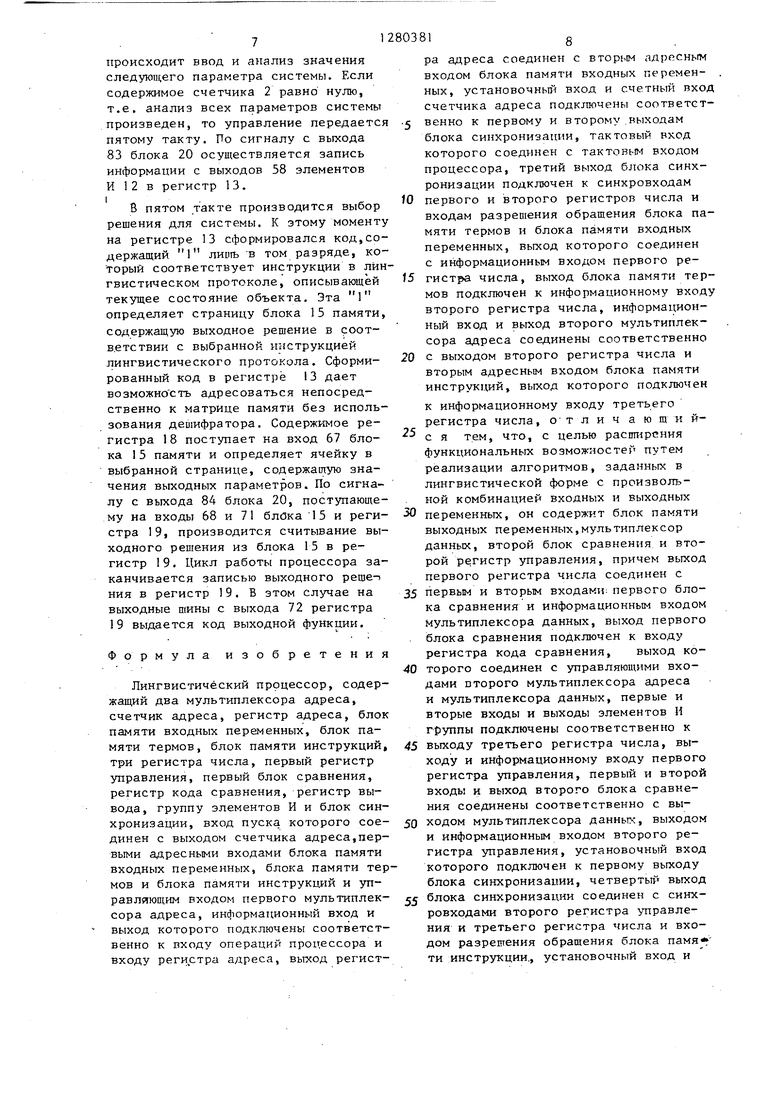

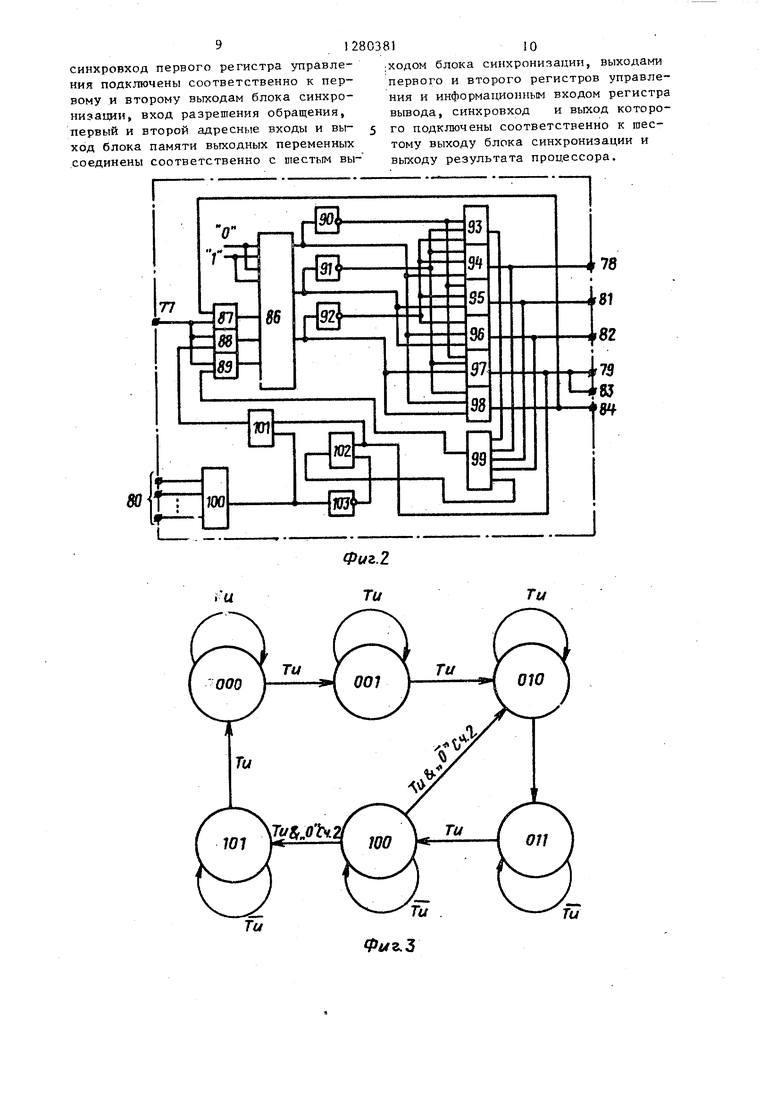

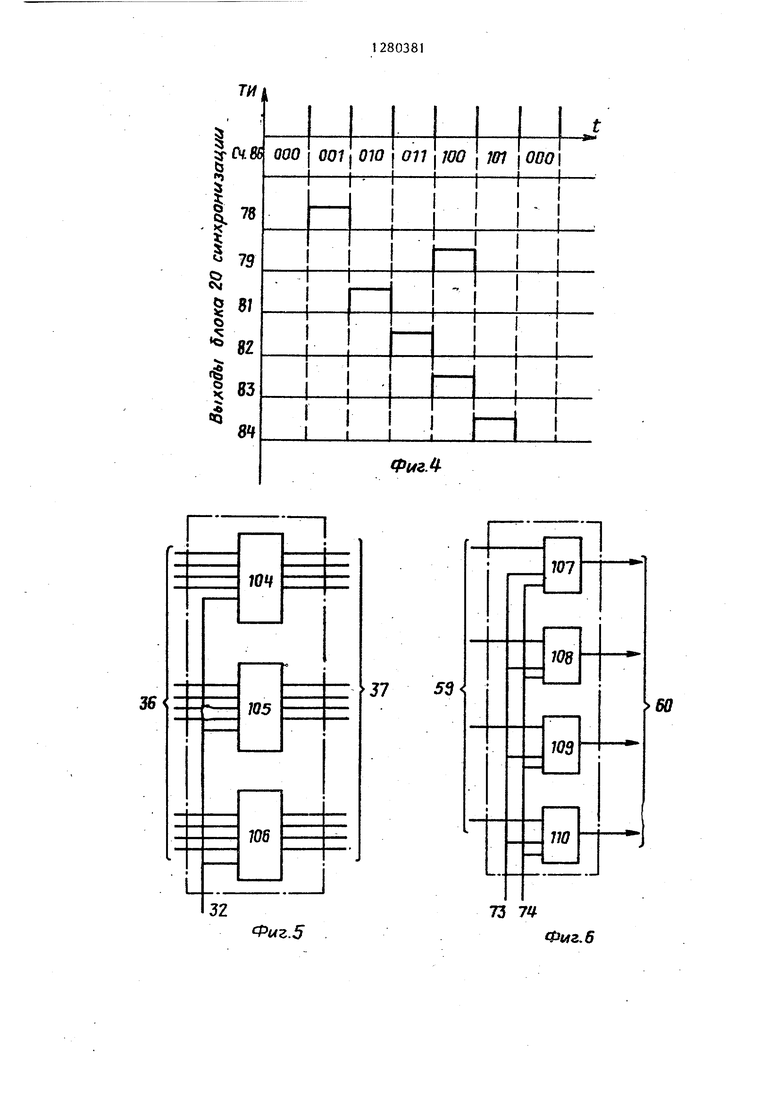

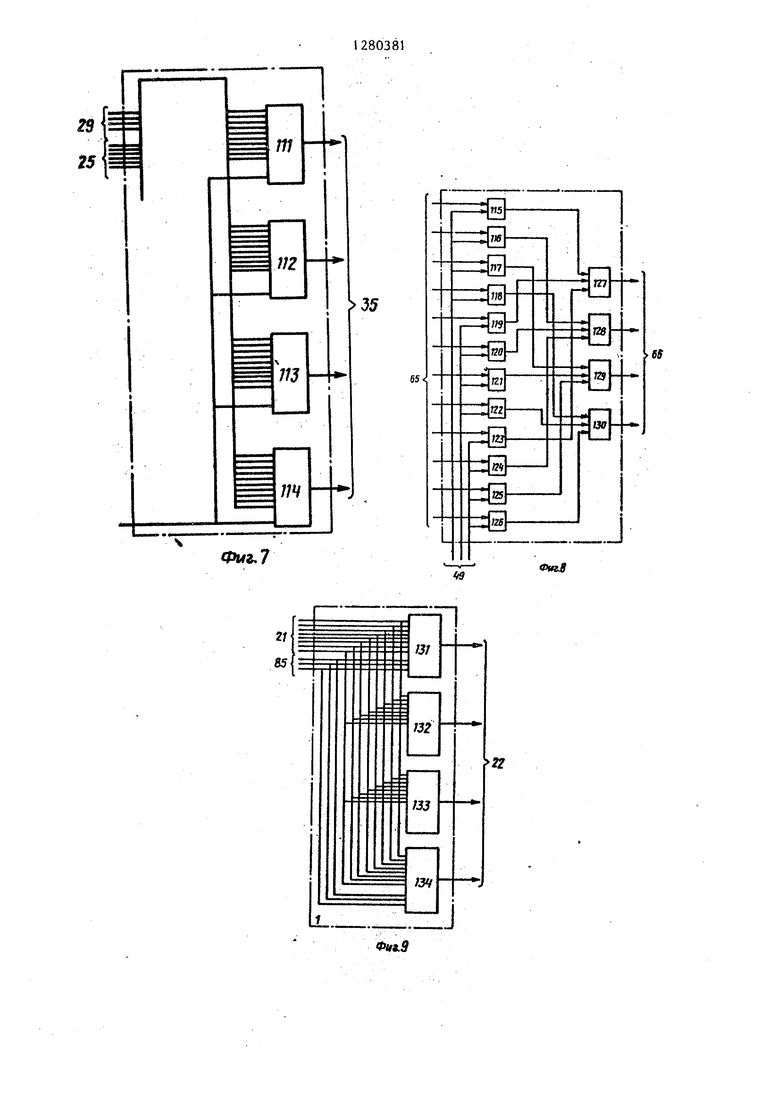

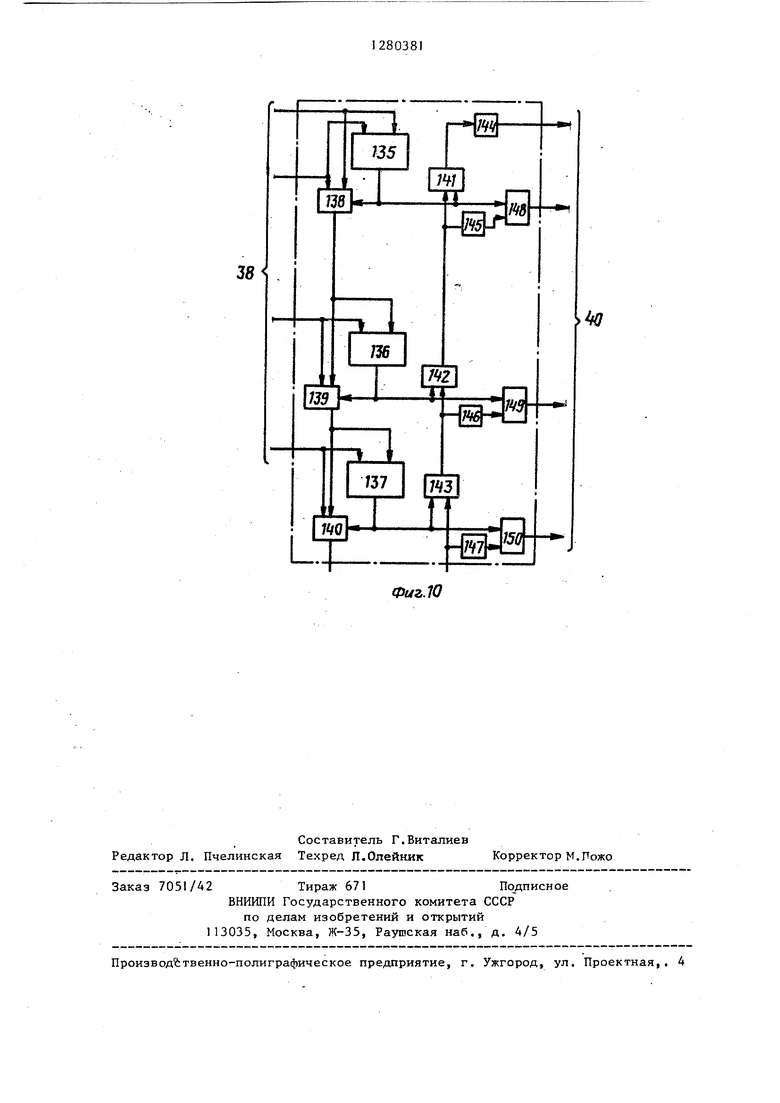

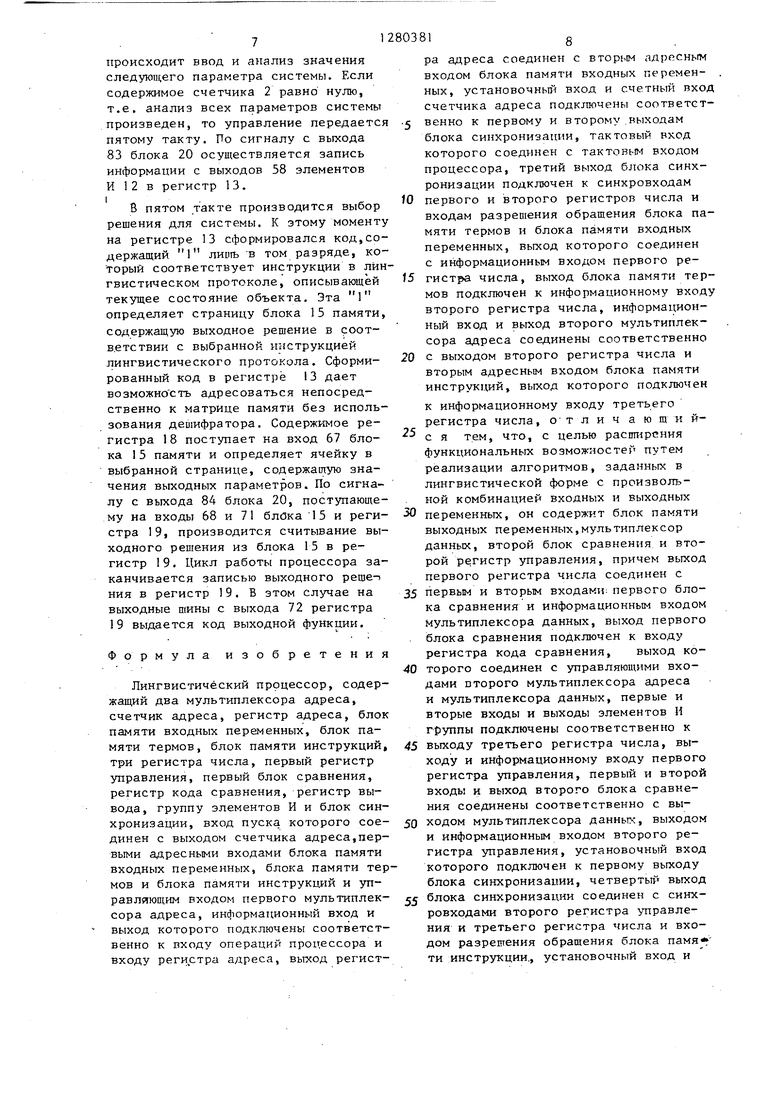

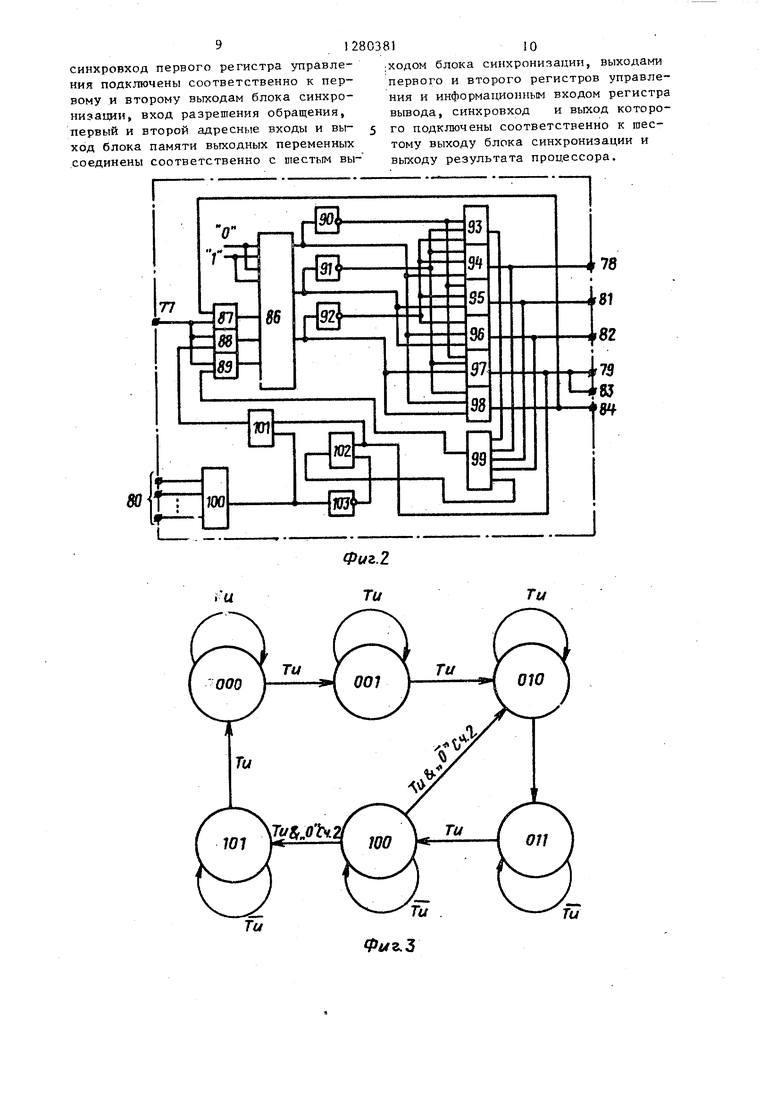

На фиг. 1 представлена функциональная схема процессора; на фиг. 2- сх,ема блока синхронизации; на фиг.З- граф переходов счетчика блока синхронизации; на фиг. 4 - временная диаграмма работы блока синхронизации , на фиг. 5 - схема регистра адреса, первого, второго и третьего регистров числа, регистра кода сравнения и регистра вывода; -на фиг. 6 - схема регистров управления, на фиг. 7 - схема блоков памяти входных переменных, термов и инструкций; на фиг. 8 - схема мультиплексора данных и второго мультиплексора адреса; на фиг. 9 - схема первого мультиплексора адреса; на фиг. 10 - схема первого блока сравнения.

Устройство содержит первый мультиплексор 1 адреса, счетчик 2 адреса, регистр 3 адреса, блок 4 памяти .:входных переменных, блок 5 памяти инструкций, блок 8 памяти термов, первый и второй 8 регистры числа, третий регистр 9 числа, первый блок 10 сравнения, регистр 11 кода сравнения, группу 12 элементов И, первый регистр 13 управления, второй мультиплексор 14 адреса, блок 15 памяти выходных переменных, мультиплек--- сор 16 данных, второй блок 17 сравнения, второй регистр 18 управления, регистр 19 вывода, блок 20 синхронизации, информационный вход 21 и выход 22 мультиплексора I, вход 23 и выход 24 регистра 3, первый адресный вход 25 блока 4, установочный 26 и

to

40 блока 10, вход 41 гистра 11, первый 43 ды блока 17, выход 4 формационный вход 46

5 гистра 18, управляющ типлексора 16, управ мультиплексора 14, у 50 (вход разрешения рой адресный вход 51 ка 5, информационный вход 54 и выход 55 р вые 56 и вторые 57 в 58 элементов И групп онный вход 59 и выхо

13, первый адресный 15, выход 62 блока 6 вход 63 и выход 64 р формационный вход 65 типлексора 14, второ

67, управляющий вход шения обращения) и вы информационный вход 71 и выход 72 регист ный вход 73 и синхро ра 13, установочный ровход 76 регистра 1 77, первый 78 и втор вход 80 пуска, трети 82, пятый 83 и тесто

30 ка 20, управляющий в плексор а 1 , счетчик третий элементы И третий элементы НЕ 9 девятый элементы И 9

35 и второй 100 элемент 101 и одиннадцать 1 четвертый элемент НЕ четырехразрядные рег регистров 7-9 числа,

40 регистра II и регист ры 107-110 регистров разрядные запоминающ 114 блоков 4-6 памят 115-126 и элементы И

45 типлексоров 14 и 16, мультиплексоры 131-1 ра 1, схемы 135-137 таторы 138-14.0, элем 143, элементы НЕ 144

счетный 27 входы и выход 28 счетчика 50 148-150 блока 10.

2, второй адресньй вход 29 блока 4, первый адресный вход 30 блока 5, адресный вход 31 блока 6, синхровход 32 регистра 7, вход 33 разрещения обращения блока 6, синхровход 34 регистра 8, выход 35 блока 4, информационный вход 36 и выход 37 регистра 7, входы 38 блока 10, информационный вход 39 мультиплексора 16, выход

to

2803812

40 блока 10, вход 41 и выход 42 регистра 11, первый 43 и второй 44 входы блока 17, выход 45 блока 17, информационный вход 46 и выход 47 ре5 гистра 18, управляющий вход 48 мультиплексора 16, управляющий вход 49 мультиплексора 14, управляющий вход 50 (вход разрешения обращения),второй адресный вход 51 и выход 52 блока 5, информационный вход 53, синхро- вход 54 и выход 55 регистра 9, первые 56 и вторые 57 входы и выходы 58 элементов И группы 12, информационный вход 59 и выход 60 регистра

13, первый адресный вход 61 блока 15, выход 62 блока 6, информационный вход 63 и выход 64 регистра 8, информационный вход 65 и выход 66 мультиплексора 14, второй адресный вход

67, управляющий вход 68 (вход разрешения обращения) и выход 69 блока 15, информационный вход 70, синхровход 71 и выход 72 регистра 19, установочный вход 73 и синхровход .74 регистра 13, установочный вход 75 и синхровход 76 регистра 18, тактовый вход 77, первый 78 и второй 79 выходы, вход 80 пуска, третий 81, четвертый 82, пятый 83 и тестой 84 выходы бло30 ка 20, управляющий вход 85 мульти- плексор а 1 , счетчик 86, первый - третий элементы И 87-89, первый - третий элементы НЕ 90-92, четвертый - девятый элементы И 93-98, первый 99

35 и второй 100 элементы ИЛИ, десятый 101 и одиннадцать 102 Элементы И-и четвертый элемент НЕ 103 блока 20, четырехразрядные регистры 104-106 регистров 7-9 числа, регистра 3,

40 регистра II и регистра 19, триггеры 107-110 регистров 13 и 18, одноразрядные запоминающие блоки 111- 114 блоков 4-6 памяти, элементы И 115-126 и элементы ИЛИ 127-130 муль45 типлексоров 14 и 16, одноразрядные мультиплексоры 131-134 мультиплексо- ра 1, схемы 135-137 сравнения коммутаторы 138-14.0, элементы ИЛИ 141- 143, элементы НЕ 144-147, элементы

Информационным входом лингвистического процессора является вход 21 мультиплексора 1, выход 22 которого подключен к входу 23 регистра 3. Вы- 55 ход 24 регистра 3 соединен с входом 29 блока 4 памяти. Выход 35 блока 4 памяти подключен к входу 36 регистра 7, выход которого подключен к входу 38 блока 10 и входу 39 мультиппексота 9 соединен с вторыми входами элементов 93, 94, 97 и 98. Третий выход счетчика 86 подключен к входу элемента 92 итретьим входам элементов 97 и 98. Выход элемента 92 соединен с третьими входами элементов 93 и 9А и вторыми входами элементов 95 и 96. Выход элемента 93 подключен к первому входу элемента 99. Выход элемента 94 соединен с вторым входом элемента 99 и выходом 78 блока 20. Выход элемента 95 подключен к третьему входу элемента 99 и третьему выходу 81 блока 20. Выход элемента 96 соединен с четвертым входом элемента 99 и четвертым выходом 82 блока 20, Выход элемента 97 соединен с первыми входами элементов 101 и 102, а также с выходами 79 и 83 блока 20. Выход

-5

fO

pa 16. Выход 40 блока 10 соединен с входом 41 регистра 11, выход которого подключен к входам 49 и 48 мультиплексоров 14 и 16. Выход мультиплексора 16 соединен с входом 43 блока 17, выход 45 которого подключен к входу 46 регистра 18. Установочный вход 75 регистра 18 соединен с установочными, входами 26 и 73 счетчика 2 и регистра 13 и подключен g: выходу 78 блока 20., выход 79 которого соединен с счетным входом 27 счетчика 2. Вход 25 блока 4 памяти соединен с входом 31 блока 6 памяти, входом 30 блока 5 памяти, управляющим входом 85 мультиплексора 1 и входом 80 блока 20 и подключен к выходу 28 счетчика 2, Выход 62 блока 6 соединен с входом 63 регистра 8, выход 64 которого подключен к информа- 20 элемента 98 подключен к первому вхо- ционному входу мультиплексора 14, вы- ду элемента 87 и выходу 84 блока 20. ход которого соединен с входом 51 блока 5. Выход 52 блока 5 подключен к входу 53 регистра 9, выход 55 которого соединен с входами 56 элемен- 25 входу элемента 101. Выход элемента тов И группы 12, выходы 58 которых 103 подключен к второму входу элемен15

Вход 80 блока 20 соединен с входом элемента 100, выход которого подключен к входу элемента 103 и второму

подключены к входу 59 регистра 13. Выход 60 регистра 13 соединен с вхо-. дами 57 элементов И группы 12 и входом 61 блока 15, вход 67 которого соединен с -входом 44 блока 17 и подключен к выходу 47 регистра 18.. Выход 69 блока 15 соединен с входом 70 регистра 19, выход 72 которого является выходом результата процессора. Вход разрешения обращения блока 4 памяти соединен с входом 33 блока 6 памяти, синхровходами 32 и 34 регистров 7 и 8 и выходом 81 блока 20, выход 83 которого подключен к входу 74 регистра 13. Вход 50 блока 5 соединен с синхровходами 54- и 76 регистра 9 и регистра 18 и выходом 82 блока 20, выход 84 которого соединен с входами 68 и 7 блока 15 и регистра 19. Вход 77 блока 20 является тактовым входом процессора. Первый, третий и четвертый информационные входы счетчика 86 блока 20 соединены с имной О, а второй информационный вход счетчика 86 - с шиной 1. Первый выход счетчика 86 соединен ,с входом элемента 90 и первыми входами элементов 94, 96 и 98. Выход элемента 90 соединен с первыми входами элементов 93, 95 и 97. Второй выход счетчика 86 подключен к входу элемента 91 .и третьим входам элементов 95 и 96. Выход элемен803814

та 9 соединен с вторыми входами элементов 93, 94, 97 и 98. Третий выход счетчика 86 подключен к входу элемента 92 итретьим входам элементов 97 и 98. Выход элемента 92 соединен с третьими входами элементов 93 и 9А и вторыми входами элементов 95 и 96. Выход элемента 93 подключен к первому входу элемента 99. Выход элемента 94 соединен с вторым входом элемента 99 и выходом 78 блока 20. Выход элемента 95 подключен к третьему входу элемента 99 и третьему выходу 81 блока 20. Выход элемента 96 соединен с четвертым входом элемента 99 и четвертым выходом 82 блока 20, Выход элемента 97 соединен с первыми входами элементов 101 и 102, а также с выходами 79 и 83 блока 20. Выход

-5

fO

20 элемента 98 подключен к первому вхо- ду элемента 87 и выходу 84 блока 20. 25 входу элемента 101. Выход элемента 103 подключен к второму входу элемен15

элемента 98 подключен к первому вхо- ду элемента 87 и выходу 84 блока 20. входу элемента 101. Выход элемента 103 подключен к второму входу элеменВход 80 блока 20 соединен с входом элемента 100, выход которого подключен к входу элемента 103 и второму

та 102, выход которого соединен с пятым входом элемента 99, выход которого подключен к первому входу эле0 мента 89. Выход элемента 101 подключен к первому входу элемента 88. Вторые входы элементов 87-89 - объединены между собой и подключены к тактовому входу 77 блока 20. Выход

элемента 87 подключен к входу установки О счетчика 86, выходы элементов 88 и 89 подключены соответственно к установочному и счетному входам счетчика 86.

0 Лингвистический процессор работает следующим образом.

Рлок 4 памяти имеет страничную организацию, причем каждая страница соответствует одной лингвистической

переменной, а каждая ячейка - кон- . кретному значению входной переменной. Каждая ячейка разбита на k зон (где k - число терм-значений соответствующей переменной), а каждая зона содержит, значение принадлежности вход- ного значения к данному терму. В блоке 6 памяти в каждой ячейке хранятся терм-значения лингвистических переменных. Блок 5 памяти имеет страничную организацию, причем страница соответствует лингвистической переменной, а ячейка - терм-значению соответствующей переменной. Разрядность слова блока 5 равна Количеству ин0

5

струкций в лингвистическом протоколе алгоритма. При этом слово содержит 1 лишь в тех разрядах, которые соответствуют инструкциям лингвистического протокола, содержащим данное лингвистическое значение входного параметра.. Блок 15 памяти содержит выходные решения. Причем страница памяти, содержащая выходное решение в лингвистической форме, определяется содержимым регистра 13, а конкретное числовое значение выходного параметра - содержимым регистра 18.

Рассмотрим работу лингвистического процессора по тактам.

В первом такте по сигналу с выхо- да 78 блока 20 в счетчик 2 заносите значение N. Значение на выходе счетчика уменьшается в каждом такте на при наличии единичного сигнала

Г

20 из них. Информация с выхода 66 мультиплексора 14 поступает на вход 51

блока 5, являясь адресом ячейки,

I

В третьем такте по сигналу с выхо

на входе 27 счетчика. Все разряды регистров 13 и 18 устанавливаются в единичное состояние. Выходное значение счетчика 2 поступает на вход „1да 82 блока 20, поступающему на вход 25 блока 4 и на вход 30 блока 5, вы- 25 с/. п .. ic.54 регистра 9, на вход 76 регистра 18 и на вход 50 блока 5, происходит следующее, С выхода 52 блока 5 на регистр 9 считьшается слово, содержащее 1 лишь в тех разрядах, которые соответствуют инструкциям лингвистического протокола, включающим полученное (на входе 51) лингвистическое значение входного параметра. Информация с выхоДа 45 блока 17 забирая в этих блоках соответствующие страницы, на вход 31 блока 6, выби-, рая соответствующие ячейки, на вход 80 блока 20 и вход 85 мультиплексора 1, пропуская значение N-ro параметра через мультиплексор 1 (управляющий вход 85 мультиплексора 1 является адресным входом, если вход 85 является трехразрядным, с его помо54 регистра 9, на вход 76 регистра 18 и на вход 50 блока 5, происходит следующее, С выхода 52 блока 5 на регистр 9 считьшается слово, содержащее 1 лишь в тех разрядах, которые соответствуют инструкциям лингвистического протокола, включающим полученное (на входе 51) лингвистическое значение входного параметра. Информация с выхоДа 45 блока 17 защью коммутируется восемь разрядов ин- 35 писывается в регистр 18, Регистр 18

формацйонного входа 21 мультиплексора 1), С выхода 22 мультиплексора 1 значение N-ro параметра поступает на вход 23 регистра 3, С выхода 24 регистра 3 информация поступает на вход 29 блока 4 памяти, выбирая соответствующую ячейку.

Во втором такте по сигналу с вы- кода 81 блока 20, поступающему на входы 86 и 33 блоков 4 и 6 памяти, а также на входы 32 и 34 регистров 7 и 8, Происходит чтение информации Из блоков 4 и 6 памяти соответственно на регистры 7 и 8 (входы 36 и 63), Регистр 7 считывает значения функции принадлежности входного параметра к термам N-ой лингвистической переменной, а регистр 8 - терм-значения этой же лингвистической переменной. В этом же такте блок 10 выявляет максимальное значение функции принадлежности к термам данной лингвистической переменной. Выход 40 блока 10 имеет разрядность, равную

должен быть выполнен на двухступен- . чатых триггерах, так как информахдая с его выхода 47 поступает через блок 17 на его же вход 46, Регистр

40 13 также является двухступенчатым. Таким образом, в регистре 17 осуществляется хранение минимальной из максимальных степеней принадлежности всех входных параметров,

45 В четвертом такте по сигналу с выхода 79 блока 20, поступающему на вход 27 счетчика 2, осуществляется вычитание 1 из его содержимого, что соответствует переходу к следую50 щему параметру системы и соответст-: венно. к следующим -страницам блоков 4 и 5 памяти и следующей ячейке бпо- ка 6, , В процессе работы устройства содержимое счетчика поступает на

55 вход 80 блока. 20, В четвертом такте производится анализ его содержимого на равенство нулю. При неравенстве содердамого счетчика 2 нулю управление передается второму , т.е.

803816

числу термов, 1 Появляется на том выходе, где функция принадлежности 1максимальна. По входу 41 эта 1 за- письшается в регистр 1I, с выхода 42

5 которого она поступает на вход 49 мультиплексора 14 и вход 48 мультиплексора 16, пропуская на выход 66 мультиплексора 14 номер терм-значения лингвистической переменной и на

to вход 43 блока 17 максимальный из показателей степеней принадлежности входного числового значения к терм- значениям данной лингвистической переменной. На вход 44 блока 17 посту15 пает код с выхода 47 регистра 18, Блок I7 осуществляет сравнение содержимого регистра 18 с числом, поступившим с выхода мультиплексора 16, и вьтдает на выход 45 мийимаяьное

20 из них. Информация с выхода 66 мультиплексора 14 поступает на вход 51

блока 5, являясь адресом ячейки,

I

В третьем такте по сигналу с выхо„1да 82 блока 20, поступающему на вход 25 с/. п .. ic.„1да 82 блока 20, поступающему на вход 25 с/. п .. ic.30

54 регистра 9, на вход 76 регистра 18 и на вход 50 блока 5, происходит следующее, С выхода 52 блока 5 на регистр 9 считьшается слово, содержащее 1 лишь в тех разрядах, которые соответствуют инструкциям лингвистического протокола, включающим полученное (на входе 51) лингвистическое значение входного параметра. Информация с выхоДа 45 блока 17 заолжен быть выполнен на двухступен- атых триггерах, так как информахдая с его выхода 47 поступает через блок 17 на его же вход 46, Регистр

13 также является двухступенчатым. Таким образом, в регистре 17 осуществляется хранение минимальной из аксимальных степеней принадлежности всех входных параметров,

В четвертом такте по сигналу с выхода 79 блока 20, поступающему на вход 27 счетчика 2, осуществляется вычитание 1 из его содержимого, что соответствует переходу к следующему параметру системы и соответст-: венно. к следующим -страницам блоков 4 и 5 памяти и следующей ячейке бпо- ка 6, , В процессе работы устройства содержимое счетчика поступает на

вход 80 блока. 20, В четвертом такте производится анализ его содержимого на равенство нулю. При неравенстве содердамого счетчика 2 нулю управление передается второму , т.е.

происходит ввод и анализ значения следующего параметра системы. Если содержимое счетчика 2 равно нулю, т.е. анализ всех параметров системы произведен, то управление передаетс пятому такту. По сигналу с выхода 83 блока 20 осуществляется запись информации с выходов 58 элементов И 12 в регистр 13.

В пятом такте производится выбор решения для системы. К этому момент на регистре 13 сформировался код,содержащий 1 лиигь В том разряде, который соответствует инструкции в лйн гвист гческом протоколе, описывающей текущее состояние объекта. Эта 1 определяет страницу блока 15 памяти содержащую выходное решение в соответствии с выбранной инструкцией лингвистического протокола. Сформированный код в регистре 13 дает возможно сть адресоваться непосредственно к матрице памяти без использования дешифратора. Содержимое регистра 18 поступает на вход 67 блока 15 памяти и определяет ячейку в выбранной странице, содержащую значения выходных параметров. По сигналу с выхода 84 блока 20, поступающему на входы 68 и 71 блока 15 и регистра 19, производится считывание выходного решения из блока 15 в регистр 19. Цикл работы процессора заканчивается записью выходного реше-i НИН в регистр 19. В этом случае на выходные шины с выхода 72 регистра 19 выдается код выходной функции.

Формула изобретения

Лингвистический процессор, содержащий два мультиплексора адреса, счетчик адреса, регистр адреса, блок памяти входных переменных, блок памяти термов, блок памяти инструкций, три регистра числа, первый регистр управления, первый блок сравнения, регистр кода сравнения, регистр вывода, группу элементов И и блок синхронизации, вход пуска которого соединен с выходом счетчика адреса,первыми адресными входами блока памяти входных переменных, блока памяти термов и блока памяти инструкций и управляющим входом первого мультиплексора адреса, информационный вход и выход которого подключены соответственно к входу операций процессора и входу регистра адреса, выход регист5

ра адреса соединен с вторым адресньгм входом блока памяти входных переменных, установочньш вход и счетный вход счетчика адреса подключены соответст5 венно к первому и второму .выходам блока синхронизации, тактовый вход которого соединен с тактовым входом процессора, третий выход блока синхронизации подключен к синхровходам

O первого и второго регистров числа и входам разрешения обращения блока памяти термов и блока памяти входных переменных, выход которого соединен с информационным входом первого ре5 гистра числа, выход блока памяти термов подключен к информационному входу второго регистра числа, информационный вход и выход второго мультиплексора адреса соединены соответственно

0 с выходом второго регистра числа и вторым адресным входом блока памяти инструкций, выход которого подключен

к информационному входу третьего регистра числа, о-т л и ч а ю щ и й- с я тем, что, с целью расширения функциональных возможностей путем реализации алгоритмов, заданных в лингвистической форме с произвольной комбинацией входных и выходных

0 переменных, он содержит блок памяти выходных переменных,мультиплексор данных, второй блок сравнения и второй регистр управления, причем выход первого регистра числа соединен с

5 первым и вторым входами;первого блока сравнения и информационным входом мультиплексора данных, выход первого блока сравнения подключен к входу регистра кода сравнения, выход ко0 торого соединен с управляющими входами второго мультиплексора адреса и мультиплексора данных, первые и вторые входы и выходы элементов Н группы подключены соответственно к

5 выходу третьего регистра числа, выходу и информационному входу первого регистра управления, первый и второй входы и выход второго блока сравнения соединены соответственно с вы0 ходом мультиплексора данных, выходом и информационным входом второго регистра управления, установочный вход которого подключен к первому выходу блока синхронизации, четвертый выход

5 блока синхронизации соединен с синх- ровходами второго регистра управления и третьего регистра числа и входом разрешения обращения блока ти инструкции., установочный вход и

синхровход первого регистра управления подключены соответственно к первому и второму выходам бпока синхронизации, вход разрешения обращения, первый и второй адресные входы и вы;ходом блока синхронизации, выходам первого и второго регистров управл ния и информационным входом регист вывода, синхровход и выход котор го подключены соответственно к шес

ход блока памяти выходных переменных тому выходу блока синхронизации и соединены соответственно с шестым вы- выходу результата процессора.

;ходом блока синхронизации, выходами первого и второго регистров управления и информационным входом регистра вывода, синхровход и выход которого подключены соответственно к

Фмг.2

36

Фмг.5

37 S3

60

73 71

Фиг. 6

23 25

m

//г

7/5

/;v

Фиг,

35

6S

«HeJ

fr

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Логический процессор | 1985 |

|

SU1305704A1 |

| Управляющий процессор | 1984 |

|

SU1290341A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Лингвистический процессор для обработки диагностической информации | 1989 |

|

SU1672417A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1674221A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

Изобретение относится к вьтчис- лительной технике и мож ет быть использовано для реализации логических алгоритмов, заданных в лингвистической форме. Целью изобретения является расширение функциональных возможностей процессора за счет реализации алгоритмов, заданных в лингвистической форме с произвольной комбинацией входных и выходных переменных. Процессор содержит мультиплексоры 1, 14 адреса, счетчик 2 адреса, регистр 3 адреса, блок 4 памяти входных переменных, блок 5 памяти инструкции, блок 6 памяти термов, регистры 7, 8, 9 числа, блоки 10, 17 сравнения, регистр П кода сравнения, группу 12 элементов И, регистры 13, 18 управления, блок 15 памяти выходных переменных,мультиплексор 16 данных, регистр 19 вывода, блок 20 синхронизации. 10 ил. S (Л Фи8.1

ш

Составитель Г.Виталиев Редактор Л. Пчелинская Техред Л.ОлейникКорректор М.Пожо

. в---« -

Заказ 7051/42 Тираж 671По дписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производ (Ьтвенно-полиграфическое предприятие, г. Ужгород, ул. Проектная,. 4

Фиг.10

| Балашов Е.П | |||

| и др | |||

| Многофункциональные регулярные вычислительные структуры | |||

| - М.: Сов | |||

| радио, 1978, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-01-21—Подача