1315995

ментов И 24-27, группь элементов ИЛИ третий мультиплексор 32, и управляе- 28, 29, группу элементов НЕ 30, блок мый триггер 33. 8 ил, 3 табЛ. 31 сравнения нечетных параметров

1

Изобретение относится к цифровой вьгаислительной технике и может быть использовано для машинной реализации алгоритмов обработки нечеткой информации.

Цель изобретения расЕЙирение функциональных возможностей процессора за счет обеспечения возможности реализации им алгоритмов класса состояние объекта - промежуточная переменная - решение.

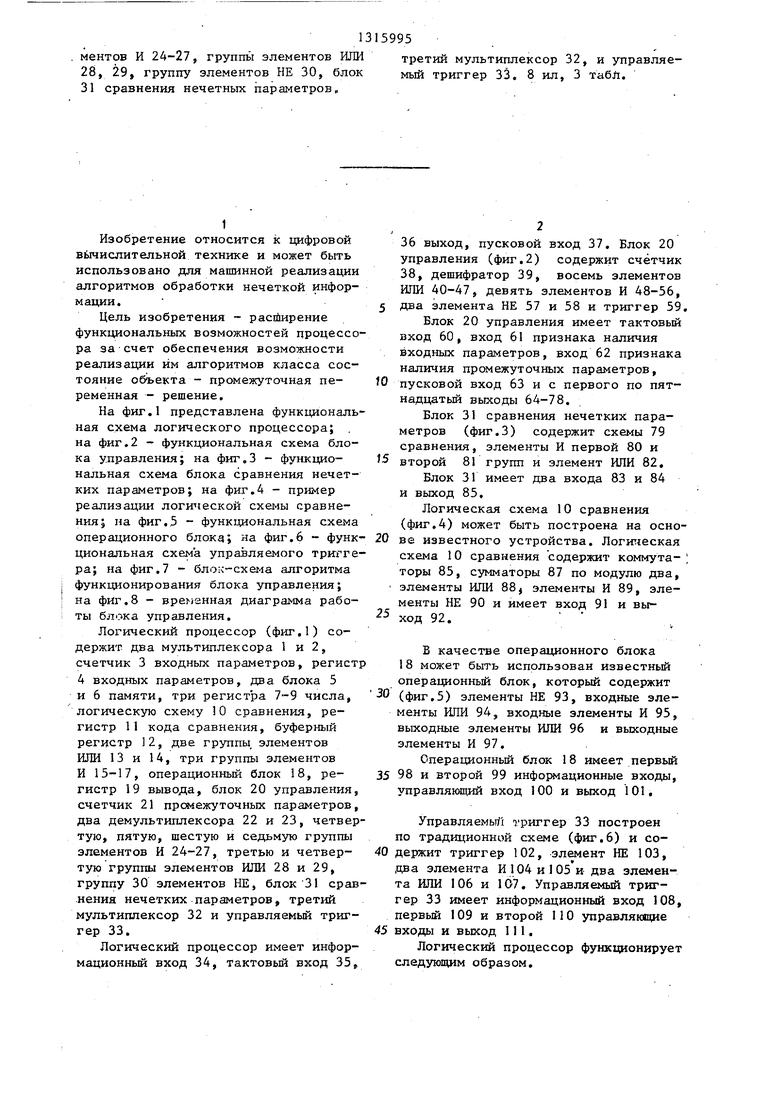

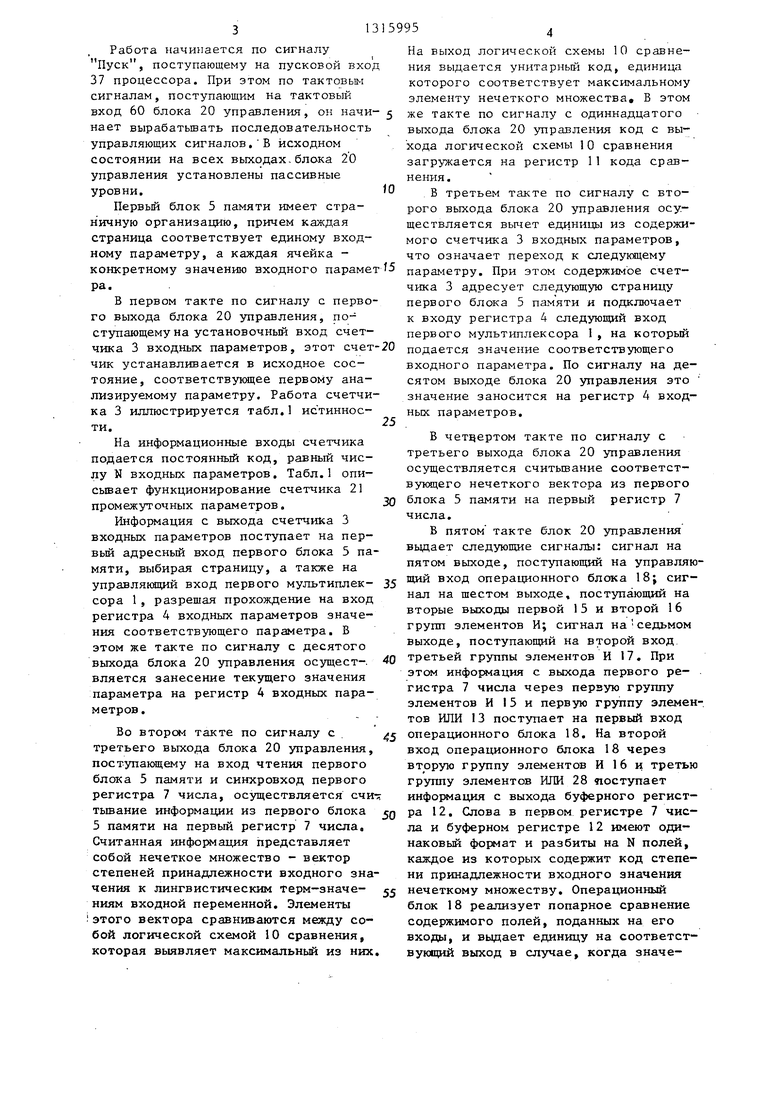

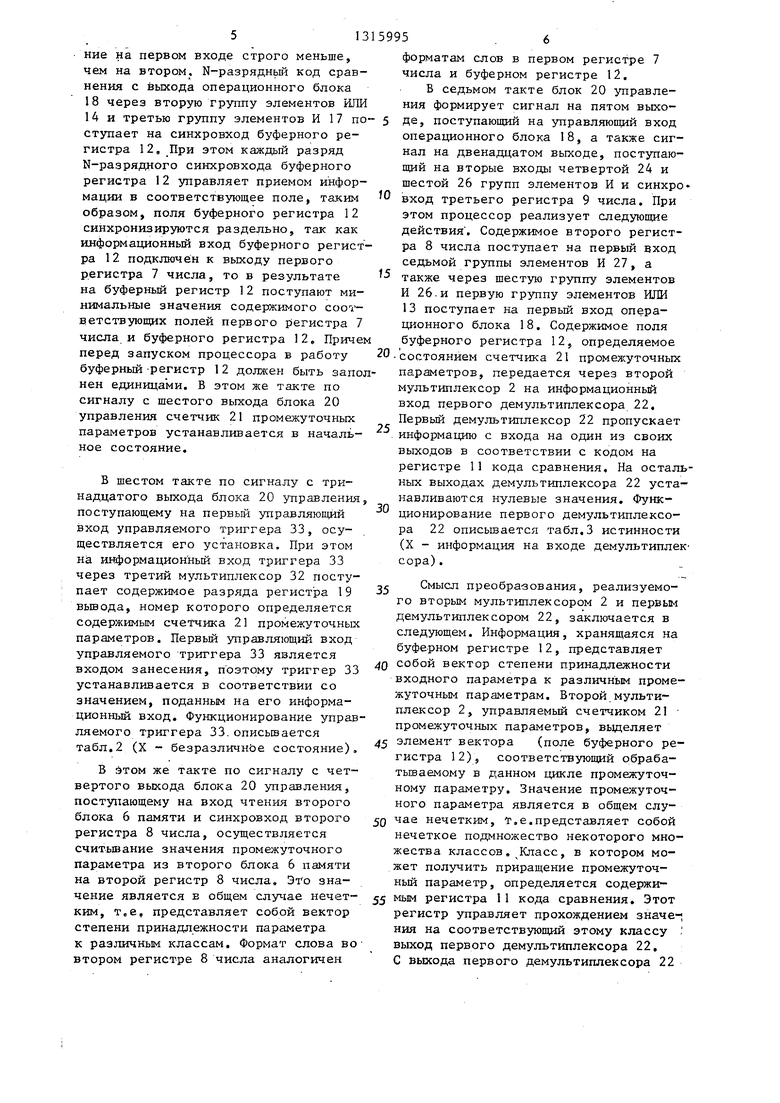

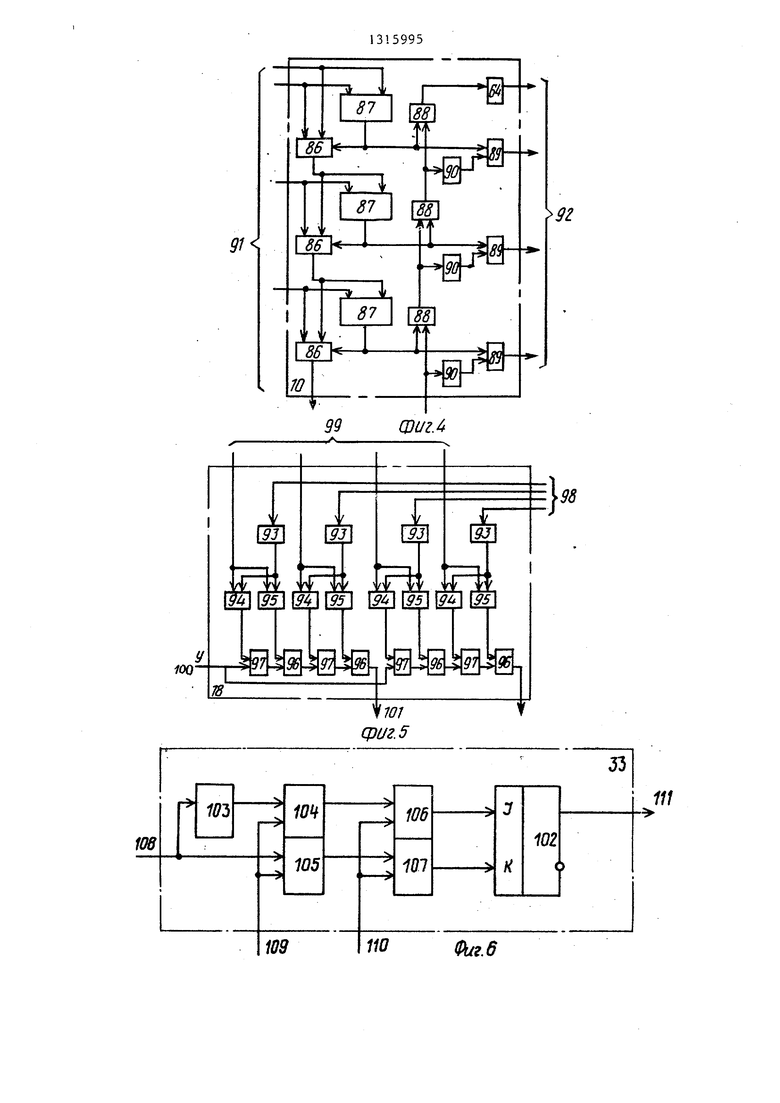

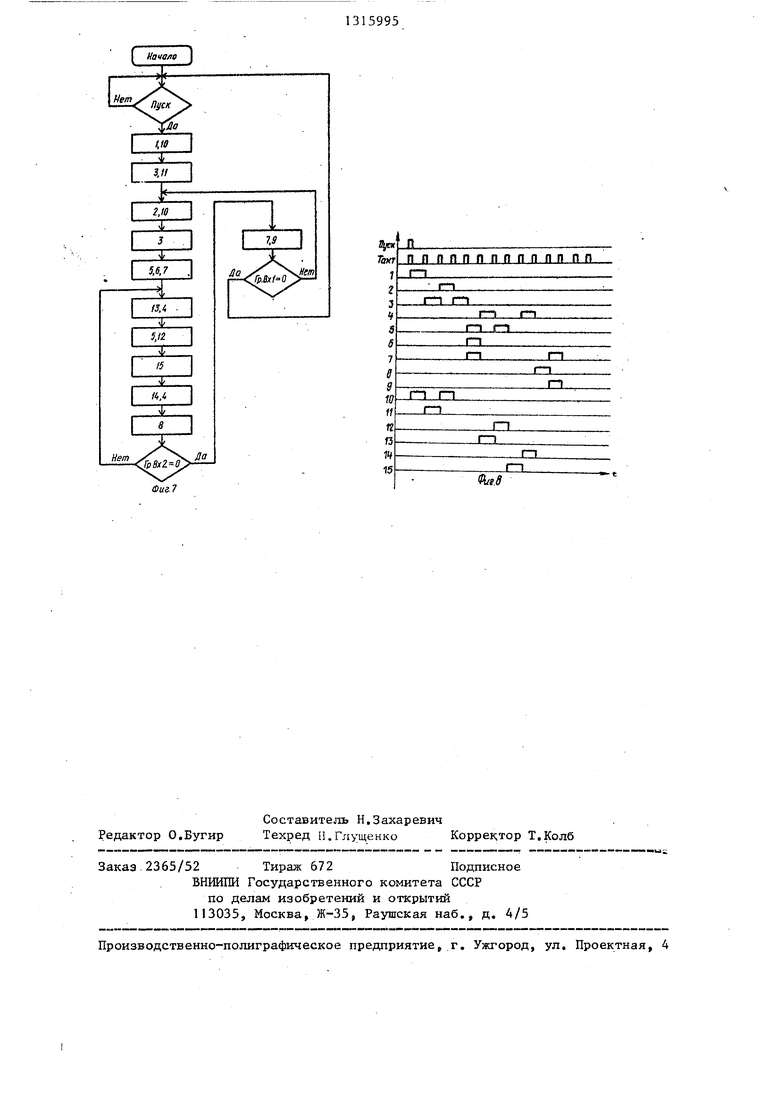

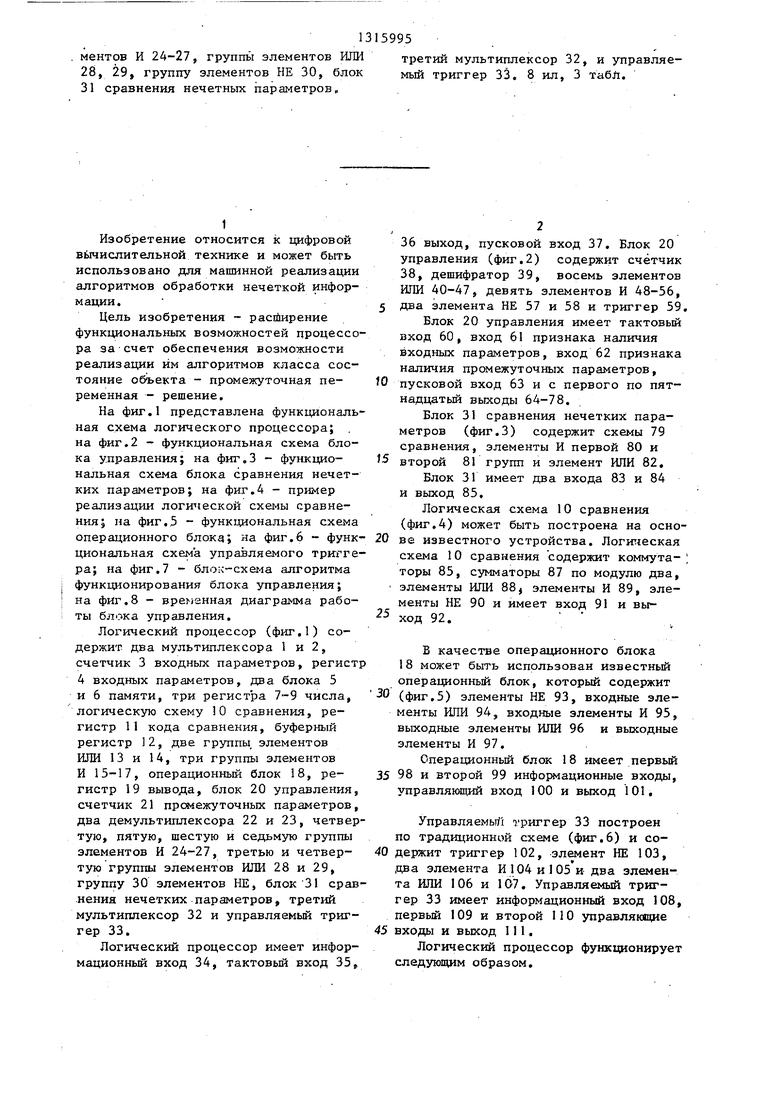

На фиг.1 представлена функциональная схема логического процессора; . на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема блока сравнения нечетких параметров; на фиг.4 - пример реализации логической схемы сравнения; на фиг.5 - функциональная схема операционного блока; на фиг.6 - функциональная схема управляемого триггера; на фиг.7 - блок-схема алгоритма функционирования блока управления; на фиг.8 - временная диаграмма работы блока управления.

Логический процессор (фиг.1) содержит два мультиплексора 1 и 2, счетчик 3 входных параметров, регистр 4 входных параметров, два блока 5 и 6 памяти, три регистра 7-9 числа, логическую схему 10 сравнения, регистр 11 кода сравнения, буферный регистр 1 2, две группы, элементов ИЛИ 13 и 14, три группы элементов И 15-17, операционный блок 18, регистр 19 вывода, блок 20 управления, счетчик 21 промежуточных параметров, два демультиплексора 22 и 23, четвертую, пятую, шестую и седьмую группы элементов И 24-27, третью и четвертую группы элементов ИЛИ 28 и 29, группу 30 элементов НЕ, блок 31 сравнения нечетких параметров, третий мультиплексор 32 и управляемый триггер 33.

Логический процессор имеет информационный вход 34, тактовый вход 35,

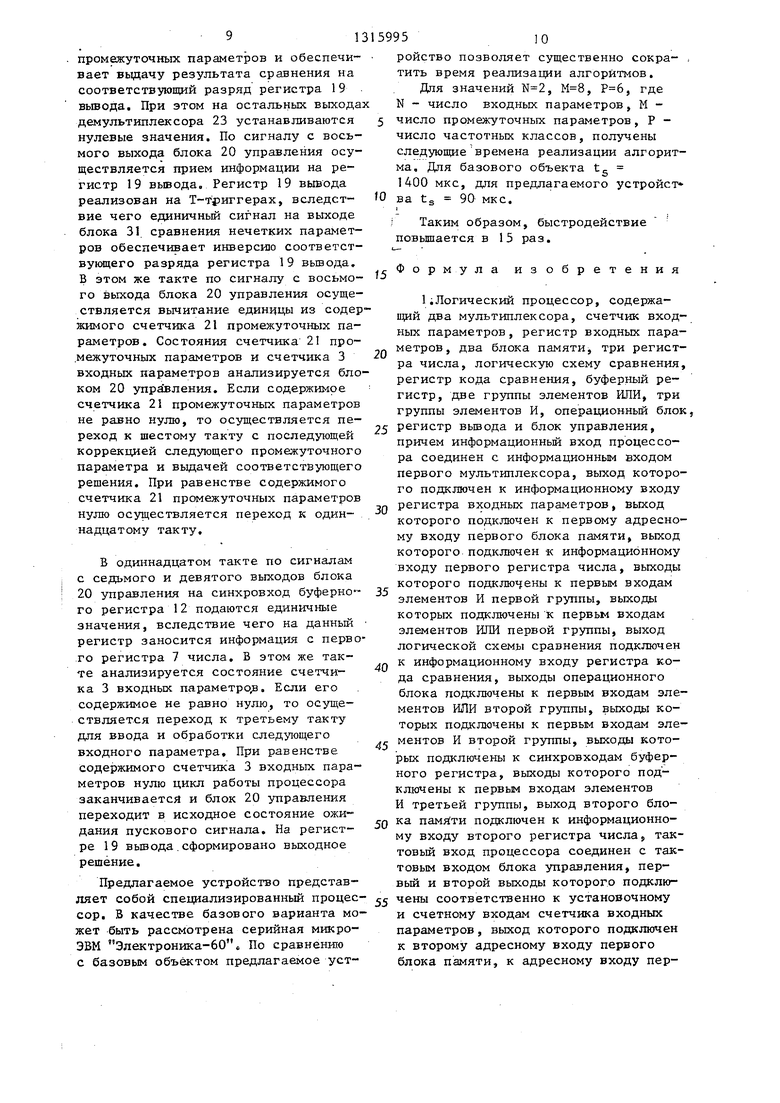

36 выход, пусковой вход 37. Блок 20 управления (фиг.2) содержит счётчик 38, дешифратор 39, восемь элементов ИЛИ 40-47, девять элементов И 48-56,

два элемента НЕ 57 и 58 и триггер 59. Блок 20 управления имеет тактовый вход 60, вход 6 признака наличия входных параметров, вход 62 признака наличия промежуточных параметров,

пусковой вход 63 и с первого по пятнадцатый выходы 64-78.

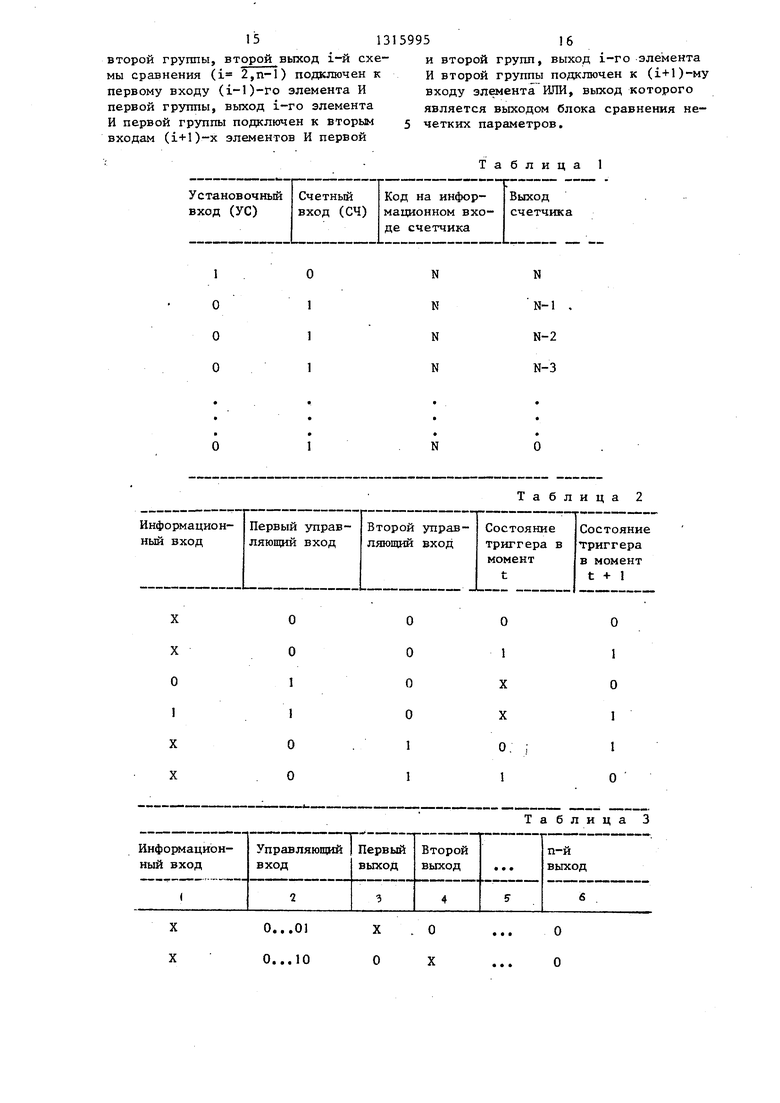

Блок 31 сравнения нечетких параметров (фиг.З) содержит схемы 79 сравнения, элементы И первой 80 и

второй 81 групп и элемент ИЛИ 82, Блок 31 имеет два входа 83 и 84 и выход 85.

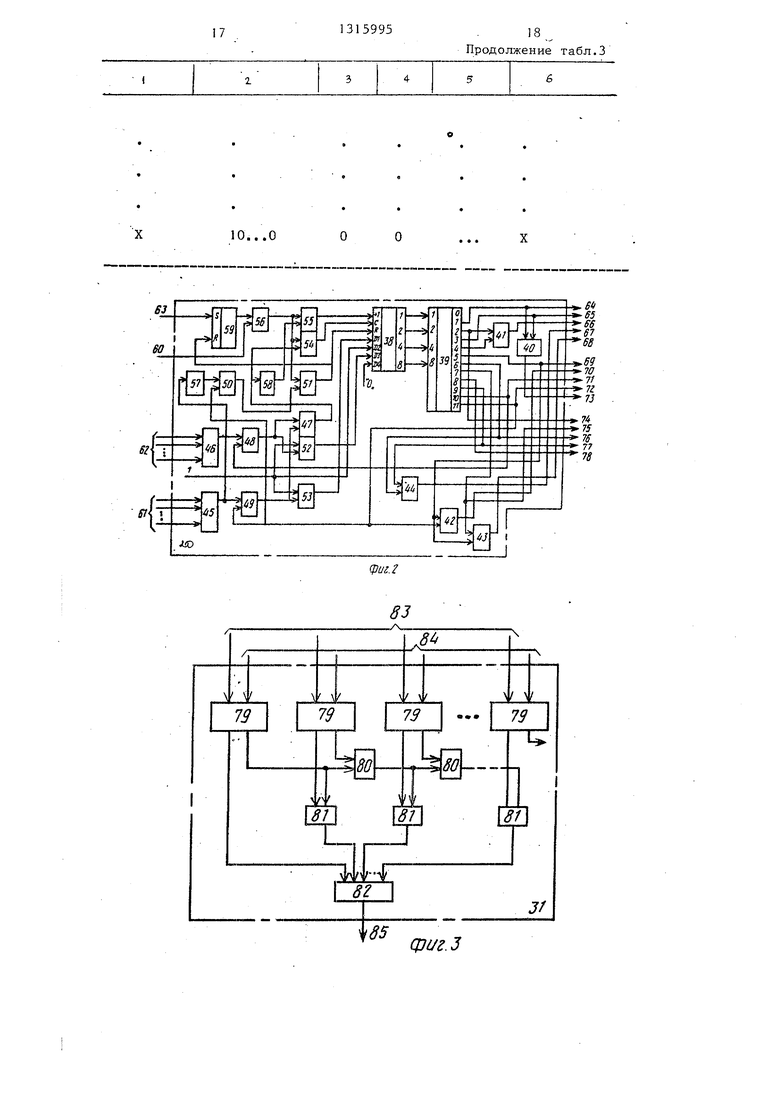

Логическая схема 10 сравнения (фиг.4) может быть построена на основе известного устройства. Логит еская схема 10 сравнения содержит коммута- ; торы 85, сумматоры 87 по модулю два, элементы ИЛИ 88j элементы И 89, элементы НЕ 90 и имеет вход 91 и выход 92.

В качестве операционного блока 18 может быть использован известный операционньй блок, который содержит

(фиг.5) элементы НЕ 93, входные элементы ИЛИ 94, входные элементы И 95, выходные элементы ИЛИ 96 и выходные элементы И 97.

Операционный блок 18 имеет первьй

98 и второй 99 информационные входы, управляющий вход 100 и выход 101,

Управляемы/ триггер 33 построен о традиционной схеме (фиг.6) и соержит триггер 102, элемент НЕ 103, цва элемента И 104 и 1 О5 и два элемена ИЛИ 106 и 107, Управляемый тригер 33 имеет информационный вход 108, ервьй 109 и второй ПО управляющие

ходы и выход 111.

Логический процессор функционирует ледующим образом.

Работа начинается по сигналу Пуск, поступающему на пусковой вход 37 процессора. При этом по тактовым сигналам, поступающим на тактовый

На выход логической схемы 10 сравнения выдается унитарный код, единица которого соответствует максимальному элементу нечеткого множества, В этом

вход 60 блока 20 управления, он начи- 5 же такте по сигналу с одиннадцатого

нает вырабатьшать последовательность управляющих сигналов. В исходном состоянии на всех выходах,блока 20 управления установлены пассивные уровни.

Первый блок 5 памяти имеет страничную организацию, причем каждая страница соответствует единому входному параметру, а каждая ячейка - конкретному значению входного парамет ра. .

В первом такте по сигналу с первого выхода блока 20 управления, поступающему на установочный вход счетВ третьем такте по сигналу с вто рого выхода блока 20 управления осу ществляется вычет единицы из содерж мого счетчика 3 входных параметров, что означает переход к следукщему параметру. При этом содержимое счет чика 3 адресует следующую страницу первого блока 5 памяти и подключает к входу регистра 4 следующий вход первого мультиплексора 1, на которы

чика 3 входных параметров, этот счет-20 подается значение соответствующего

чик устанавливается в исходное состояние, соответствукяцее первому анализируемому параметру. Работа счетчика 3 иллюстрируется табл.1 ис тиннос- ти.

На информационные входы счетчика подается постоянный код, равный числу N входных параметров. Табл.1 опи- сьшает функционирование счетчика 21 промежуточных параметров.

Информация с выхода счетчика 3 входных параметров поступает на первый адресный вход первого блока 5 памяти, выбирая страницу, а также на управляниций вход первого мультиплексора 1, разрешая прохождение на вход регистра 4 входных параметров значения соответствующего параметра. В этом же такте по сигналу с десятого выхода блока 20 управления осущест-. вляется занесение текущего значения параметра на регистр А входных параметров .

Во втором такте по сигналу с третьего выхода блока 20 управления поступающему на вход чтения первого блока 5 памяти и синхровход первого регистра 7 числа, осуществляется счи тьтание информации из первого блока 5 памяти на первый регистр 7 числа. Считанная информация представляет собой нечеткое множество - вектор степеней принадлежности входного значения к лингвистическим терм-значе- киям входной переменной. Элементы этого вектора сравниваются между собой логической схемой 10 сравнения, которая вьшвляет максимальный из них

На выход логической схемы 10 сравнения выдается унитарный код, единица которого соответствует максимальному элементу нечеткого множества, В этом

же такте по сигналу с одиннадцатого

выхода блока 20 управления код с выхода логической схемы 10 сравнения загружается на регистр 11 кода сравнения .

В третьем такте по сигналу с второго выхода блока 20 управления осуществляется вычет единицы из содержимого счетчика 3 входных параметров, что означает переход к следукщему параметру. При этом содержимое счетчика 3 адресует следующую страницу первого блока 5 памяти и подключает к входу регистра 4 следующий вход первого мультиплексора 1, на который

подается значение соответствующего

входного параметра. По сигналу на десятом выходе блока 20 управления это значение заносится на регистр 4 входных параметров.

0

е

В четвертом такте по сигналу с третьего выхода блока 20 управления осуществляется считьшание соответст- вукяцего нечеткого вектора из первого блока 5 памяти на первый регистр 7 числа.

В пятом такте блок 20 управления выдает следующие сигналы: сигнал на пятом выходе, поступающий на управляюг щий вход операционного блока 18; сигнал на шестом выходе, поступающий на вторые выходы первой 15 и второй 16 групп элементов И; сигнал на седьмом выходе, поступающий на второй вход

0 третьей группы элементов И 17, При этом информация с выхода первого регистра 7 числа через первую группу элементов И I5 и первую группу элемеи- тов ИЛИ 13 поступает на первый вход

5 операционного блока 18. На второй вход операционного блока 18 через вторую группу элементов И 16 и третью группу элементов ИЛИ 28 поступает информация с выхода буферного регистра 12. Слова в первом регистре 7 числа и буферном регистре 12 имеют одинаковый формат и разбиты на N полей, каждое из которых содержит код степени принадлежности входного значения нечеткому множеству. Операционный блок 18 реализует попарное сравнение содержимого полей, поданных на его входы, и выдает единицу на соответствующий выход в случае, когда значе513

ние на первом входе строго меньше, чем на втором, N-разрядньм код сравнения с выхода операционного блока 18 через вторую группу элементов ИЛИ 14 и третью группу элементов И 17 поступает на синхровход буферного регистра 12, При этом каждый разряд N-pasрядного синхровхода буферного регистра 12 управляет приемом информации в соответствующее поле, таким образом, поля буферного регистра 12 синхронизируются раздельно, так как информационный вход буферного регистра 12 подключен к выходу первого регистра 7 числа, то в результате на буферньш регистр 12 поступают минимальные значения содержимого соответствующих полей первого регистра 7 числа и буферного регистра 12, Приче перед запуском процессора в работу буферный-регистр 12 должен быть запонен единицами. В этом же такте по сигналу с шестого вьпсода блока 20 управления счетчик 21 промежуточных параметров устанавливается в начальное состояние.

В шестом такте по сигналу с тринадцатого выхода блока 20 управления поступающему на первый управляющий вход управляемого триггера 33, осуществляется его установка. При этом на информационный вход триггера 33 через третий мультиплексор 32 поступает содержимое разряда регистра 19 вьшода, номер которого определяется содержимым счетчика 21 промежуточных параметров. Первьй управляющий вход управляемого триггера 33 является входом занесения, поэтому триггер 33 устанавливается в соответствии со значением, поданным на его информационный вход. Функционирование управляемого триггера 33. описывается табл.2 (X - безразличное состояние).

В этом же такте по сигналу с четвертого выхода блока 20 управления, поступающему на вход чтения второго блока 6 памяти и синхровход второго регистра 8 числа, осуществляется считьщание значения промежуточного параметра из второго блока 6 памяти на второй регистр 8 числа. Это значение является в общем случае нечетким, т.е, представляет собой вектор степени принадлежности параметра к различным классам. Формат слова во втором регистре 8 числа аналогичен

5 . 6

форматам слов в первом регистре 7 числа и буферном регистре 12.

Б седьмом такте блок 20 управления формирует сигнал на пятом выхо- де, поступающий на управляюш 1й вход операционного блока 18, а также сигнал на двенадцатом выходе, поступающий на вторые входы четвертой 24 и шестой 26 групп элементов И и синхро

вход третьего регистра 9 числа. При этом процессор реализует следующие действия . Содержимое второго регистра 8 числа постзшает на первый вход седьмой группы элементов И 27, а также через шестую группу элементов И 26.и первую группу элементов ИЛИ 13 поступает на первый вход операционного блока 18. Содержимое поля буферного регистра 12, определяемое

состоянием счетчика 21 промежуточных параметров, передается через второй мультиплексор 2 на информационньй вход первого демультиплексора 22. Первый демулзьтиплексор 22 пропускает информацию с входа на один из своих выходов в соответствии с кодом на регистре 11 кода сравнения. На остальных выходах демультиплексора 22 устанавливаются нулевые значения. Функционирование первого демультиплексора 22 описьшается табл.3 истинности (X - информация на входе демультиплексора) .

Смысл преобразования, реализуемого вторым мультиплексором 2 и первым демультиплексором 22, заключается в следующем. Информация, хранящаяся на буферном регистре 12, представляет

собой вектор степени принадлежности входного параметра к различным проме- жуточньЕм параметрам. Второй мультиплексор 2, управляемьш счетчиком 21 промежуточных параметров, выделяет

элемент вектора (поле буферного регистра 12), соответствующий обрабатываемому в данном цикле промежуточному параметру. Значение промежуточного параметра является в общем случае нечетким, т.е.представляет собой нечеткое подмножество некоторого мноества классов. Класс, в котором моет получить приращение промежуточный параметр, определяется содержимым регистра 11 кода сравнения. Этот регистр управляет прохождением значе-; кия на соответствующий этому классу . выход первого демультиплексора 22, С выхода первого демультиплексора 22

71

эта информация поступает па первый вход пятой группы элементов И 25, а также через четвертую группу элементов И 24 и третьею группу элементов ИЛИ 28 на второй вход операционного блока 18. Таким образом, операционный блок 18 реализует-Е данном слу чае поэлементное сравнение полей ходов на втором регистре 8 числа и на выходе первого демультиплексора 22. Код сравнения с выхода операционного блока 18 поступает на второй вход пятой группы элементов И 25 и через группу элементов НЕ 30 на второй вхо седьмой группы элементов И 27, Пятая 25 и седьмая 27 группы элементов И разбиты на подгруппы (фиг.10), каждая из которых соответствует одному полю информационного слова. При этом вторые входы элементов И одной подгруппы объединены между собой и подключены к соответствующему разряду второго входа группы элементов И, так как на выходе первого демулъти- плексора 22 ненулевая информация присутствует только в единственном поле, то все подгруппы пятой группы элементов И 25, соответствующие другим полям, блокируются нулевыми сигналами с выхода демультиплексора 22. По условию функционирования операционного блока 18 на всех его выходах, соответствующих этим полям, устанавливаются нулевые сигналы (вход 1 & вход 2). Эти сигналы чер.ез группу элементов НЕ 30 единичным значениям подаются на вторые входы соответствующих подгрупп седьмой группы элементов И 27. Таким образом, на входы этих полей третьего регистра 9 числа через седьмую группу элементов И 27 и четвертую группу элементов ИЛИ 29 поступает информация из соответствующих полей второго регистра 8 числа. Для поля, выделенного содержимьм регистра 11 кода сравнения, на выходе первого демультиплексора 22 осуществляется сравнение его coдepжи югo с содержимым соответствующего поля второго регист

.ра 8 числа. На соответствующем выходе операционного блока 18 в зависимости от результата сравнения устанавливается значение, пропускающее на вход заданного поля третьего регистра 9 числа информацию либо с выхода первого демультиплексора 22 через пятую группу элементов И 25 к

958

четвертую группу элементов Ш1И 29, либо с второго регистра 8 числа через седьмую группу элементов И 27 к четвертую группу элементов ИЛИ 29. Это значение является большим из сравниваемых. По сигналу с двенадцатого выхода блока 20 управления осуществляется занесение информации на третий регистр 9 числа.

Таким образом, в третьем регистре 9 числа формируется нечеткое значение промежуточного параметра, скорректированное с учетом вновь поступающего значения входного параметра.

В восьмом такте по сигналу с пятнадцатого выхода блока 20 управления сформированное на третьем регистре 9 числа значение записьшается во вто рой блок 6 памяти.

В девятом такте по сигналу с четырнадцатого выхода блока 20 управления, поступающему на второй управляющий вход триггера 33, осуществляется инверсия его состояния (табл.2

инстинноети триггера 33). В этом же такте по сигналу с четвертого выхода блока 20 управления осуществляется считьшание нечеткого значения промежуточного параметра из второго

блока 6 памяти на второй регистр 8

числа.

I .

В десятом в блоке 31 сравнения нечетких параметров происходит

сравнение нечетких значений параметров , записанных на втором 8 -и третьем 9 регистрах числа. Сравнение нечетких значений может быть реализовано следующим образом. Считается,

что классы, составляющие базовое множество нечеткого параметра, упорядочены. Сравниваются степени принадлежности параметра высшим классам, В слуггае неравенства результат их сравнения считается результатом сравнения нечетких значений. Если степени при-м надлежности сравниваемых нечетких множеств равны, то сравн 1ваются принадлежности к следующему по порядку

классу и т,д. На выходе блока 31 сравнения нечетких параметров устанавливается единичное значение, если значение нечеткого параметра на втором входе больше, чем на первом, Результат сравнения с выхода блока 31 сравнения нечетких параметров через второй демультиплексор 23 поступает на регистр 19 вывода, Демульт1С1лексор 23 управляется кодом на счетчике 21

91

промежуточных параметров и обеспечивает вьщачу результата сравнения на соответствующий разряд регистра 19 вьгоода. При этом на остальных выхода демультиплексора 23 устанавливаются нулевые значения. По сигналу с восьмого выхода блока 20 управления осуществляется прием информации на регистр 19 вьюода. Регистр 19 вьюода реализован на Т-триггерах, вследствие чего единичньй сигнал на выходе блока 31 сравнения нечетких параметров обеспечивает инверсию соответст- вунлцего разряда регистра 19 вьшода. В этом же такте по сигналу с восьмого выхода блока 20 управления осуществляется вычитание единицы из содер жимого счетчика 21 промежуточных параметров. Состояния счетчика 21 про- .межуточных параметров и счетчика 3 входных параметров анализируется блоком 20 управления. Если содержимое счетчика 21 промежуточных параметров не равно нулю, то осуществляется переход к шестому такту с последующей коррекцией следующего промежуточного параметра и вьщачей соответствующего решения. При равенстве содержимого счетчика 21 промежуточных параметров нулю осуществляется переход к одиннадцатому такту.

В одиннадцатом такте по сигналам с седьмого и девятого выходов блока 20 управления на синхровход буферного регистра 12 подаются единичные значения, вследствие чего на данный регистр заносится информация с первого регистра 7 числа. В этом же такте анализируется состояние счетчика 3 вкодньк параметро;в. Если его содержимое не равно нулю, то осуществляется переход к третьему такту для ввода и обработки следующего входного параметра. При равенстве содержимого счетчика 3 входных параметров нулю цикл работы процессора заканчивается и блок 20 управления переходит в исходное состояние ожидания пускового сигнала. На регистре 19 вьшода.сформировано выходное решение.

Предлагаемое устройство представляет собой специализированный процес- чены соответственно к установочному сор. В качестве базового варианта мо- и счетному входам счетчика входных жет быть рассмотрена серийная микро- параметров, выход которого подключен ЭВМ Электроника-60. По сравнению к второму адресному входу первого с базовым объектом предлагаемое уст- блока памяти, к адресному входу пер5995

10

ройство позволяет существенно сокра- тить время реализации алгоритмов.

Для значений , , , где N - число входных параметров, М 5 число промежуточньгк параметров , Р - число частотных классов, получены следующие времена реализации алгоритма. Для базового объекта t 1400 МКС, для предлагаемого устройст

О ва ts 90 МКС.

15

Таким образом, быстродействие повьппается в 15 раз.

Формула изобретения

0

0

0

1;Логический процессор, содержащий два мультиплексора, счетчик входных параметров, регистр входных параметров, два блока памяти, три регистра числа, логическую схему сравнения, регистр кода сравнения, буферный регистр, две группы элементов ИЛИ, три группы элементов И, операционный блок,

5 регистр вьшода и блок управления, причем информационньй вход процессора соединен с информационным входом первого мультиплексора, выход которого подключен к информационному входу регистра входных параметров, выход которого подключен к первому адресному входу первого блока памяти, выход которого подключен к информационному входу первого регистра числа, выходы которого подключены к первым входам элементов И первой группы, выходы которых подключены к первьм входам элементов РШИ первой группы, выход логической схемы сравнения подключен к информационному входу регистра кода сравнения, выходы операционного блока подключены к первым входам элементов ИЛИ второй группы, выходы которых подключены к первым входам элег ментов И второй группы, выходы которых подключены к синхровходам буферного регистра, выходы которого подключены к первым входам элементов И третьей группы, выход второго бло0 ка памя ти подключен к информационному входу второго регистра числа, тактовый вход процессора соединен с тактовым входом блока управления, первый и второй выходы которого подклю5

вого мультиплексора и входу признака наличия входных параметров блока управления, третий выход которого подключен к входу чтения первого блока памяти и синхровходу первого регистра числа, четвертый выход блока управления подключен к входу чтения второго блока памяти и синхровходу второго регистра числа, пятый, шестой, седьмой, восьмой и девятый выходы блока управления подключены соответственно к управляющему входу операционного блока, вторым входам элементов И, второй группы элементов И, вторым входам третьей группы, синхровходу регистра вьшода и вторым входам элементов ИЛИ второй группы, выход регистра вьшода подключен к выходу процессора,отличающий с я тем, что, с целью расширения функциональных возможностей процессора за счет обеспечения возможности реализации им алгоритмов класса состояние объекта - промежуточная

переменная - решение, в него введе-

t

ны счетчик промежуточных параметров,

два демультиплексора, с четвертой по седьмую группы элементов И, третья и четвертая группы элемент ов ИЛИ, элементов НЕ, блок сравнения нечетких параметров, третий мультиплексор и триггер, причем выход первого регистра числа подключен к входу логической схемы сравнения и информационному входу буферного регистра, выход которого подключен к информационному входу второго мультиплексора, выход которого подключен к информационному входу первого демультиплексора, адресньй вход которого подключен к выходу регистра кода сравнения, выход первого демультит плексора подключен к первьм входам элементов И четвертой и пятой групп, выходы элементов И четвертой группы подключены к вторым входам элементов ИЛИ третьей группы, первые входы и выходы которых подключены соответственно к выходам элементов И второй группы и вторым информационным входам операционного блока, выход счетчика промежуточных параметров подключен к адресному входу второго мультиплексора и первому адресному входу второго блока памяти, выход которого подключен к информ.ационному входу второго регистра числа, выходы которого подключены к первым входам блока сравнения нечетких параметров и элементов И шестой и седьмой групп, и выходы элементов И шестой группы подключены к вторым входам элементов

ИЛИ первой группы, выходы которых подключены к первым информационным входам операционного блока, выходы которого подключены к вторым входам элементов И пятой группы и через

группу элементов НЕ - к вторым входам элементов И седьмой группы, выг ходы элементов И пятой и седьмой групп подключены соответственно к первым и вторьм входам элементов ИЛИ

четвертой группы, выходы которой подключены к информационным входам третьего регистра числа, выход которого подключен к информационному входу второго блока памяти и второму входу.

блока сравнения нечетких параметров, выход которого подключен к информационному входу третьего мультиплексора; выход которого подключен к информационному входу триггера, выход которого подключен к второму адресному входу второго блока памяти, адресные входы второго демультиплексора и третьего мультиплексора подключены

к выходу счетчика промежуточных пара

метров, установочный вход которого

подключен к вторьм входам элементов И первой группы и шестому выходу блока управления, восьмой выход которого подключен к счетному входу счетчика промежуточных параметров,, выход которого подключен к входу признака наличия промежуточных параметров блока управления, десятый и одиннадцатый выходы которого подключены к

синхровходам соответственно регистра входных параметров и регистра кода сравнения, двенадцатый выход блока управления подключен к вторым входам элементов И четвертой и шестой групп

и синхровходу третьего регистра числа, тринадцатью, четырнадцатый и пятнадцатый выходы блока управления подключены соответственно к первому и второму управляюцим входам тригге- ра и входу записи второго блока памяти, вход пуска блока управления является одноименным входом процессора.

2.Процессор по п,1, о т л и - чающийся тем, что блок управления содержит счетчик, дешифратор, восемь элементов ИЛИ, девять элементов И, два элемента НЕ и триггер, причем первый, второй, третий и чет131

зертьш разряды информационного выхода счетчика подключены к соответствующим разрядам входа дешифратораJ первый выход которого подключен к первому выходу блока управления первому входу первого элемента ИЛИ, выход которого подключен к десятому выходу блока управления,-второй выход дешифратора подключен к первому входу второго элемента ИЛИ и одиннадцатому выходу блока управления, третий выход дешифратора подключен к второму входу первого элемента ИЛИ и второму выходу блока управления, четвертый выход дешифратора подключен второму входу второго элемента ИЛИ, выход которого подключен к третьему выходу блока управления, пятьм выход дешифратора подкп очен к шестому выходу блока управления, первому входу третьего элемента ИЛИ и второму входу четвертого элемента ИЛИ, выход которого подключен к пятому выходу блока управления, шестой выход дешифратора подключен к трин ад цатому выходу блока управления, второму входу пятого элемента ИЛИ, выход которого подключен к четвертому выходу блока управления, седьмой выход дешифратора, подключен к первому входу четвертого элемента ИЛИ и две- наддатому выходу блока упргшления, восьмой выход дешифратора подключен к пятнаддатому выходу блока управления, девятый выход дешифратора подключен к четырнадцатому выходу блока управления и первому входу пятого элемента ИЛИ, десятый выход дешифратора подключен к восьмому блока управления и второму входу первого элемента И, одиннадцатый вы ход дешифратора подключен к девятому выходу блока управления, второму входу второго элемента И, второму входу третьего элемента И, второму входу третьего элемента ИЛИ, выход которого подключен к седьмому вьгкоду блока управления, разряды входа признака наличия входных параметров блока управления подключены к соответ.ствующим входам шестого элемента ИЛИ, а разряды входа признака чин промежуточных параметров, блока

. управления - к соответствующим вхо дам седьмого элемента ИЛИ,, выход которого подключен к первому входу первого элемента И, выход шестого элемента ИЛИ подключен к первому

5995

14

входу третьего элемента И, выход которого подключен к второму входу четвертого элемента И, выход первого элемента И подключен к первому

входу восьмого элемента ИЛИ и второ- му входу, пятого элемента И, выход которого подключен к третьему разряду информационного входа счетчика, выход второго элемента И подключен

к второму входу шестого элемента И, второму входу восьмого элемента ИЛИ, выход которого подключен к второму вх оду седьмого элемента И и через элемент НЕ - к второму входу восьмого элемента И, выход которого подключен к счетному входу счетчика, второй разряд информационного входа счетчика подк.пючен к шине единичного потенциала блока, первому входу пятого элемента И и первому входу шестого элемента И, выход которого подключен к первому разряду информационного входа счетчика, четвертый разряд информационного входа счетчика подключен к шине нулевого потенциала блока, выход четвертого элемента И подклю чен к входам установки в О счетчика и триггера, прямой вход которого подключен к первому входу девятого

элемента И, тактовый вход блока управления подключен к второму входу девя того элемента И, выход которого подключен к первому входу четвертого элемента И, первому входу восьмого

элемента И и первому входу седьмого элемента И, выход которого подключен к синхровходу счетчика, вход пуска блока управления подключен к установочному входу триггера.

3.Процессор по п.1, о т л и ч а ю- щ и и с я тем, что блок сравнения нечетких параметров содержит п схем сравнения (где п - разрядность нечеткого вектора), i - 2 элементов И пер-, вой группы (, п), i-1 элемен- тов И второй группы, элемент ИЛИ, причем разряды первого и второго блоков сравнения нечетких параметров

подключены соответственно к первым и вторьм входам соответствуюш 1х схем сравнения, первый выход первой схемы сравнения подключен к первому входу элемента ИЛИ, второй выход первой схемы сравнения подключен к вто- входам первых элементов И первой и второй групп, первый выход i-й схемы сравнения (i 2,п) подключен к первому входу (i-1)-го элемента И

151315995 6

второй группы, второй выход i-й схе- и второй групп, выход i-rо элемента мы сравнения (i 2,п-1) подключен к и второй группы подключен к (1+1)-му

входу элемента ИЛИ, выход которого является выходом блока сравнения непервому входу (i-l)-ro элемента И

первой группы, выход i-ro элемента

И первой группы подключен к вторым 5 четких параметров.

входам (1+1)-х элементов И первой

о о 1 1

о о

X X

0...01 0...10

Таблица 1

Таблица 2

о

1

X X о, ;

о 1

о 1 1 о

Таблица 3

. о

X

о о

X

10...О

Продолжение табл.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический процессор | 1985 |

|

SU1305704A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Управляющий процессор | 1984 |

|

SU1290341A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано для машинной реализации алгоритмов обработки нечетной информации. Целью изобретения является расширение функциональных возможностей процессора за счет обеспечения возможности реализации им алгоритмов класса состояние объекта - промежуточная переменная - решение. С этой целью процессор содержит счетчик 2 промежуточных параметров два демультиплексора 22,.23, группы эле- (Л со СП СО со СП

85

сриг.З

9г

Фиг.7

. ,

п п пппп finnnnn п п

j-n п

m гп

JTL

Фиг.д

JTL

Редактор О.Бугир

Составитель Н.Захаревич

Техред и.Глущенко Корректор Т.Колб

Заказ.2365/52 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужг ород, ул. Проектная, 4

| Авторское свидетельство СССР № 843592, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Балашов Е.П | |||

| и др | |||

| Многофункциональные вычислительные структуры | |||

| - М.: Советское радио, 1978, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Устройство приоритета | 1982 |

|

SU1108450A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1986-02-05—Подача