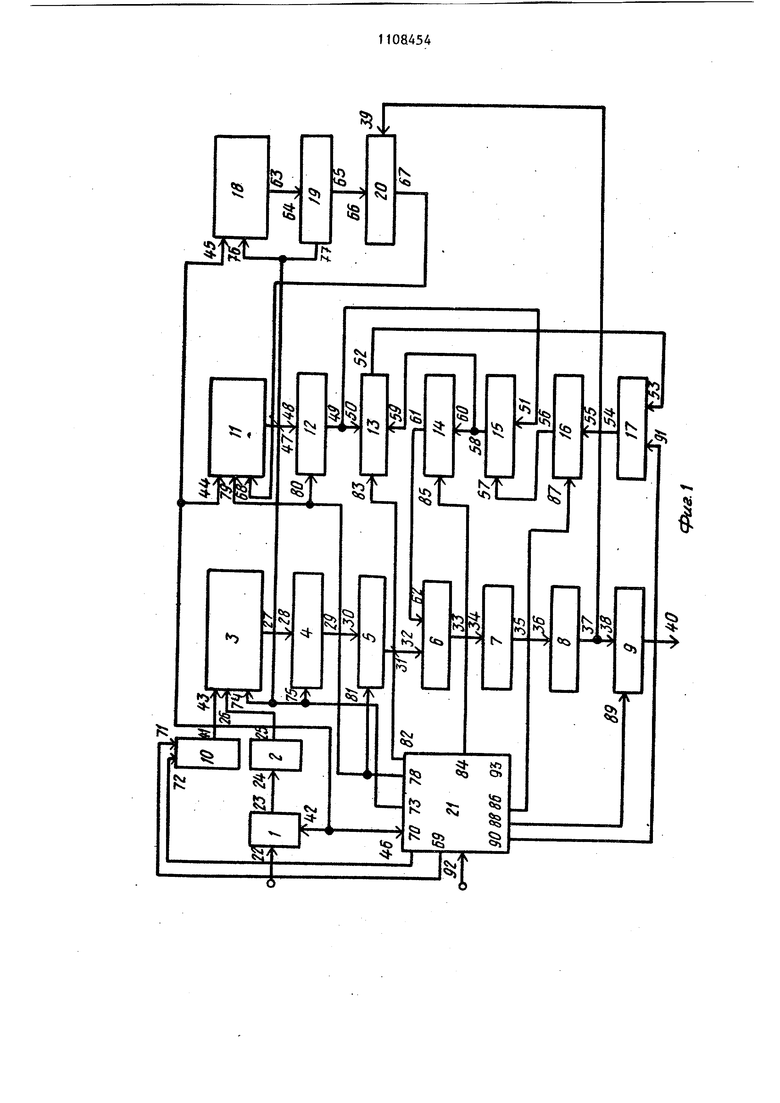

буферного регистра соединены соответ ственно с выходом третьего регистра числа и выходами элементов И третьей группы, первые и вторые входы которых подключены соответственно к выхо дам элементов ИЛИ второй группы и седьмому выходу блока синхронизации, восьмой и девятый выходы которого соединены соответственно с управляющим входом регистра вывода и вторыми входами элементов ИЛИ второй группы, информационный и управляющий вхрды второго мультиплекстора подклю чены соответственно к выходу второго регистра числа и выходу регистра кода сравнения, вход которого соединен с выходом схемы сравнения, а информа ционный вход и выход регистра вьгоода подключены соответственно к выходу регистра кода сравнения и вуходу процессора. 2. Процессор по п. 1, отличающийся тем, что блок синхронизации содержит счетчик, семь элементов НЕ, двадцать один элемент и пять элементов ИЛИ, при этом первый, второй и четвертый информационные входы счетчика соединены с шиной нулевого потенциала, а третий информационный вход счетчика - с шиной единичного потенциала, первый, второй, третий и четвертый выходы счетчика подключены ко входам соответственно первого, второго, третьего и четвертого элементов НЕ, первый, вто рой, третий и четвертый входы и выхо первого элемента И соединены соответ ственно с выходами первого, второго и третьего элементов НЕ, четвертым выходом счетчика и входом пятого эле мента НЕ, первый, второй, третий и четвертый входы и выход второго элемента И подключены соответственно к вькоду первого элемента НЕ, второму выходу счетчика, третьему выходу счетчика, выходу четвертого элемента НЕ и входу шестого элемента НЕ, входы и выход первого элемента ИЛИ соединены соответственно с управляющим входом блока и входом седьмого элемента НЕ, первый и второй входы и вьпсод третьего элемента И подключены соответственно к выходам второго элемента И, седьмого элемента НЕ и первому входу второго элемента ИЛИ второй вход которого соединен с выхо дом шестого элемента НЕ, первый, второй и третий входы и выход четвер того элемента И подключены соответ54ственно к выходу второго элемента И, тактовому входу блока, выходу первого элемента ИЛИ и синхровходу счетчика, первый и второй входы и выход пятого элемента И соединены соответственно с тактовым входом блока, выходом первого элемента И и входом сброса счетчика, первый, второй и третий входы и выход шестого элемента И подключены соответственно к тактовому входу блока, выходу пятого элемента НЕ, выходу второго элемента ИЛИ и счетному входу счетчика, первый и второй входы седьмого элемента И соединены с выходами третьего и четвертого элементов НЕ, первый и второй входы восьмого элемента И подключены к выходу четвертого элемента НЕ и третьему выходу счетчика, первый и второй входы девятого элемента И соединены с четвертым выходом счетчика и выходом третьего элемента НЕ, первый и второй входы десятого элемента И подключены к первому и второму выходам счетчика, первый и второй входы одиннадцатого элемента И соединены с выходом второго элемента НЕ и первым выходом счетчика, первый и второй входы двенадцатого элемента И подключены к выходам первого и второго элементов НЕ, первый и второй входы тринадцатого элемента И соединены с выходом первого элемента НЕ и вторым выходом счетчика, первый и второй входы четырнадцатого элемента И подключены к выходам седьмого и тринадцатого элементов И, первый и второй входы пятнадцатого элемента И соединены с выходами седьмого и одиннадцатого элементов И, первьй и второй входы шестнадцатого элемента И подключены к выходам восьмого и двенадцатого элементов И, первый и второй входы семнадцатого элемента И соединены с выходами восьмого и одиннадцатого элементов И, первый и второй входы восемнадцатого элемента И подключены к выходам седьмого и десятого элементов И, первый и второй входы девятнадцатого элемента И соединены с выходами седьмого и восьмого элементов И, первый и второй входы двадцатого элемента И подключены к выходам девятого и двенадцатого элементов И, первый и второй входы двадцать первого элемента И соединены с выходами восьмого и тринадцатого элементов И, выход шестнадцатого элемента И подключен к первому выходу блока и первому входу третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом пятнадцатого элемента И и третьим выходом блока, выход пятнадцатого элемента И подключен ко второму выходу блока, первый и второй входы и выход четвертого элемента ИЛИ соединены соответственно с выходами четырнадцатого и семнадцатого элементов И и четвертым выходом блока, выходы двадцать первого элемента И, девятнадцатого элемента И, пятого элемента ИЛИ, двадцатог элемента И и восемнадцатого элемента И подключены соответственно к пятому, шестому, седьмому, восьмому и девятому выходам блока, а первый и второй входы пятого элемента ИЛИ соединены с выходами восемнадцатого и двадцать первого элементов И.

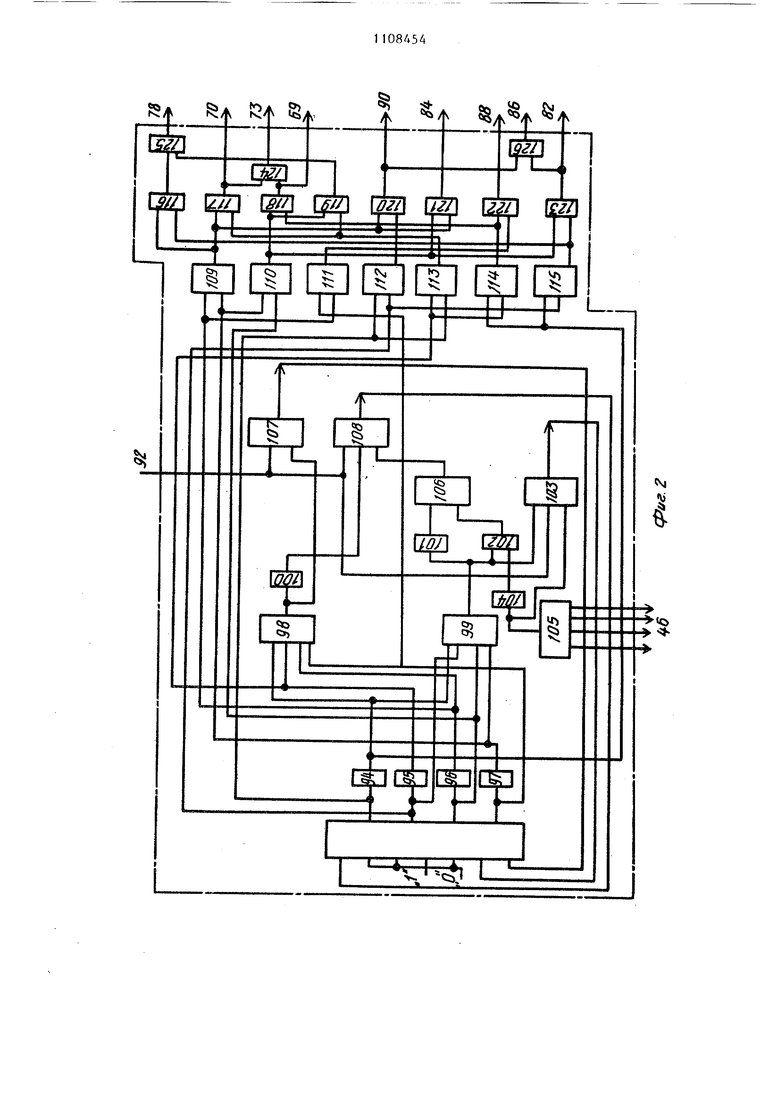

3. Процессор по п. 1, отличающийся Tei, что операционный блок содержит четыре операционные группы элементов И, ИЛИ и НЕ,

каждая из которых включает один элемент НЕ, два элемента И и два элемента ИЛИ, при этом входы элементов НЕ каждой группы соединены со вторым информационным входом блока, первые и вторые входы первого элемента И и первого элемента ИЛИ каждой группы подключены соответственно к первому информационному входу блока и вьгходу элемента НЕ той же группы, выходы первого элемента ИЛИ и первого элемента И каж,цой группы соединены с первыми входами соответственно второго элемента И и второго элемента ИЛИ той же группы, выход второго элемента И каждой группы подключен ко второму входу второго элемента ИЛИ той же группы, вторые входы элементов И первой группы соединены с управляющим входом блока, вторые входы вторых элементов И второй и четвертой групп подключены к выходам вторых элементов ИЛИ соответственно первой и третьей групп, а выходы вторых элементов ИЛИ второй и четвертой групп соединены с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический процессор | 1985 |

|

SU1305704A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для обработки данных | 1987 |

|

SU1536396A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1988 |

|

SU1509985A1 |

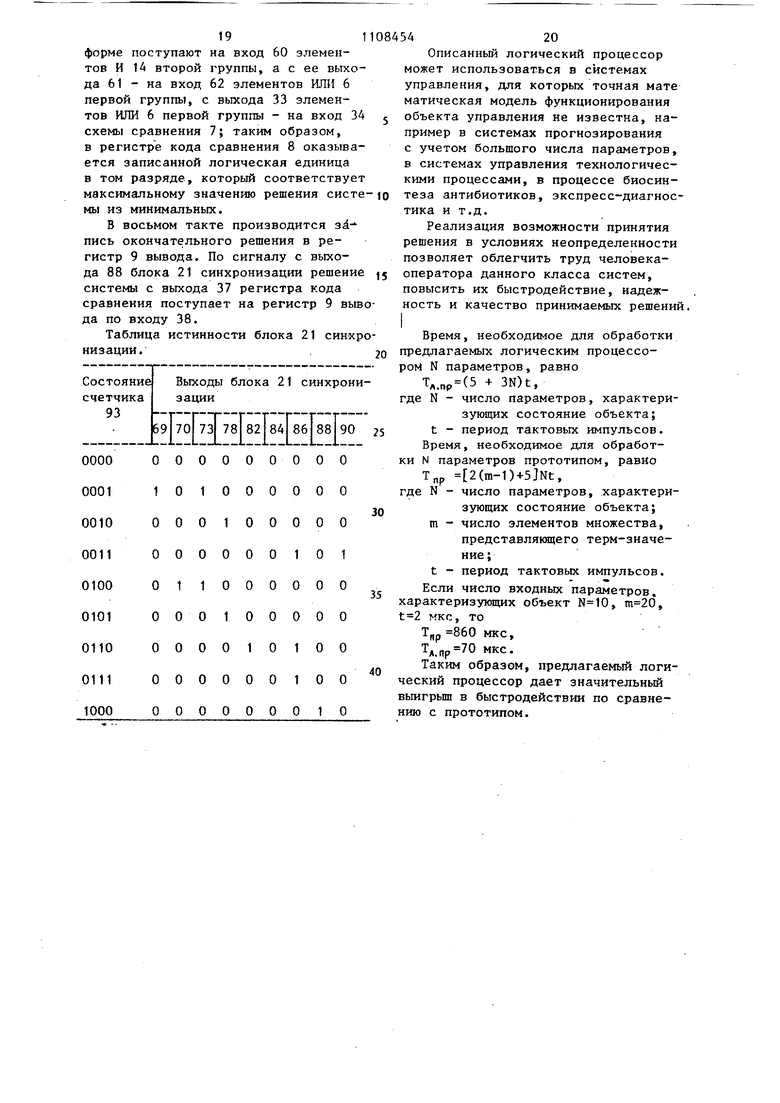

1. ЛОГИЧЕСКИЙ ПРОЦЕССОР, содержащий первьй мультиплексор, регистра адреса, счетчик адреса, два блока памяти, два регистра числа, схему сравнения, операционный блок и блок синхронизации, управляющий вход, тактовый вход, первый и второй выходы которого соединены соответственно с выходом счетчика адреса, тактовым входом процессора, установочным входом и счетным входом счетчика адреса, третий выход блока синхронизации подключен к управляющим входам первого и второго блоков памяти и первого и второго регистров числа, выход счетчика адреса соединен с управляющим входом первого мультиплексора и первыми адресными входами первого и второго блоков памяти, вы- ходы которых подключены к информационным .входам соответственно первого и второго регистров числа, информационный вход и выход первого мультиплексора соединены соответственно с информационным входом процессора и входом регистра адреса, выход которого подключен ко второму адресному входу первого блока памяти, о т личающийся тем, что, с целью повышения быстродействия, он содержит второй мультиплексор, третий блок памяти, третий регистр числа, буферный регистр, регистр кода сравнения, регистр вывода, три группы элементов И и две группы элементов ИЛИ, причем первые и вторые входы и выходы элементов И первой группы соединены соответственно с выходом первого регистра числа, четвертым выходом блока синхронизации и первыми входами элементов ИЛИ первой группы, вторые входы и выходы котоS (Л рых подключены соответственно к выходам элементов И второй группы и входу схемы сравнения, первый и второй адресные входы, управляющий вход и выход третьего блока памяти соединены соответственно с выходом счетчика адреса, выходом второго мультиплексора, четвертым выходом блока синхронизации и информационным входом третьего регистра числа, управляющий оо вход и выход которого подключены 4 СД 4ib соответственно к четвертому выходу блока синхронизации и первому информационному входу операционного блока, второй информационный вход, управляющий вход и выход операционного блока соединены соответственно с выходом буферного регистра, пятым выходом блока синхронизации и первыми входами элементов ИЛИ второй группы, первые и вторые входы элементов И второй группы подключены соответственно к выходу буферного регистра и шестому выходу блока синхронизации, информационный и управляющий входы

1

Изобретение относится к вычислительной технике и может быть использовано для классификации ситуации в многопараметрических системах, например для функциональной диагностик в автоматических системах многопрофильной оценки здоровья, в системах управления уличным движением, в системах управления теплицами.

Известно устройство, содержащее блок памяти, регистр сдвига, регистр адреса, регистр числа, два триггера режима, счетчик, устройство управления, входные шины аргумента и выходные шины результата, причем выход регистра адреса соединен с первым входом блока памяти, первый, второй и третий выходы которого соответственно подключены к информационному входу регистра числа, к первому входу первого триггера режима и к первому входу второго регистра режима, первый разрядный выход регистра числа является выходом результата, а второй, третий разрядные.выходы

регистра числа подключены соответственно к информационному входу регистра адреса и к первому входу счетчика, входом управляющего процессора является вход регистра сдвига, выход которого подключен ко второму входу блока памяти lJ.

Данное устройство предназначено для преобразования множества параметров, характеризующих состояние объекта, в двоичный код.

Недостатком данного устройства является низкое быстродействие, обусловленное тем, что выбор решения производится путем последовательного сравнения текущего значения параметра с эталонными значениями.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство для реализации разветвленных алгоритмов.

Логический процессор содержит первый мультиплексор, регистр адреса, счетчик адреса, два блока памяти. два регистра числа, схему сравнения, операционный блок и блок синхронизации , управляющий вход, тактовый вход первый и второй выходы которого соединены соответственно с выходом счетчика адреса, тактовым входом процессора, установочным входом и счетным входом счетчика адреса, третий выход блока синхронизации подключен к управляющим входам первого и второго блоков памяти и первого и второго регистров числа, выход счетчика адреса соединен с управляющим входом первого мультиплексора и первыми адресными входами первого и второго блоков памяти, выходы кото рых подключены к информационным входам соответственно первого и второго регистров числа, информационный вход и выход первого мультиплексора соеди нены соответственно с информационным входом процессора и входом регистра аДреса, выход которого подключен ко второму адресному входу первого блока памяти L 2 . Недостатком данного устройства является низкое быстродействие, так как производится последовательное сравнение текущего значения параметра с хранимыми в блоке памяти эталон ными значениями. Целью изобретения является повыше ние быстродействия за счет параллель ного сравнения текущего значения параметра с эталонными. Указанная цель достигается тем, что в логический процессор,содержащий первый мультиплексор, регистр адреса, счетчик адреса, два блока памяти, два регистра числа., схему сравнения, операционный блок и блок синхронизации, управляющий вход, тактовый вход, первый и второй выходы которого соединены соответственно с выходом счетчика адреса, тактовым входом процессора, установочным входом и счетным входом счетчика адреса третий выход блока синхронизации под ключен к управляющим входам первого и второго блоков памяти и первого и второго регистров числа, выход счетчика адреса соединен с управляющим входом первого мультиплексора и первыми адресными входами первого и второго блоков памяти, выходы кото рых подключены к информационным входам соответственно первого и второго регистров числа, информационный вход и выход первого мультиплексора соединены соответственно с -информационным входом процессора и входом регистра адреса, выход которого подключен ко второму адресному входу первого блока памяти, введены второй мультиплексор, третий блок памяти, третий регистр числа, буферный регистр, регистр кода сравнения, регистр вывода, три группы элементов И и две группы элементов ИЛИ, причем первые и вторые входы и выходы элементов И первой группы соединены соответственно с выходом первого регистра числа, четвертым выходом блока синхронизации и первыми входами элементов ИЛИ первой группы, вторые входы и выходы которых подключены соответственно к выходам элементов И второй группы и входу схемы сравнения, первый и второй адресные входы, управляющий вход и выход третьего блока памяти соединены соответственно с вьЬсодом счетчика адреса, выходом второго мультиплекстора, четвертым выходом блока синхронизации и информационным входом третьего регистра числа, управляющий вход и выход которого подключены соответственно к четвертому выходу блока синхронизации и первому информационному входу операционного блока, второй информационный вход, управляющий вход и выход операционного блока соединены соответственно с выходом буферного регистра, пятым выходом блока синхронизации и первыми входами элементов ИЛИ второй группы, первые и вторые входы элементов И второй группы подключены соответственно к выходу буферного регистра и шестому выходу блока синхронизацииj информационный и управляющий входы буферного регистра соединены соответственно с выходом третьего регистра числа и выходами элементов И третьей группы, первые и вторые входы которых подключены соответственно к выходам элементов ИЛИ второй группы и седьмому выходу блока синхронизации, восьмой и девятый вькоды которого соединены соответственно с управляющим входом регистра вывода и вторыми входами элементов ИЛИ второй группы, информационный и управляющий входы второго мультиплексора подключены соответственно к выходу второго регистра числа и выходу регистра кода сравнения, вход которого соединен с выходом схемы сравнения, а информационный вход и выход регистра вывода подключены соответственно к выходу регистра кода сравнения и выходу процессора. Блок синхронизации содержит счетчик, семь элементов НЕ, двадцать один элемент И и пять элементов ИЛИ при этом пррвый, второй и четвертый информационйые входы счетчика соедине с шиной нулевого потенциала,а третий информационный вход счетчика - с шиной единичного потенциала, первый, второй, третий и четвертый выходы счетчика подключены ко входам соответственно первого, второго, третьего и четвертого элементов НЕ, первый второй, третий и четвертый входы и выход первого элемента И соединены соответственно с выходами первого, второго и третьего элементов НЕ, чет вертым выходом счетчика и входом пятого элемента НЕ, первый, второй, третий и четвертый входы и выход вто рого элемента И подключены соответст венно к выходу первого элемента НЕ, второму выходу счетчика, третьему вы ходу счетчика, выходу четвертого элемента НЕ и входу шестого элемента НЕ, входы и выход первого элемента ИЛИ соединены соответственно с управляющим входом блока и входом седьмого элемента НЕ, первый и второй входы и выход третьего элемента И подключены соответственно к выходам второго элемента И, седьмого элемента НЕ и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента НЕ, первый, второй и третий входы и выход четвертого элемента И подклю чены соответственно к выходу второго элемента И, тактовому входу блока, выходу первого элемента ИЛИ и синхровходу счетчика, первый и второй входы и выход пятого элемента И соединены соответственно с тактовым вхо дом блока, выходом первого элемента И и входом сброса счетчика, первый, второй и третий входы и выход .шестого элемента И подключены соответственно к тактовому входу блока, выходу пятого элемента НЕ, выходу второго элемента ИЛИ и счетному входу счетчика, первый и второй входы седьмого элемента И соединены с выхо дами третьего и четвертого элементов НЕ, первый и второй входы восьмо го элемента И подключены к выходу четвертого элемента НЕ и третьему вы ходу счетчика, первый и второй входы девятого элемента И соединены с четвертым выходом счетчика и ЕЫХОДОМ третьего элемента НЕ, первый и второй входы десятого элемента И подключены к первому и второму выходам счетчика, первый и второй входы одиннадцатого элемента И соединены с выходом второго элемента НЕ и первым выходом счетчика, первый и второй входы двенадцатого элемента И подключены к выходам первого и бторого элементов НЕ, первый и второй входы тринадцатого элемента И соединены с выходом первого элемента НЕ и вторым выходом счетчика, первый и второй входы четырнадцатого элемента И подключены к выходам седьмого и тринадцатого элементов И, первый и второй входы пятнадцатого элемента И соединены с выходами седьмого и одиннадцатого элементов И, первый и второй входы шестнадцатого элемента И подключены к выходам восьмого и двенадцатого элемента И, первый и второй входы семнадцатого элемента И соединены с выходами восьмого и одиннадцатого элементов И, первый и второй входы восемнадцатого элемента И подключены к выходам седьмого и десятого элементов И, первый и второй входы девятнадцатого элемента И соединены с выходами седьмого и восьмого элементов И, первый и второй входы двадцатого элемента И подключены к выходам девятого и двенадцатого элементов И, первый и второй входы двадцать первого элемента И соединены с выходами восьмого и тринадцатого элементов И, выход шестнадцатого элемента И подключен к первому выходу блока и первому входу третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом пятнадцатого элемента И и третьим входом блока, выход пятнадцатого элемента И подключен ко второму выходу блока, первый и второй входы и выход четвертого элемента ИЛИ соединены соответственно с выходами четырнадцатого и семнадцатого лементов И и четвертым выходом блока, выходы двадцать первого элемента И, девятнадцатого элемента И, пятого элемента ИЛИ, двадцатого элемента И и восемнадцатого элемента И подключены соответственно к пятому, шестому, седьмому, восьмому и девятому выходам блока, а первый и второй входы пятого элемента ИЛИ соединены с выходани восемнадцатого и двадцать перво го элементов И. Операционный блок содержит четыре операционные группы элементов И, ИЛИ и НЕ, каждая из которых включает оди элемент НЕ, два элемента И и два эле мента HJirf, при этом входы элементов НЕ каждой группы соединены со вторым информационным входом блока, первые и вторые.входы первого элемен та И и первого элемента ИЛИ каждой группы подключены соответственно к первому информационному входу блок и выходу элемента НЕ той же группы, выходы первого элемента ИЛИ и первого элемента И каждой группы соединены с первыми входами соответственно второго элемента И и второго элемента ИЛИ той же группы, выход второго элемента И каждой группы подключен ко второму входу второго элемента ИЖ той же группы, вторые входы вторых элементов И первой группы соединены с управляюпщм входом блока вторые входы вторых элементов И второй и четвертой группы подключены к выходам вторых элементов ИЛИ соответственно первой и третьей групп, а выходы вторых элементов ИЛИ второй и четвертой групп соединены с выходом блока. В системах, неотъемлемым звеном которых является человек, оцениваюпщй информацию и принимающий решение логический алгоритм управления задается в лингвистической форме. Например, если на вход системы поступают параметры объекта: температура и влажность (20С, 80%), то на входе формируются терм-значения лингвкстических переменных температура и влажность : низкое, нормальное, высокое и очень высокое. Логический алгоритм в лингвистической форме задается в этом случае следующим образом: ЕСЛИ ТЕМПЕРАТУРА ВЫСОКАЯ, ТО ВЛАЗК НОСТЬ НИЗКАЯ: to ..., ТО ДАВЖНИЕ НОРМАЛЬНОЕ. Лингвистическое условие (ЕСЖ ТЕМПЕРАТУРА ВЫСОКАЯ,ЕСЛИ ВЛАЖНОСТЬ НИЗКАЯ) интерпретируется в прототипе последовательностью элементарных (бинарных) логических условий, которые реализуются (проверяются) последовательно. Использование вновь введенных элементов, блоков и связей между ними в сочетании со страничной организацией первого блока памяти. 4 в которой в каждой странице хранятся значения одной лингвисти 1еской переменной, а в каждой зоне - терм-значение (адрес страницы определяется содержимым счетчика адреса, а адрес ячейки соответствующей страницы определяется значением регистра адреса) позволяет обеспечивать параллельное сравнение элементарных логических условий, задающих условие в лингвистической форме, что увелиывает быстродействие . На фиг, 1 представлена функциональная схема предлагаемого процессора; на фиг. 2 и фиг, 3 - примеры выполнения блока синхронизации и операционного блока соответственно; на фиг. 4 и фиг. 5 - диаграммы переходов счетчика блока синхронизации и временная диаграмма логического процессора соответственно. Устройство содержит первый мультиплексор 1, регистр 2 адреса, первый блок 3 памяти, первый регистр 4 числа, элементы И 5 первой группы, элементы ИЛИ 6 первой Группы, схему 7 сравнения, регистр 8 кода сравнения, регистр 9 въюода, счетчик 10 адреса, третий блок 11 памяти, третий регистр 12.числа, операционный блок 13 элементы И 14 второй группы, буферный регистр 15, элементы 16 третьей группы, элементы ИЛИ 17 второй группы, второй блок 18 памяти, второй регистр 19 числа, второй мультиплексор 20, блок 21 синхронизации, информационный вход 22 первого мультиплексора 1, выход 23 первого мультиплексора 1, вход 24 регистра 2 адреса, выход 25 регистра 2 адреса, второй адресный вход 26 первого блока 3 памяти, выход 27 первого блока 3 памяти, информационный вход 28 первого регистра 4 числа, выход 29 первого регистра 4 числа, первый вход 30 элементов И 5 первой группы, выход 31 элементов И 5 первой группы, первый вход 32 элементов ИЛИ 6 первой группы, выход 33 элементов ИЛИ 6 первой группы, вход 34 схемы 7 сравнения, выход 35 схемы 7 сравнения, вход 36 регистров 8 кода сравнения, выход 37 регистра 8 кода сравнения, информационный вход 38 регистра 9 вывода, управляющий вход 39 второго мультиплексора 20, выход 40 регистра 9 вывода, являющийся выходом процессора выход 41 счетчика 10 адреса, управляющий вход 42 первого мультиплексоpa 1, первый адресный вход 43 первого блока 3 памяти, первый адресный вход 44 третьего блока 11 памяти, адресный вход 45 второго блока 18 памяти, управляющий вход 46 блока 21 синхронизации, выход 47 третьего блока 11 памяти, информационный вход 48 третьего регистра 12 числа, выход 49 третьего регистра 12 числа, первый информационный вход 50 операционного блока 13, информационный вход 51 буферного регистра 15, выход 52 операционного блока 13, первый вход 53 элементов ИЛИ 17 второй группы, выход 54 элементов ИЛИ 17 второй группы, первый вход 55 элемен тов И 16 третьей группы, выход 56 элементов И 16 третьей группы, управ ляющий вход 57 буферного регистра 15 выход 58 буферного регистра 15, второй информационньй вход 59 операцион ного блока 13, первый вход 60 элементов И 14 второй группы, выход 61 элементов И 14 второй группы, второй вход 62 элементов ШШ 6 первой группы, выход 63 второго блока 18 памяти информационный вход 64 второго регистра 19 числа, выход 65 второго регистра 19 числа, информационный вход 66 второго мультиплексора 20, выход 67 второго мультиплексора 20, второй адресный вход 68 третьего блока 11 памяти, первый выход 69 бло ка 21 синхронизации, второй выход 70 блока 21 синхронизации, установочный вход 71 счетчика 10 адреса, счетный вход 72 счетчика 10 адреса, третий выход 73 блока 21 синхронизации, управляющий вход 74 первого блока 3 памяти, управляющий вход 75 первого регистра 4 числа, управляющий вход 7 второго блока 18 памяти, управляющий вход 77 второго регистра 19 числа, четвертый выход 78 блока 2t синхрони зации, управляющий вход 79 третьего блока 11 памяти, управляющий вход 80 третьего регистра 12 числа, второй вход 81 элементов И 5 первой группы, пятый выход 82 блока 21 синхронизаци управляющий вход 83 операционного, блока 13, шестой выход 84 блока 21 синхронизации, второй вход 85 элементов И 14 второй группы, седьмой выход 86 блока 21 синхронизации, второй вход 87 элементов И 16 третье группы, восьмой выход 88 блока 21 синхронизации, управляклдай вход 89 регистра 9 вывода, девятый выход 90 блока 21 синхронизации, второй 54. 10 вход 91 элементов ИЛИ 17 второй группы, тактовый вход 92 блока 21 синхронизации, счетчик 93 блока 21 синхронизации, элементы НЕ 94 - 97 блока 21 синхронизации, элементы И 98, 99 блока 21 синхронизации, элементы НЕ 100, 101 блока 21 синхронизации, элементы И 102, 103 блока 21 синхронизации, элемент НЕ 104 блока 21 синхронизации, элементы ИЛИ 105, 106 блока 21 синхронизации, элементы И 107-123 блока 21 синхронизации, элементы ИЛИ 124-126 блока 21 синхронизации, элементы НЕ 127-130.операционного блока 13, элементы И 132, i 134, 136 операционного блока 13, элементы ИЛИ 131, 133, 135, 137 элементы И 138, 139 оЪерационного блока 13, элемент ИЛИ140, элемент И 141, элемент ИЛИ 142, элемент И 143, элемент ШШ 144, эле146 операцимент И 145, элемент ИЛИ онного блока 13. 1) соЛогический процессор держит первый мультиплексор 1, регистр 2 адреса, первый блок памяти 3, первый регистр 4 числа, элементы И 5 первой группы, элементы ШШ 6 первой группы, схему 7 сравнения, реЬистр 8 кода сравнения, регистр 9 вывода, счетчик 10 адреса, третий блок 1t памяти, третий регистр 12 числа, операционный блок 13, элементы И 14 второй группы, буферный регистр 15, элементы И 16 третьей группы, элементы ИЛИ 17 второй группы, второй блок 18 памяти, второй регистр 19 числа, второй мультиплексор 20, блок 21 синхронизации. Информационным входом устройства является вход 22 первого мультиплексора 1, выход 23 которого подключен ко входу 24 регистра 2 адреса. Выход 25 регистра 2 адреса соединен со вторым адресным входом 26 первого блока 3 памяти. Выход 27 блока 3 памяти подключен к информационному входу 28 регистра 4 числа, выход которого подключен к первому входу 30 элементов И 5 первой группы. Выход 31 элементов И 5 первой группы соединен с первым входом 32 элементов ИЛИ 6 первой группы, выход 33 которой подключен к входу 34 схемы 7 сравнения. Выход 35 схемы 7 сравнения подключен к входу 36 регистра 8 кода сравнения, выход 37 которого подключен к информационному входу 38 регистра 9 вывода и. управляющему входу 39 второго мультиплексора 20. Выход 40 регистра 9 вывода является выходом устрой ства. Выход 41 счетчика 10 адреса подключен к управляющему входу 42 первого мультиплексора 1, первому адресному входу 43 первого блока 3 памяти, первому адресному входу 44 третьего блока 11 памяти, адресному входу 45 второго блока 18 памяти и управляющему входу 46 блока 21 синхронизации. Выход 47 третьего блока 11 памяти подключен к информационному входу 48 третьего регистра 1 числа, выход 49 которого подключен к первому информационному входу 50 операционного блока 13 и информацио ному входу 51 буферного регистра 15 Выход 52 операционного блока 13 сое динен с первым входом 53 элементов ИЛИ 17 второй группы. Выход 54 элементов ИЛИ 17 второй группы подключен к первому входу 55 элементов И 16 третьей группы, выход 56 которой соединен с управляющим входом 57 буферного регистра 15. Выход 58 буферного регистра 15 соединен со вторым информационным входом 59 операционного блока 13 и пер вым входом 60 элементов И 14 второй группы. Выход 61 элементов И 14 второй группы соединены со вторым входом- 62 элементов ИЖ 6 первой группы. Выход 63 второго блока 18 памяти подключен к информационному входу 64 второго регистра 19 числа, выход 65 которого подключен к инфор мационному входу 66 второго мультиплексора 20. Выход 67 второго мульт плексора 20 соединен со вторым адре ным входом 68 третьего блока 11 памяти. Первьй и второй выходы 69 и 70 блока 21 синхронизации подключены соответственно к установочному и счетному входам 71 и 72 счетчика 10 адреса. Третий выход 73 блока 21 синхронизации соединен с упра ляющим входом 74 первого блока 3 памяти, управляющим входом 75 перво го регистра 4 числа, управляющим вх дом 76 второго блока 18 памяти и управляющим входом 77 второго регис ра 19 числа. Четвертый выход 78 бло ка 21 синхронизации подключен к упр ляющему входу 79 третьего блока 11 памяти, управляющему входу 80 треть го регистра 12 числа, второму вхолу 81 элементов И 5 первой группы. Пятый выход 82 блока 21 синхронизац соединен с управляющим входом 83 оп рационного блока 13. Шестой выход 84 блока 21 синхронизации соединен со вторьм входом 85 элементов И 14 второй группы. Седьмой выход 86 блока 21 синхронизации подключен ко второму входу 87 элементов И 16 третьей группы. Восьмой выход 88 блока 21 синхронизации соединен с управляющим входом 89 регистра 9 вывода. Девятый выход 90 блока 21 синхронизации подключен ко второму входу 91 злементов ИЛИ 17 второй группы. Вход 92 блока 21 синхронизации является тактовым. Блок 21 синхронизации (фиг. 2) содержит счетчик 93, семь элементов НЕ 94, 95, 96, 97, 100, 101, 104, двадцать один элемент И 98, 99, 102, 103, 107-123 и пять элементов ИЛИ 105, 106, 124, 125, 126. Первый, второй и четвертый информационные входы счетчика 93 соединены с шиной нулевого потенциала, а третий информационный вход соединен с шиной единичного потенциала. Первый, второй, третий и четвертый выходы счетчика 93 подключены соответственно к входам первого 94, второго 95, третьего 96, четвертого 97 элементов НЕ. Первый, второй, третий .и четвертый входы и выход первого 98 элемента И соединены соответственно с выходами первого 94, второго 95, третьего 96 элементов НЕ, четвертым выходом счетчика 93 и входом пятого 100 элемента НЕ. Первый, второй, третий и четвертый входы и выход второго 99 элемента И подключены соответственно к выходу первого 94 элемента НЕ, второму выходу счетчика 93, третьему выходу счетчи-. ка 93, выходу четвертого 97 элемента НЕ и входу шестого 101 элемента НЕ. Входы и выход первого 105 элемента ИЛИ соединены соответственно с управляющим входом 46 блока синхронизации и входом седьмого 104 элемента НЕ. Первый и второй входы и выход третьего 102 элемента И подключены соответственно к входам второго 99 элемента И и седьмого 104 элемента НЕ и первому входу второго 106 элемента ИЛИ, второй вход которого соединен с выходом шестого 101 элемента НЕ. Первый, второй и третий входы и выход четвертого 103 элемента И подключены соответственно к выходу второго 99 элемента И, тактовому 92 входу блока, выходу первого 105 элемента ИЛИ и синхровходу счетчи13. 1 ка 93. Первый и второй входы н выход пятого 107 элемента И соединены соответственно с тактовым 92 входом блока, выходом первого 98 элемента И и входом сброса счетчика 93. Первый,, второй и третий входы и выход шестого 108 элемента И подключены соответственно к тактовому 92 вхо ду блока, выходу пятого 100 элемента НЕ, выходу второго 106 элемента ИЛИ и счетному входу счетчика 93. Первый и второй входы седьмого 109 элемента И соединены с выходами третьего 96 и четвертого 97 элементов Н Первый и второй входы восьмого 110 элемента И подключены к выходу четвертого 97 элемента НЕ и третьему выходу счетчика 93. Первый и второй входы девятого 111 элемента И соединены с четвертым выходом счетчика 93 и выходом третьего 96 элемента НЕ. Первый и второй входы десятого 112 элемента И подключены к первому и второму выходам счетчика 93. ПервьА и второй входы один1 д1датого 113 элемента И соединены с выходом второ го 95 элемента НЕ и первым выходом счетчика 93. Первый и второй входы двенадцатого 114 элемента И подключе ны к выходам первого 94 и второго 95 элементов НЕ. Первый и второй входы тринадцатого 115 элемента И соединены с выходом первого 94 элемента НЕ и вторым выходом счетчика 93. Первый и второй входы четырнадцатого 116 элемента И подключены к выходам седь МОго 109 и тринадцатого 115 элементов И. Первый и второй входы пятнадцатого 117 элемента И подключены к выходам седьмого 109 и одиннадцатого 113 элементов И. Первый и второ входы шестнадцатого 118 элемента И подключены к выходам восьмого 110 и двенадцатого 114 элементов И. Первый и второй входы семнадцатого 119 элемента И соединены с выходами вось мого 110 и одиннадцатого 113 элементов И. Первый и второй входы восемнадцатого 120 элемента И подключены к выходам седьмого 109 и десятого 11 элементов И. Первый и второй входы девятнадцатого 121 элемента И соединены с выходами седьмого 109 и восьмого МО элементов И. Первый и второ входы двадцатого 122 элемента И подключены к выходам девятого 111 и двенадцатого 114 элементов И. Перйый и второй входы двадцать первого 123 элементу И соединены с выходами вось 541 мого 110 и тринадцатого 115 элементов И. Выход шестнадцатого 118 элемента И подключен к первому 69 выходу блока и первому входу третьего 124 элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом пятнадцатого 117 элемента И и третьим 73 выходом блока. Выход пятнадцатого 117 элемента И подключен ко второму 70 выходу блока. Первый и второй входы и выход четвертого 125 элемента ИЛИ соединены соответственно с выходами четырнадцатого 116 и семнадцатого 119 элементов И и четвертым 78 выходом блока. Выходы двад-, цать первого 123 элемента И, девятнадцатого 121 элемента И, пятого 126 элемента ИЛИ, двадцатого 122 элемента И и восемнадцатого 120 элемента И подключены соответственно к пятому 82, шестому 84, седьмому 86, восьмому 88 и девятому 90 выходам блока. Первый и второй входы пятого 126 элемента ИЛИ соединены с выходами восемнадцатого 120 и двадцать первого 123 элементов И. Операционный блок 13 (фиг, 3) содержит четыре операционных группы элементов И, ИЛИ и НЕ, каждая-из которых включает один элемент НЕ 127 130, два элемента И 132, 134, 136, 138, 139, 141, 143, 145 и два элемента ИЛИ 131, 133, 135, 137, 140, 142, 144, 146. При этом входы элементов НЕ 127 -.130 соединены со вторым информационным 59 входом блока. Первые и вторые входы первых элементов И 132, 134, 136, 138 и первьпс элементов ИЛИ 131, 133, 135, 137 подключены соответственно к первому информационному 50 входу блока и выходам элементов НЕ 127-130 своей группы. Выходы первых элементов ИЛИ 131 133, 135, 137 и первых элементов И 132, 134, 136, 138 соединены с первыми входами соответственно вторых элементов И 139, 141, 143, 145 и вторых элементов ИЛИ 140, 142, 144, 146 своей группы. Выход вторых элементов И 139, 141, 143, 143 подключен ко вторым входам вторых элементов ИЛИ 140, 142, 144, 146 своей группы. Вторые входы вторых элементов И первой и третьей групп 139, 143 соединены с управляющим входом блока. Вторые входы вторых элементов И второй и четвертой группы 141, 145 подключены к выходам вторых элементов ИЛИ 140, 144 соответственно перВОЙ If третьей группы. Выходы вторых Элементов ИЛИ 142, 146 второй и четвертой групп соединены с выходом 52 блока. Логический процессор работает следующим образом. Третий 11 блок памяти имеет страничную организацию. Страничная организация третьего 11 блока памяти, где в каждой странице хранятся решения системы по одной лингвистической переменной, а в каждой зоне - множество этих решений, адрес страницы определяется значением счетчика 10 адреса, а адрес ячейки в соответствзпощей странице определяется значением второго 19 регистра числа, позволяет осуществить преобразование решения системы из лингвистической фогмы в числовую. Для страничной организации первого 3 и третьего 11 блоков памяти один набор адресных входов блоков памяти условно разбит на два: старшие разрядЫ адреса (первый адресный вход) определяет номер страницы, а второй адресный вход (младшие разряды адреса) определяют ячейку в странице. Управляющий вход является входом Чтение. Во втором 18 блоке памяти хранятся значения входных параметров из множества параметров, характеризующих состояние объекта, при которых функция принадлежности лингвистических переменных к терм-значениям макси- 5 мальна. В первом такте по сигналу с выхода 69 блока 21 синхронизации счетчик 10 адреса устанавливается в N. Таблица истинности счетчика 10 адреса.

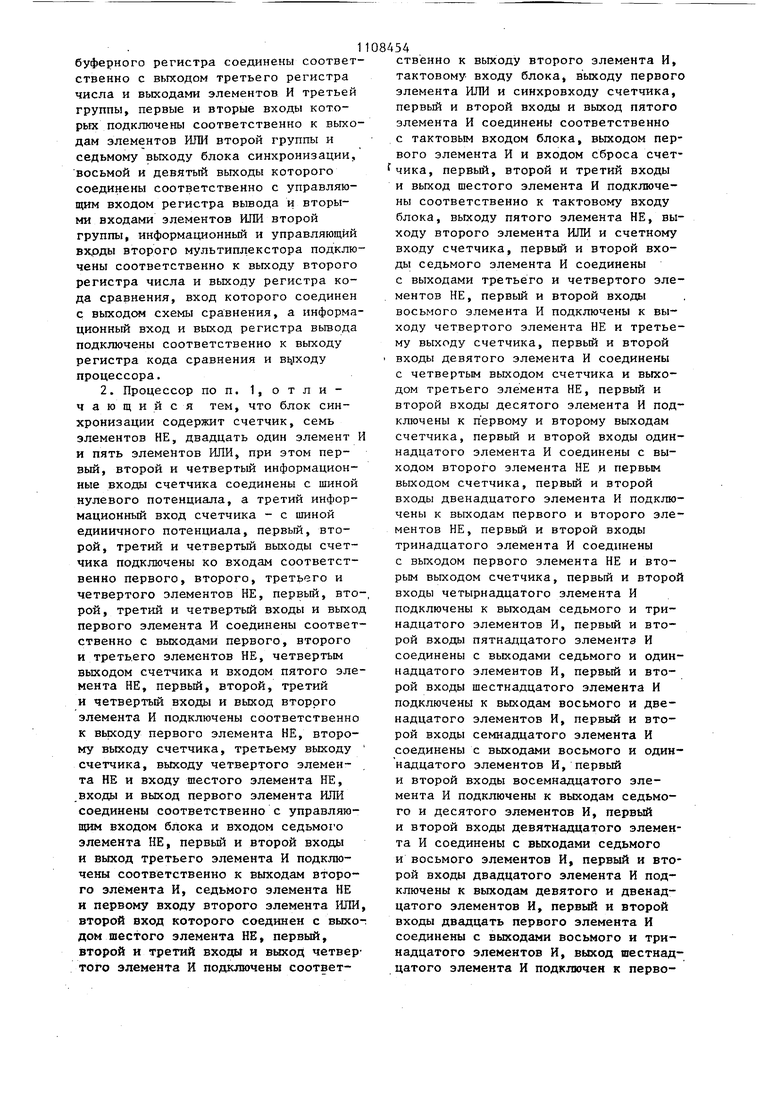

N

О 1 1 1

N N N N

1

N-1

О О О N-2 N-3 110845А ад пам ёло на и в пр чер пл О 0 0 0 1 1 1 1 X ра ет ре

Х(хранение предыдущего состояния)

Х (запись нового состояния) Продолжение таблицы I 2 г 1 4 1 Г о 1 Выходное значение 41 счетчика 10 еса поступает на вход 43 блока 3 яти, выбирая страницу, на вход 45 ка 18 памяти, выбирая ячейку, вход 46 блока 21 синхронизации ход 42 первого мультиплексора 1, пуская значенй. N-ro параметра ез первый мультиплексор 1. Таблица истинности первого мультиксора 1. ООУ1ХХХХХХХУ1 01 X У2 X X X X X X У2 10ХХУЗХХХХХУЗ 11ХХХУ4ХХХХУ4 00ХХХХУ5ХХХУ5 01ХХХХХУ6ХХУ6 10ХХХХХХУ7ХУ7 11ХХХХХХХУ8У8 безразличное состояние С выхода 23 первого мультиплексо1 значение N-ro параметра поступана вход 24 регистра 2 адреса. Таблица истинности регистра 2 ада. Эта таблица истинности относится так же к регистрам 4, 19, 12 числа, регистру 8 кода сравнения, регистру 9 вывода и буферному регистру 15. Для регистра 2 адреса и регистра 8 кода сравнения управляющий вход жест ко соединен с сигналом. Лог. 1. С выхода 25 регистра 2 адреса информации поступает на вход 26 блока памяти 3. В этом же также по сигналу с выхо да 73 блока 21 синхронизации, поступающему на вход 74 блока 3 памяти, вход 76 блока 18 памят, вход 75 регистра 4 числа и вход 77 регистра 19 числа происходит чтение информации и блоков 3 и 18 памяти соответственно на регистры 4 и 19, входы 28, 64. На регистре 4 числа - функции принадлеж ности значения входного параметра дл термов N-ой лингвистической переменной, а на регистре 19 числа - значения входной переменной для всех термов, при которых функция принадлежности максимальна. , Во втором .такте по сигналу с выхода 78 блока 21 синхронизации, поступающему на вход 81 элементов И 5 первой группы, на вход 79 блока 11 ПШ4ЯТИ и вход 80 регистра 12 числа происходит следующее. Информация с выхода 31 элементов И 5 первой группы поступает на вход 32 элементов ИЛИ 6 первой группы, с выхода 33 элементов ШШ 6 первой группы на вход 34 схемы 7 сравнения. Схема 7 сравнения вьшвляет максимальное значение функций принадлежности для все термов. Выход 35 схемы 7 сравнения имеет разрядность равную числу термов. Логическая единица появляется на том разрядном выходе, где функция принадлежности максимальна. Через вход 36 эта единица записывается в регистр 8 кода сравнения. Выход 37 регистра 8 кода сравнения подключается ко входу 39 второго мультиплексора 20 и тем самым пропус кает адрес на вход б8 блока 11 памяти . С выхода 47 блока 11 памяти происходит считывание через вход 48 на регистр 12 числа решений для известных значений лингвистической перемен ной и терма, к которому ее отнесли. В третьем такте по сигналам с выхода 90 блока 21 синхронизации, поступакиццм соответственно на вход 9 элементов ИЛИ 17 второй группы и на вход 87 элементов И третьей группы 1 4 и по образовавшемуся разрешающему сигналу на входе 57 буферного регистра 15, информация с выхода 49 регистра 12 числа записьгеается в буферный регистр 15 через вход 51. В четвертом такте по сигналу с выхода 70 блока 21 синхронизации на вход 72 счетчика 10 поступает сигнал вычета единицы, т.е. осуществляется переход к следующему параметру системы и, соответственно, к следующей странице блоков 3 и 11 памяти. По сигналу с выхода 73 блока синхронизации происходит выборка функций принадлежности из блока 3 памяти и зна- , чения параметра, при котором функция принадлежности максимальна, иэ блока 18 памяти аналогично первому такту. Пятый такт аналогичен второму, но производится на следующем входном параметре. В шестом такте происходит сравнение значений решений системы в лингвистической форме для входного параметра, хранящегося в буферном регистре 15 и считанного в регистр числа. По сигналу с выхода 82 блока 21 синхронизации, поступающего на вход 83 операционного блока 13 информация с выхода 49 регистра 12 числа и выхода 58 буферного регистра 15 поступает соответственно на входы 50, 59 операционного блока 13. На выходе 52 операционного блока 13 имеются минимальные решения системы из сравниваемых. Минимальные решения поступают на входы элементов ИЛИ 17 второй группы, а с ее выхода 54 записываются в буферный регистр 15 аналогично третьему такту. Содержимое счетчика 10 адреса во время работы устройства поступает на вход 46 блока 21 синхронизации, в шестом такте производится анализ его на нуль. При неравенстве счетчика 10 адреса нулю, управление передается четвертому такту, т.е. происходит ввод и анализ значения следующего параметра системы. Если счетчик 10 адреса равен нулю, т.е. анализ всех параметров системы произведен, то управление передается седьмому такту. В седьмом такте производится выбор решения для системы. По сигналу с выхода 84 блока 21 синхронизации, поступающему на вход 85 элементов И 14 второй группы с выхода 58 буферного регистра 15 минимальные решения системы в лингвистической форме поступают на вход 60 элементов И 14 второй группы, а с ее выхо да 61 - на вход 62 элементов ИЛИ 6 первой группы, с вьпсода 33 элементов ИЛИ 6 первой группы - на вход 3 схемы сравнения 7; таким образом, в регистре кода сравнения 8 оказыва ется записанной логическая единица в том разряде, который соответствуе максимальному значению решения сист мы из минимальных. В восьмом такте производится эАпись окончательного решения в регистр 9 вывода. По сигналу с выхода 88 блока 21 синхронизации решени системы с выхода 37 регистра кода сравнения поступает на регистр 9 вы да по входу 38. Таблица истинности блока 21 синх низации. Выходы блока 21 синхрон Состояние зации счетчика 69J70 73| 78 82|84|86|88Г90 0000000000000 0001101000000 0010000100000 0011000000101 010001 1000000 0101000100000 0110000010100 0111000000100 10000000000 10 Описанный логический процессор может использоваться в системах управления, для которых точная мате матическая модель функционирования объекта управления не известна, например в системах прогнозирования с учетом большого числа параметров, в системах управления технологическими процессами, в процессе биосинтеза антибиотиков, экспресс-диагностика и т.д. Реализация возможности принятия решения в условиях неопределенности позволяет облегчить труд человекаоператора данного класса систем, повысить их быстродействие, надежность и качество принимаемых решений, Время, необходимое для обработки редлагаемых логическим процессоом N параметров, равно Тл,пр (5 + 3N)t, де N - число параметров, характеризующих состояние объекта; t - период тактовых импульсов. Время, необходимое для обработи N параметров прототипом, равно Т„р 2(m-1), где N - число параметров, характеризующих состояние объекта; m - число элементов множества, представлякнцего терм-значение ; t - период тактовых импульсов. Если число входных параметров, арактеризующих объект , , 2 МКС, то МКС, ТА. МКС. Таким образом, предлагаемый логиеский процессор дает значительный ыигрьш в быстродействии по сравнеию с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ бальнеотерапии больных остеоартритом с сопутствующей гипертонической болезнью | 2021 |

|

RU2817309C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Балашов Е.П | |||

| и др | |||

| Многофункциональные регулярные вычислительные структуры | |||

| И | |||

| Советское радио, 1978, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

Авторы

Даты

1984-08-15—Публикация

1982-06-19—Подача