Изобретение относится к цифровой вычислительной технике и может быть использовано для классификации ситу- ащш в многопараметрических системах, для которых точная математическая модель функционирования объекта управления неизвестна.

Целью 13обретения является сокращение аппаратурных затрат путем сокращения требуемого объема памяти.

В системах, неотъемлемым звеном которых является человек, оценивающий информацию и принимающий решение, логический алгоритм управления задается в лингвистической форме. Например, если на вход системы поступают параметры объекта - интервалы времени между сбоями в блоках некоторой системы, то на входе формируются терм- значения лингвистической переменной Частота сбоев блока: Очень редко, Редко, Часто и т.п.

Логический алгоритм в лингвистической форме задается в этом случае следующим образом: если блок Б1 сбоит часто, то..., если блок Б2 сбоит ,очень редко, то..., то заменить блок БГ . .

Для преобразования значения входного параметра в лингвистическую форму в известном устройстве необходимо хранить степени принадлежности входного значения ко всем лингвистическим значениям. Однако входное значение

имеет ненулевую степень принадлежнос- 35и 37-57, семь элементов НЕ 58-64 и

ти лишь к некоторь м лингвистическимпять элементов ИЛИ 65-69. значениям. Например, для интервала Блок 20 синхронизации имеет тактовремени 2,5 ч принадлежность к линг-вый вход 70,вход 71 пуска, выходы

вистическим значениям может задавать-72-80 с первого по девятый.

ся следующим образом: 0,4/ 0чень ко, 0,9/ Редко, 0,2/ Средне, О/ Часто, 0/ 0чень часто.

Хранение всех, в том числе и нулевых, степеней принадлежности обуславливает большой объем требуемой па- мяти и приводит к значительным аппаратурным затратам в целом.

селекции содержит демуль- 81 и группы 82 элементов

Блок 21 типлексоры ИЛИ.

Блок 21 селекции имеет информаци- онньй вход 83, управляющий вход 84 и выход 85.

Логический процессор работает следующим образом. I

Использование вновь введенных бло- ка селекции, шифратора и новых свя- 50 зей в сочетании со страничной организацией второго блока памяти, где в йаждой ячейке хранятся имеющие из терм-значений, имеющих ненулевую сте-- пень принадлежности к входному значе- 55 нию, позволяет исключить хранение ненулевых степеней принадлежности, что приводит к сокращению аппаратурных затрат.

5

0

5

0

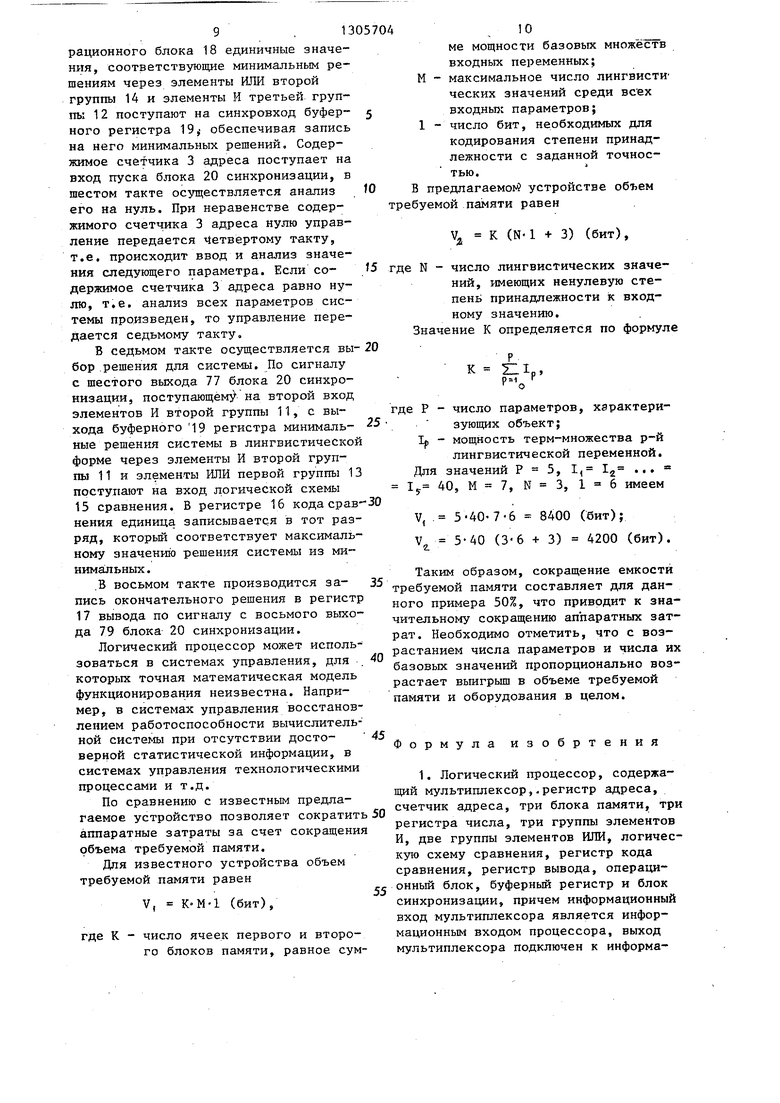

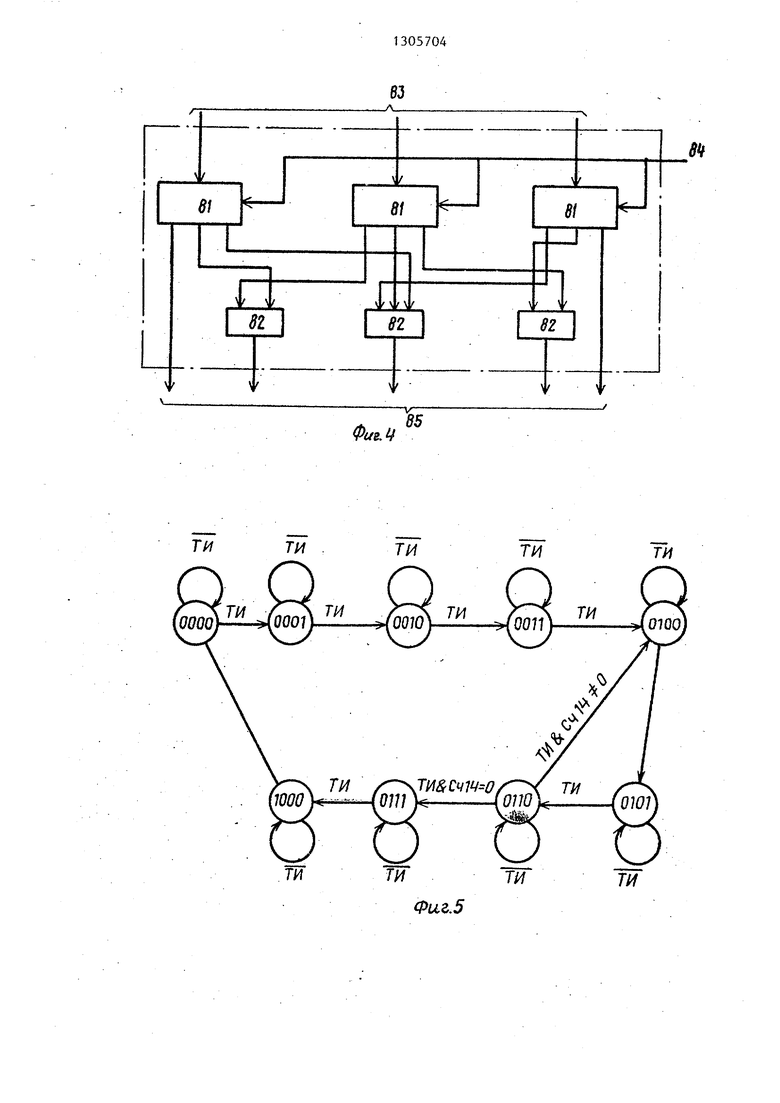

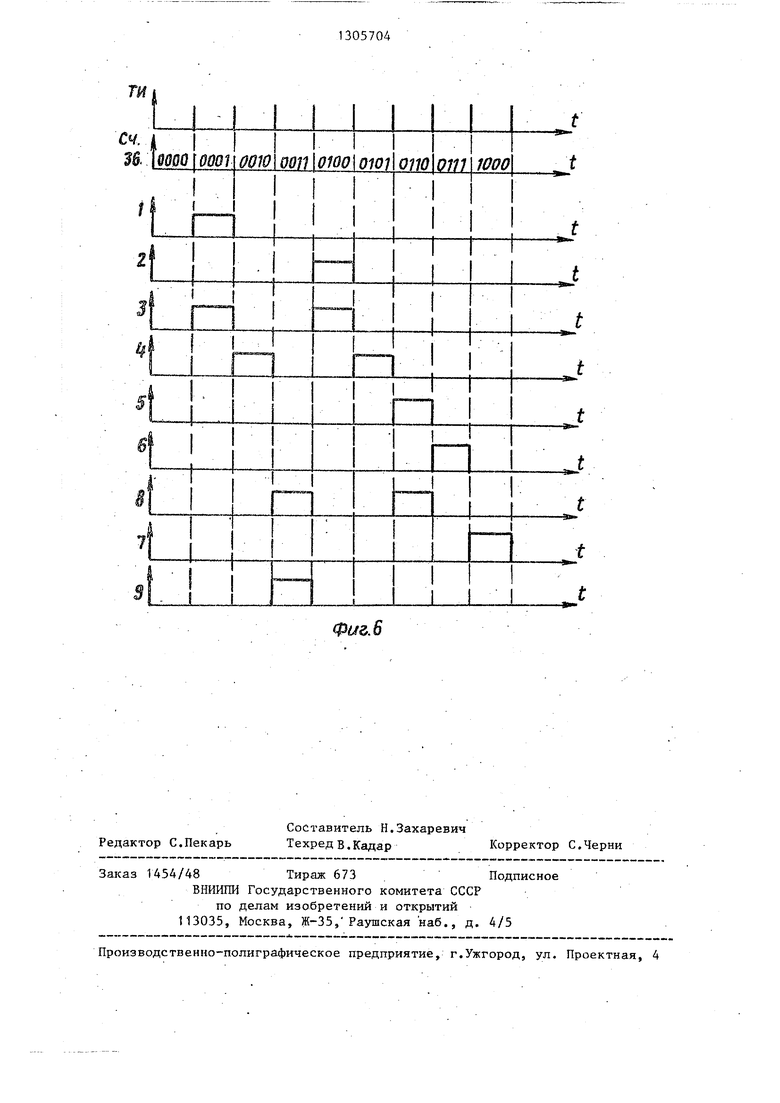

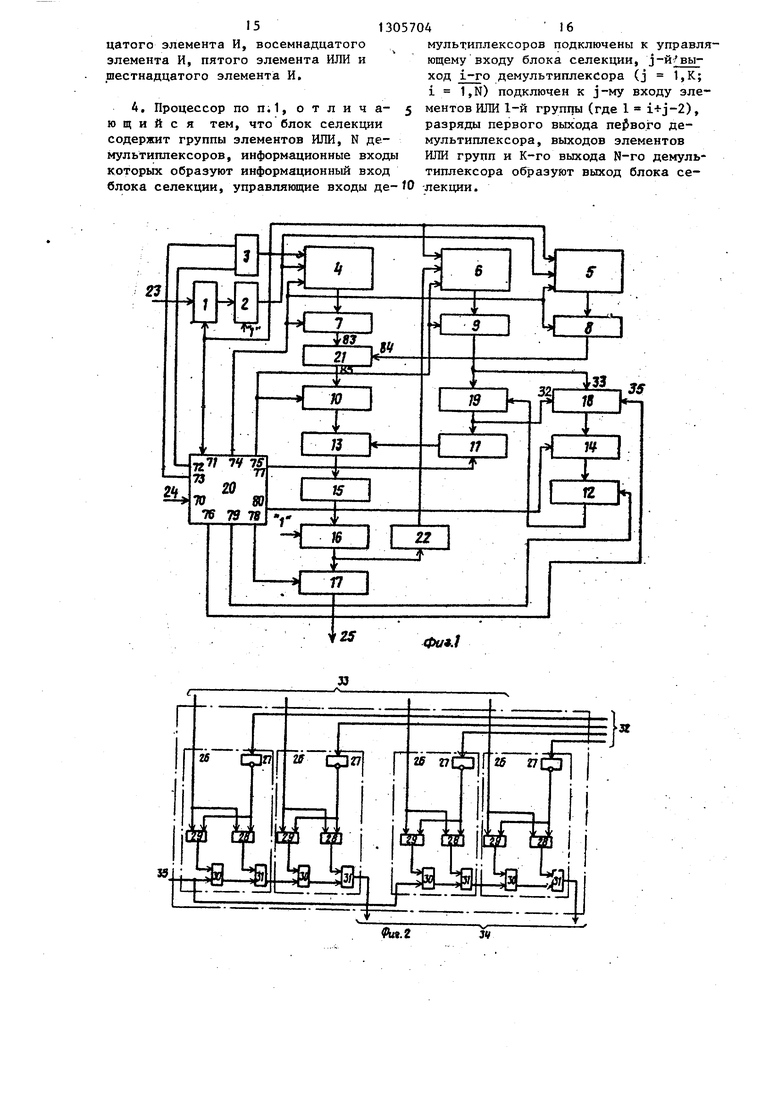

На фиг.1 представлена структурная схема логического процессора; на фиг.2-4 - функциональные схемы операционного блока, блока синхронизации и блока селекции соответственно; на фиг.5 и 6 - диаграмма переходов счетчика блока синхронизации и временная диаграмма логического процессора соответственно.

Логический процессор содержит мультиплексор 1, регистр 2 адреса, счетчик 3 адреса, три блока 4-6 памяти, три регистра 7-9 числа, три группы 10-12 элементов И, две группы 13 и 14 элементов ИЛИ, логическую схему 15 сравнения, регистр 16 кода сравнения, регистр 17 вывода, операционный блок 18, буферный регистр 19, блок 20 син- .хронизации, блок 21 селекции и шифратор 22.

Логический процессор имеет инфор- мационньш вход 23, тактовый вход 24 и выход 25 номера решения.

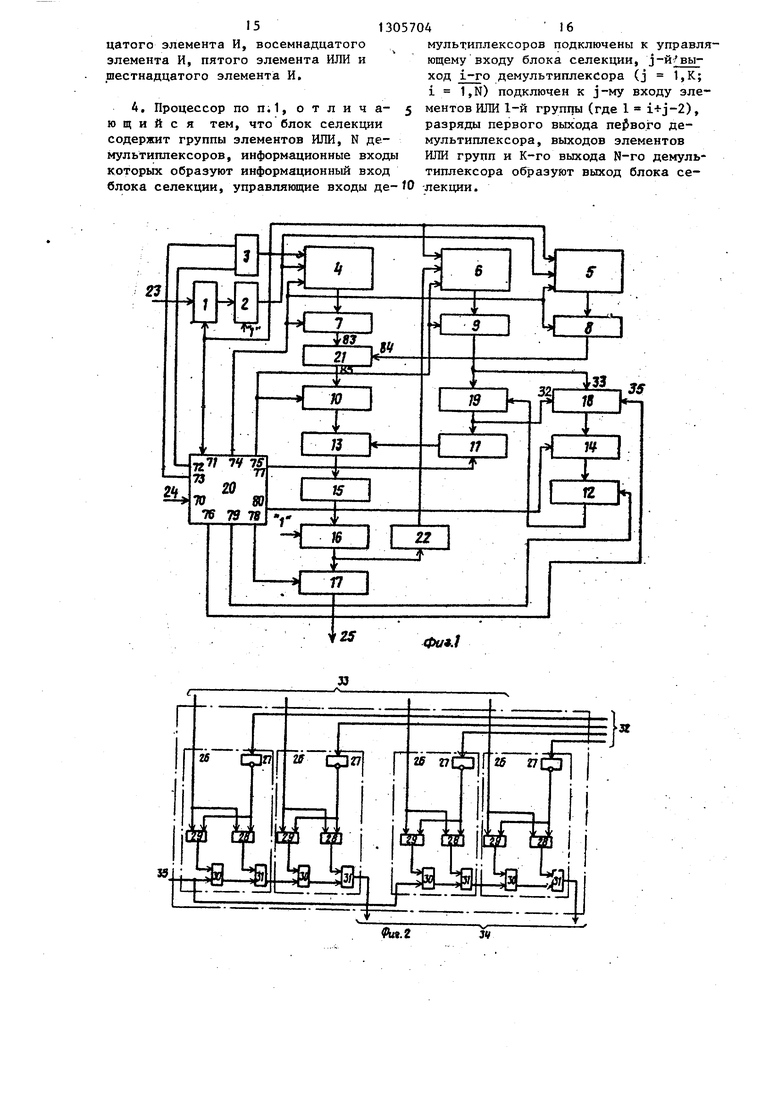

Операционный блок 18 содержит Р групп по N операционных узлов 26, каждый из которых содержит элемент НЕ 27, входные элементы И 28 и ИЛИ 29 и выходные элементы И 30 и РШИ 31.

Операционный блок 18 имеет первый 32 и второй 33 информационные входы, информационный 34 выход и стробирую- щий 35 вход.

Блок 20 синхронизации содержит счетчик 36, двадцать один элемент

селекции содержит демуль- 81 и группы 82 элементов

Блок 21 типлексоры ИЛИ.

Блок 21 селекции имеет информаци- онньй вход 83, управляющий вход 84 и выход 85.

Логический процессор работает следующим образом. I

Первый 4, второй 5 и третий 6 блоки памяти имеют страничную организацию. Для страничной организации блоков памяти их адресный вход .условно разбит на две группы: старшие разряды адреса определяют ячейку в странице. Номер страншды первого 4, вто- рого 5 и третьего 6 блоков памяти определяется содержимым счетчика 3 адреса, т.е. номером входного парамет- ра. Номер ячейки в странице для первого 4 и второго Ь блоков памяти определяется содержимым регистра 2 адреса, на который заносится числовое значение входного параметра.

Слово первого блока 4 памяти сое- тоит из N полей, где N - число лингвистических значений, имеющих ненулевую степень принадлежности к числовому значению входной переменной. Содержимое каждого поля представляет собой значение степени принадлежности входного числового значения к соответствующему лингвистическому значению (терм-значению).

Во втором блоке 5 памяти хранят- ся наименьшие терм-значения, для которых входное числовое значение имеет ненулевую степень принадлежности.ПредО 1 2 3

1

О О

О

Выходное значение счетчика 3 адреса поступает на разряды старшей груп- г пы адресного входа первого 4, второго 5 и третьего 6 блоков памяти, вы- бирая страницу, на адресный вход мультиплексора 1 и вход пуска блока 20 синхронизации. При этом на выход п

полагается, что терм-значенияупорядочены в соответствии с их семантикой. Например, для входного парамет- .ра Температура терм-значения упорядочены следующим образом: Очень низкая, Низкая, Средняя, Высокая, Очень высокая.

В каждой странице третьего блока 6 памяти хранятся решения лингвистической переменной, а в каждой зоне - множество этих решений.

В первом такте посигналу с первого выхода 72 блока20 синхронизации счетчик 3 адресаустанавливается в Р.

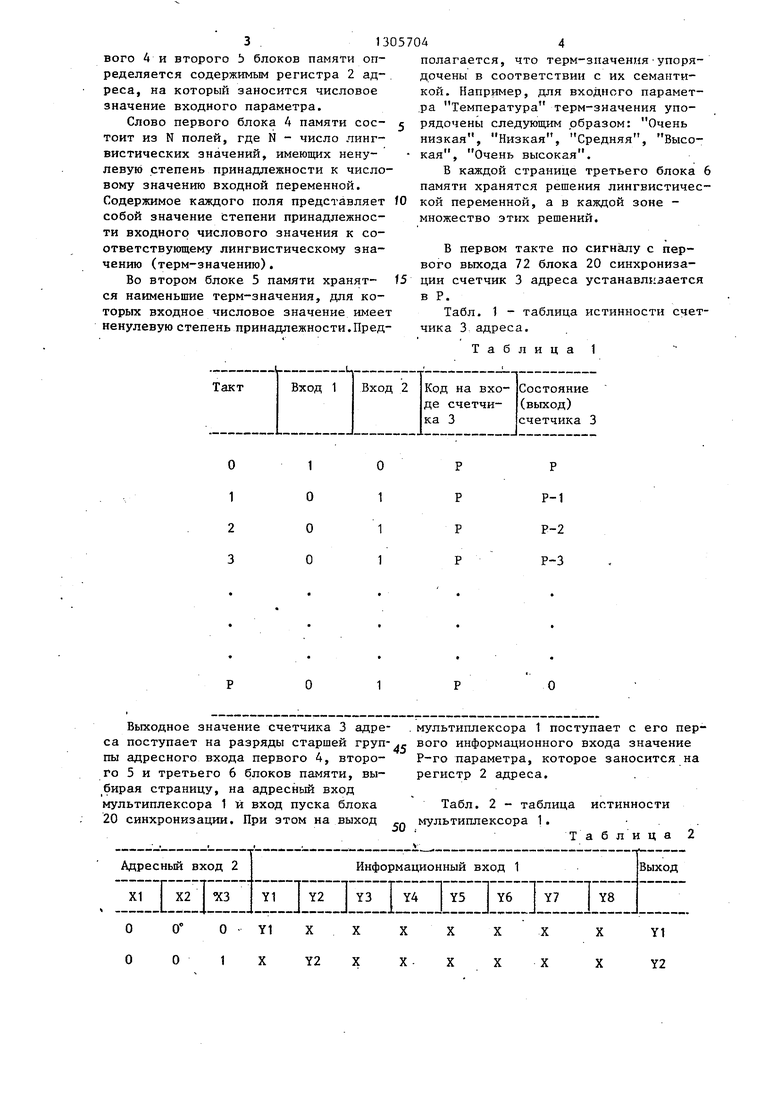

Табл. 1 - таблицаистинности счетчика 3 адреса.

Таблица1

Р Р Р Р

Р Р-1

Р-2 Р-3

мультиплексора 1 поступает с его первого информационного входа значение Р-го параметра, которое заносится на регистр 2 адреса.

Табл. 2 - таблица истинности мультиплексора 1. . .

Таблица 2

Табл. 3 - таблица истинности регистра 2 адреса.25

Т а б л и ц а 3

X(t) X(t-1) (хранение преды- j дущего состояния)

X(t) ) (запись

нового сое- 40 тояния)

Эта таблица истинности относится также к регистрам 7-9 числа, регистру 16 кода сравнения, регистру 17 вьшода и буферному регистру 19. Для регистра 2 адреса и регистра 16 кода сравнения синхровход жестко соединен с шиной логической единицы.

С выхода регистра 2 адреса информация поступает на разряды младшей группы адресного входа первого 4 и

5

0

0

5 0

второго 5 блоков памяти, выбирая тем самым ячейку в странице. В этом же такте по сигналу с третьего выхода 74 блока 20 синхронизации, поступающему на входы чтения первого 4 и вто- рого 5 блоков памяти и синхровходы первого 7 и второго 8 регистров числа, осуществляется чтение информации из блоков 4 и 5 памяти на регистры 7 и 8 числа соответственно. На регистре 7 числа - ненулевые значения функции принадлежности числового значения входного параметра к термам р-Й лингвистической переменной, а на регистре 8 числа - меньшее из терм- значений, имеющих ненулевую степень принадлежности к входному значению.

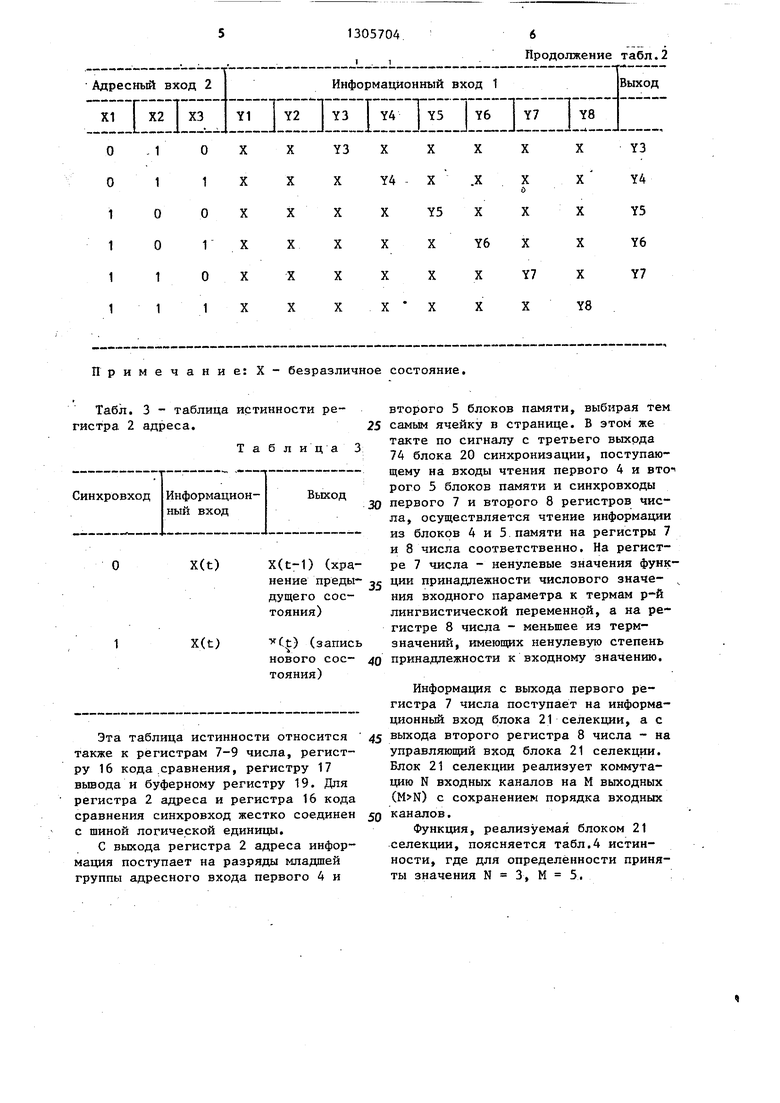

Информация с выхода первого регистра 7 числа поступает на информа- ционньш вход блока 21 селекции, а с выхода второго регистра 8 числа - на управляющий вход блока 21 селекции. Блок 21 селекции реализует коммутацию N входных каналов на М выходных () с сохранением порядка входных каналов.

Функция, реализуемая блоком 21 селекции, поясняется табл.4 истинности, где для определённости приняты значения N 3, М 5,

При этом каждый демультиплексор представляет собой сетку одноразрядных демультиплексоров.

Во втором такте по сигналу с четвертого выхода 75 блока 20 синхронизации, поступающему на второй вход элементов И первой группы 10, вход чтения третьего блока 6 памяти и син- хровход третьего регистра 9 числа, происходит следующее. Информация с выхода блока 21 селекции через элементы И первой группы 10 и элементы ИЛИ первой группы 13 поступает на вход логической схемы 15 сравнения. Схема 15 сравнения выявляет максималь ное значение степени принадлежности для всех термов. Выход, схемы 15 сравнения имеет разрядность, равную числу термов. Логическая единица появляется на том разряде выхода, где функция принадлежности максимальна. В качестве, схемы 15 сравнения может быть использовано известное устройство для сравнения чисел. Эта единица записывается в регистр 16 кода сравнения и с его выхода поступает на вход шифратора 22. На выходе шифратора 22 устанавливается лингвистическое значение р-го входного параметра, которое поступает на разряды младшей группы адресного входа третьего блока 6 памяти, определяя адрес ячейки в странице. Осуществляется чтение из третьего блока 6 памяти на третий регистр 9 числа решений для известных значений лингвистической переменной и терма, к которому необходимо отнести ее значение.

В третьем такте по сигналам с девятого 80 и восьмого 79 выходов бдо-

Таблица 4

0

5

0

5

0

5

0

5

ска 20 синхронизации, поступающим на вторые входы соответственно элементов ИЛИ второй группы 14 и элементов И третьей группы 12 по образовавшемуся разрешающему сигналу на синхро- входе буферного регистра 19 информация с выхода третьего регистра 9 числа записывается в буферный регистр 19,

В четвертом такте по сигналу со второго выхода 73 блока 20 синхронизации, поступающему на счетный вход счетчика 3 адреса, осзтцествляется вычет единицы из его содержимого, тем самым происходит переход к следующе- . му параметру системы и соответственно к следующей странице блоков 4-6 памяти. По сигналу с третьего выхода 74 блока 20 синхронизации происходит выборка функций принадлежностей из блока 4 памяти и минимального терм- значения с ненулевой степенью принадлежности из блока 5 памяти аналогично первому такту.

Пятый такт аналогичен второму, но производится над следующим входным параметром.

В шестом такте происходит сравнение значений решений системы в лингвистической форме для входного параметра, хранящегося в буферном регистре 19 и считанного в регистр 9 числа, По сигналу с пятого выхода 76 блока 20 синхронизации, поступающему на управляющий вход операционного блока 18, из сравниваемых значений на первом и втором информационных входах операционного блока 18, поступающих соответственно с выходов регистра 9 числа и буферного регистра 19, выбираются минимальные. С выхода oneрационного блока 18 единичные значения, соответствующие минимальным решениям через элементы ИЛИ второй группы 14 и элементы И третьей группы 12 поступают на синхровход буфер- ного регистра 19, обеспечивая запись на него минимальных решений. Содержимое счетчика 3 адреса поступает на вход пуска блока 20 синхронизации, в шестом такте осуществляется анализ его на нуль. При неравенстве содержимого счетчика 3 адреса нулю управление передается г1етвертому такту, т.е. происходит ввод и анализ значения следующего параметра. Если со- держимое счетчика 3 адреса равно нулю, т.е. анализ всех параметров системы произведен, то управление передается седьмому такту.

В седьмом такте осуществляется вы- бор .решения для системы. По сигналу с шестого выхода 77 блока 20 синхронизации, поступающем на второй вход элементов И второй группы 11, с выхода буферного 19 регистра минималь- ные решения системы в лингвистической форме через элементы И второй группы 11 и элементы ИЛИ первой группы 13 поступают на вход логической схемы 15 сравнения. В регистре 16 кода срав нения единица записывается в тот разряд, которьй соответствует максимальному значению решения системы из минимальных .

.В восьмом такте производится за- пись окончательного решения в регистр 17 вывода по сигналу с восьмого выхода 79 блока 20 синхронизации.

Логический процессор может использоваться в системах управления, для которых точная математическая модель функционирования неизвестна. Например, в системах управления восстановлением работоспособности вычислительной системы при отсутствии досто- верной статистической информации, в системах управления технологическими процессами и т.д.

По сравнению с известным предлагаемое устройство позволяет сократить аппаратные затраты за счет сокращения объема требуемой памяти.

Для известного устройства объем требуемой памяти равен

V, К-М-1 (бит),

где К - число ячеек первого и второго блоков памяти, равное сумме мощности базовых множеств входных переменных; М - максимальное число лингвистических значений среди вс ех входньп: параметров; 1 - число бит, необходимых для кодирования степени принадлежности с заданной точностью.

В предлагаемого устройстве объем требуемой памяти равен

Vj К (N-1 + 3) (бит),

где N - число лингвистических значений, имеющих ненулевую степень принадлежности к входному значению. Значение К определяется по формуле

К Zli ,

где Р - число параметров, характеризующих объект;

If - мощность терм-множества р-й лингвистической переменной. Для значений Р 5, 1, 1 ... 1;: 40, М 7, N 3, 1 6 имеем

V, . 5-407-6 8400 (бит);

Vy 5-40 (3-6 + 3) 4200 (бит).

Таким образом, сокращение емкости требуемой памяти составляет для данного примера 50%, что приводит к значительному сокращению аппаратных затрат. Необходимо отметить, что с возрастанием числа параметров и числа их базовых значений пропорционально возрастает выигрьш в объеме требуемой памяти и оборудования в целом.

Формула изобртения

1. Логический процессор, содержащий мультиплексор,.регистр адреса, счетчик адреса, три блока памяти, три регистра числа, три группы элементов И, две группы элементов ИЛИ, логическую схему сравнения, регистр кода сравнения, регистр вывода, операционный блок, буферньй регистр и блок синхронизации, причем информационный вход мультиплексора является информационным входом процессора, выход мультиплексора подключен к информационному входу регистра адреса, син- хровход которого подключен к шине логической единицы процессор, разряды выхсда которого подключены к соответствующим разрядам младшей груп- пы адресного входа первого блока памяти, разряды старшей группы адресных входов с первого по третий блоков памяти подключены к соответствующим разрядам выхода счетчика адреса, ад- ресного входа мультиплексора и входа пуска блока синхронизации, первый и второй выходы которого подключены соответственно к установочному и счетному входам счетчика адреса, третий выход - к входам чтения первого и второго блоков памяти и синхровходам первого и второго регистров числа, вход чтения третьего блока памяти подключен к синхровходу третьего регистра числа, к первым входам элементов И первой группы и к четвертому выходу блока синхронизации, пятьй выход которого подключен к стробирующему входу операционного блока, а шестой - к первым входам элементов И второй группы, вторые входы которых подключены к соответствующим разрядам выхода буферного регистра и первого информационного входа операцион- ного блока, второй информационный вход которого подключен к информационному входу буферного регистра и к выходу третьего регистра числа, информационные входы с первого по третий регистров числа подключены к информационным выходам с первого по третий блоков памяти соответственно, выходы элементов И второй группы под

ключены к первым входам соответствую- 40 группы первого информационного входа

щих рые дам

элементов ИЛИ первой группы, втовходы которых подключены к выхо- соответствующих элементов И первой группы, выходы элементов ИЛИ первой группы подключены к соответствую- щим разрядам входа логической схемы сравнения, выход которой подключен к информационному входу регистра кода сравнения, выход которого подключен к информационному входу регистра вьгоода, синхровход которого подключен к седьмому выходу блока синхронизации, восьмой и девятый выходы которо

операционного блока, выход элемента НЕ каждого операционного узла подключен к первым входам входных элементов И и ИЛИ того же операционного узла, вторые входы входных элементов И и ИЛИ i-ro операционного узла j-й группы подключены к i-му разряду j-й группы второго информационного входа операционного блока, выходы 50 входных элементов И и ИЛИ каждого операционного узла подключены к первым входам соответственно выходных элементов ИЛИ и И того же операционного узла, второй вход выходного элего подкГлючены к первым .входам соответственно элементов И третьей группы 55 мента ИЛИ каждого операционного узла и элементов ИЛИ второй группы, вторые подключен к выходу выходного элемен- входы которых подключены к соответ- та И того же операционного узла, вы- ствующим разрядам информационного вы- ход выходного элемента ИЛИ i-ro (i хода операционного блока, выходы эле- 1, N-1) операционного узла j-й групментов ИЛИ второй группы подключены к вторым входам соответствующих элементов И третьей группы, выходы которых подключены к синхровходу буферного регистра, тактовый вход блока синхронизации является та ктовым входом процессора, вькод регистра вьшода является выходом номера решения процессора, отличающийся тем, что, с целью сокращения аппаратных затрат за счет снижения емкости памяти, процессор содержит блок селекции и шифратор, причем вход шифратора подключен к выходу регистра кода срав

нения, разряды выхода шифратора подключены к соответствующим разрядам младшей группы адресного входа третьего блока памяти, разряды младшей группы адресного входа второго блока

пам яти подключены к соответствующим разрядам выхода регистра адреса, ин- формационньй вход блока селекции подключен к выходу первого регистра числа, управляющий вход блока селекции

подключен к выходу второго регистра числа, разряды выхода блока селекции подключены к вторым входам соответствующих элементов И первой группы. 2,Процессор по п.1, о т л и ч а

ю щ и и с я тем, что операционный блок содержит Р групп (где Р - число эталонных ситуаций) по N операционных узлов (где N - разрядность значения переменной), каждый из которых содержит элемент НЕ, входные элементы И и ИЛИ и выходные элементы И и- ИЛИ, причем вход элемента НЕ i-ro операционного узла j-й группы (i 1, N, j 1, Р) является i-M разрядом j-и

5

операционного блока, выход элемента НЕ каждого операционного узла подключен к первым входам входных элементов И и ИЛИ того же операционного узла, вторые входы входных элементов И и ИЛИ i-ro операционного узла j-й группы подключены к i-му разряду j-й группы второго информационного входа операционного блока, выходы 0 входных элементов И и ИЛИ каждого операционного узла подключены к первым входам соответственно выходных элементов ИЛИ и И того же операционного узла, второй вход выходного эле5 мента ИЛИ каждого операционного узла подключен к выходу выходного элемен- та И того же операционного узла, вы- ход выходного элемента ИЛИ i-ro (i 1, N-1) операционного узла j-й груп13

пы подключен к второму входу выходного элемента И (i + 1)-го операционного узла той же гр)уппы, выход выходного элемента ИЛИ N-ro операционного узла j-й группы является j-M разрядом информационного выхода операционного блока, вторые входы вы- ходньвс эле ментов И первых операционных узлов всех групп подключены к стробирующему входу операционного блока,

1

3. Процессор ПОП.1, отличающийся тем, что блок синхрони130570414

элементов И, второй вход одиннадцатого элемента И подключен к четвертому входу шестого элемента Ник входу седьмого элемента НЕ, выход которого 5 подключен к вторым входам четвертого и десятого элементов Инк первому входу двенадцатого элемента И, второй вход которого подключен к входу шестого элемента НЕ и к третьему вхо- 10 ду четвертого элемента И, четвертый вход которого подключен к входу пятого элемента НЕ, к второму входу восьмого элемента Ник первому входу тринадцатого элемента И, второй

зации содержит счетчик, двадцать один le

„„С, вход которого подключен к второму

элемент И, семь элементов НЕ и пять

входу девятого элемента И и к входу четвертого элемента НЕ, входы четвертого, пятого, шестого и седьмого элементов НЕ подключены соответственно к первому, второму, третьему и четвертому разрядам вьпсода счетчика, выход десятого элемента И подключен к первым входам элементов И с четырнадцатого по семнадцатый, выход одиннадцатого элемента И подключен к первому входу восемнадцатого элемента И, второй вход которого подключен к выходу седьмого элемента И и к первому входу девятнадцатого элемента И, второй вход которого подключен к выходу две- j надцатого элемента И, к первым входам двадцатого и двадцать первого элементов И и к второму входу семнадцатого элемента И, вторые входы четырнадцаэлементов ИЛИ, причем первый, второй и четвертый разряды информационного входа счетчика подключены к входу логического нуля блока, третий разряд информационного входа счетчика подключен к входу логической единицы блока, синхровход, вход начальной установки и тактовый вход счетчика подключены соответственно к выходам первого, второго и третьего элементов И, первые входы которых подключены к тактовому входу блока синхронизации, второй вход первого элемента И подключен к выходу четвертого элемента И, входу первого элемента НЕ и первому входу пятого элемента И второй вход которого подключен к выходу второго элемента НЕ, вход которого подключен к третьему входу первого элемента И и к выходу первого элемента ИЛИ, входь: которого являются соответствующими разрядами входа пуска блока синхронизации, выходы первого элемента НЕ и пятого элемента И подключены соответственно к первому и (второму входам второго элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, третий вход которого подключен к вы- ходу третьего элемента НЕ, вход которого подключен к второму входу второго элемента И и к выходу шестого элемента и, первый вход которого подключен к вькоду четвертого элемента НЕ, первым входам четвертого, седьмого и восьмого элементов И, второй вход шестого элемента И подключен к выходу пятого элемента НЕ, к первому входу девятого элемента И и к второму входу седьмого элемента И, третий вход шестого элемента И подключен к выходу шестого элемента НЕ и к первым входам десятого и одиннадцатого

0

5

0

входу девятого элемента И и к входу четвертого элемента НЕ, входы четвертого, пятого, шестого и седьмого элементов НЕ подключены соответственно к первому, второму, третьему и четвертому разрядам вьпсода счетчика, выход десятого элемента И подключен к первым входам элементов И с четырнадцатого по семнадцатый, выход одиннадцатого элемента И подключен к первому входу восемнадцатого элемента И, второй вход которого подключен к выходу седьмого элемента И и к первому входу девятнадцатого элемента И, второй вход которого подключен к выходу две- j надцатого элемента И, к первым входам двадцатого и двадцать первого элементов И и к второму входу семнадцатого элемента И, вторые входы четырнадца5 того и двадцать первого элементов И I

подключены к выходу восьмого элемента И, вторые входы пятнадцатого и двадцатого элементов И подключены к выходу девятого элемента И, второй вход шестнадцатого элемента И подключен к выходу тринадцатого элемента И, выходы четырнадцатого и двад- . цатого элементов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, выходы пятнадцатого и девятнадцатого элементов И подключены соответственно к первому и второму входам четвертого элемента ИЛИ, -выходы шестнадцатого и двадцать

0

5

0

5

первого элементов И подключены соответственно к первому и второму входам пятого элемента ИЛИ, выходы с первого по девятый блока синхронизации подключены соответственно к выходам девятнадцатого элемента И, пятнадцатого элемента И, четвертого элемента ИЛИ, третьего элемента ИЛИ., двадцать первого элемента И, семнад15130

цатого элемента И, восемнадцатого элемента И, пятого элемента ИЛИ и шестнадцатого элемента И,

А, Процессор по п.1, о т л и ч а- ю щ и и с я тем, что блок селекции содержит группы элементов ИЛИ, N де- мультитшексоров, информационные входы которых образуют информационный вход блока селекции, управляющие входы де

2f

4

16

мультиплексоров подключены к управляющему входу блока селекции, 1-й/вы- ход i-ro демультиплекСора (j 1,К; i 1,N) подключен к j-му входу элементов ИЛИ 1-й группы (где 1 i+j-2), разряды первого выхода первого де- мультиплексора, выходов элементов ИЛИ групп и К-го выхода N-ro демуль- типлексора о5разуют выход блока се- -лекции.

Фи9,1

Фи9.г

5 S fS

/

е

81

е

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Лингвистический процессор для обработки диагностической информации | 1989 |

|

SU1672417A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Управляющий процессор | 1984 |

|

SU1290341A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

. Изобретение относится к вычислительной техник-е и может быть использовано в многопарамётрических системах управления, для которых точная математическая модель функционирования объекта управления неизвестна. Цель изобретения - сокращение аппаратных затрат путем снижения требуемой емкости памяти. С этой целью логический процессор содержит блок селекции и шифратор, с помощью которых осуществляются выявление максимального значения степени принадлежности входных параметров эталонному множеству и в дальнейшем шифрование этого значения в код номера решения, являющийся результатом работы процессора. 3 з.п. ф-лы. 6 ил. 4 табл. с S ел с сд

п

8Z

82

82

VU

f

Фие.

85

ти

0010} .Гооп

тити

Фиг.5

Фи&.В

Редактор С.Пекарь

Составитель Н.Захаревич

Техред в.КадарКорректор С.Черни

Заказ 1454/48 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35/ Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР №843592, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Балашов Е.П | |||

| и др | |||

| Многофункциональные регулярные вычислительные структуры | |||

| - М.: Сов.радио, 1978 | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-08-08—Подача