I

Изобретение относится к вычислительной технике, электронике и может быть использовано при создании больших интегральных схем (БИС) и в качестве выходного усилителя, предназначенного для работы .на внешнюю емкостную нагруасу и для непосредственного объединения по ИЛИ с выходными каскадами других БИС. В частности, элемент может быть исполь зован в статических оперативных запоминающих устройствах для вывода информации.

Известны элементы с тремя состояниями, построенные как на МДП, так и на биполярных транзисторах l. Их существенными признаками являются наличие на выходе мощного двухтактного нелинейного ключа-усилителя, построен-ного или на транзисторах одного или аополняюших типов прЪводимости, и схем управления работой ключа-усилителя.

В качестве входных сигналов для раб1оты таких элементов используются управляющий сигнал (и/илм его инверсия).

а также информационный сигнал (и-или инверсия информационного сигнала). Принцип работы элемента заключается в том, что информационный сигнал, равныйлогической единице или нулю появляется на выходе элемента только при наличии управляющего сигнала или инверсии управляющего сигнала. В противном случае оба транзистора выходного ключа-усилителя закрыты и на выходе элемента устанавливается третье состояние, при котором внутренняя часть БИС отключается от нагрузки.

Недостатком известных элементов является различие во времени формирования сигналов на затворах транзисторов выходного ключа-усилителя из-за асиммет- рии схем управления, что уменьшает быстродействие устройства.

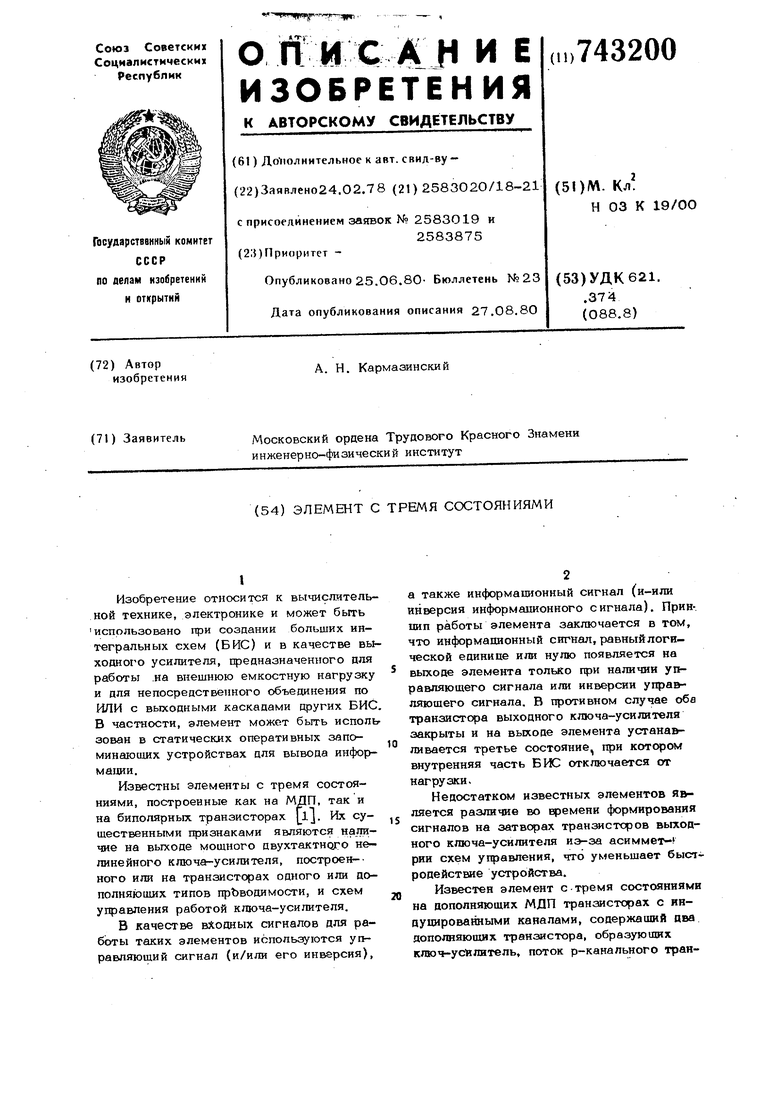

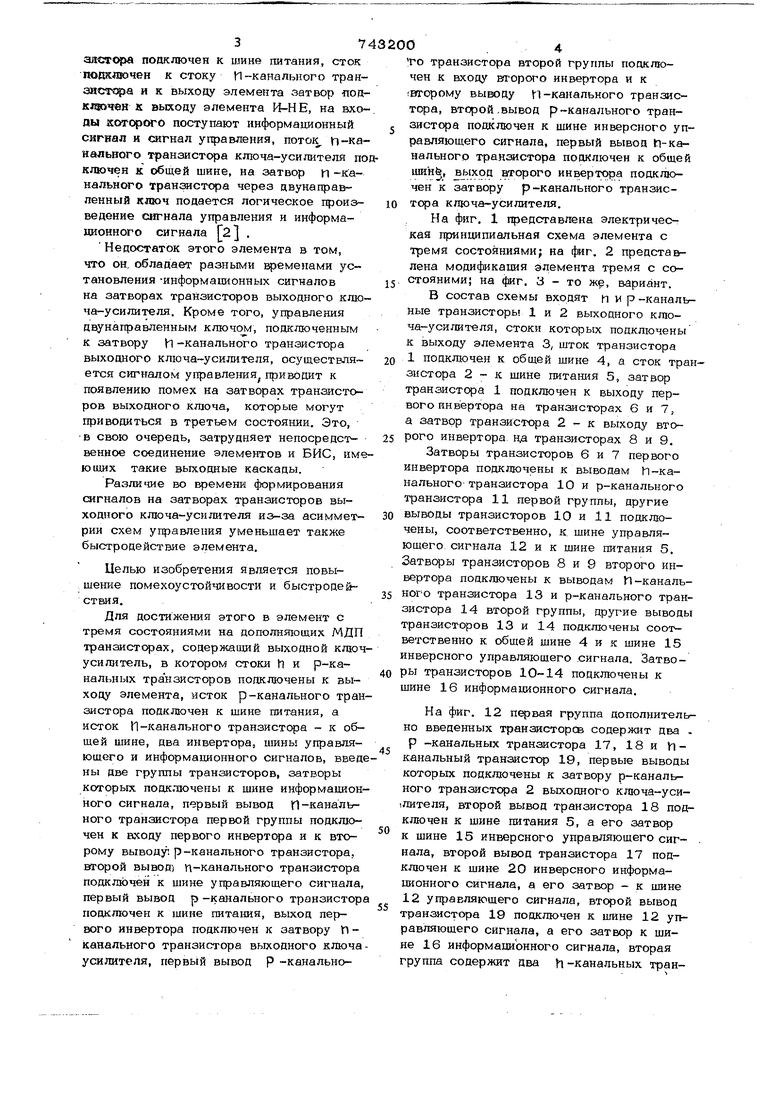

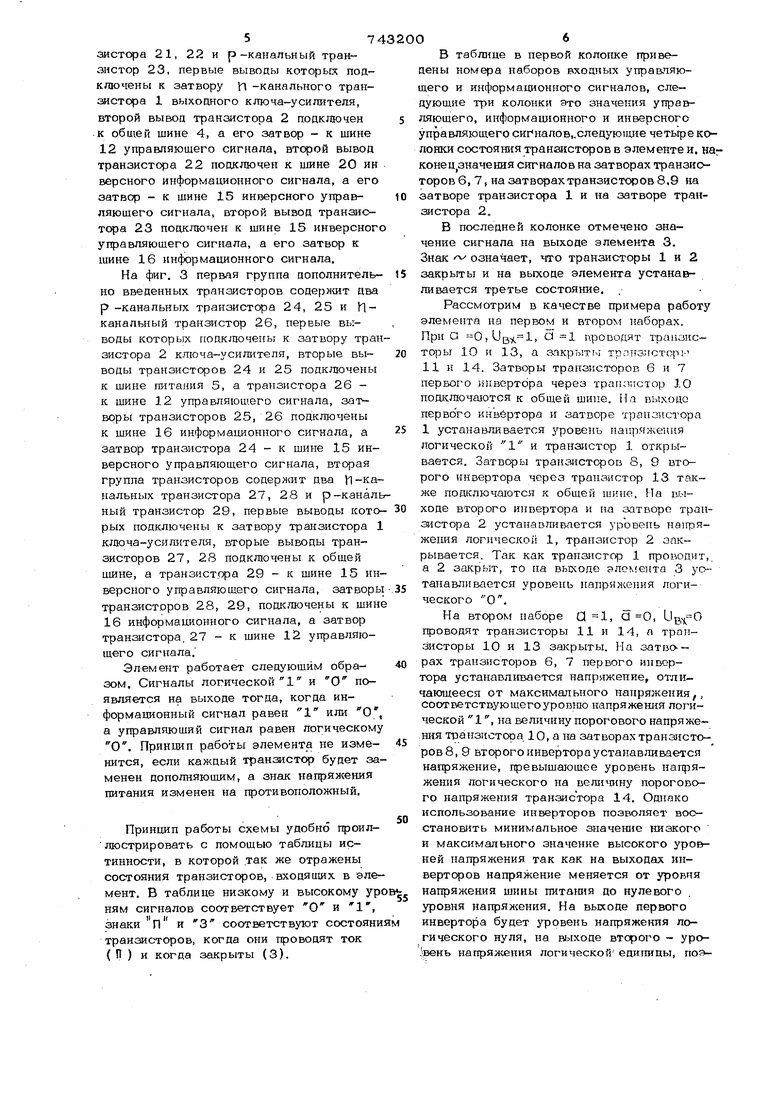

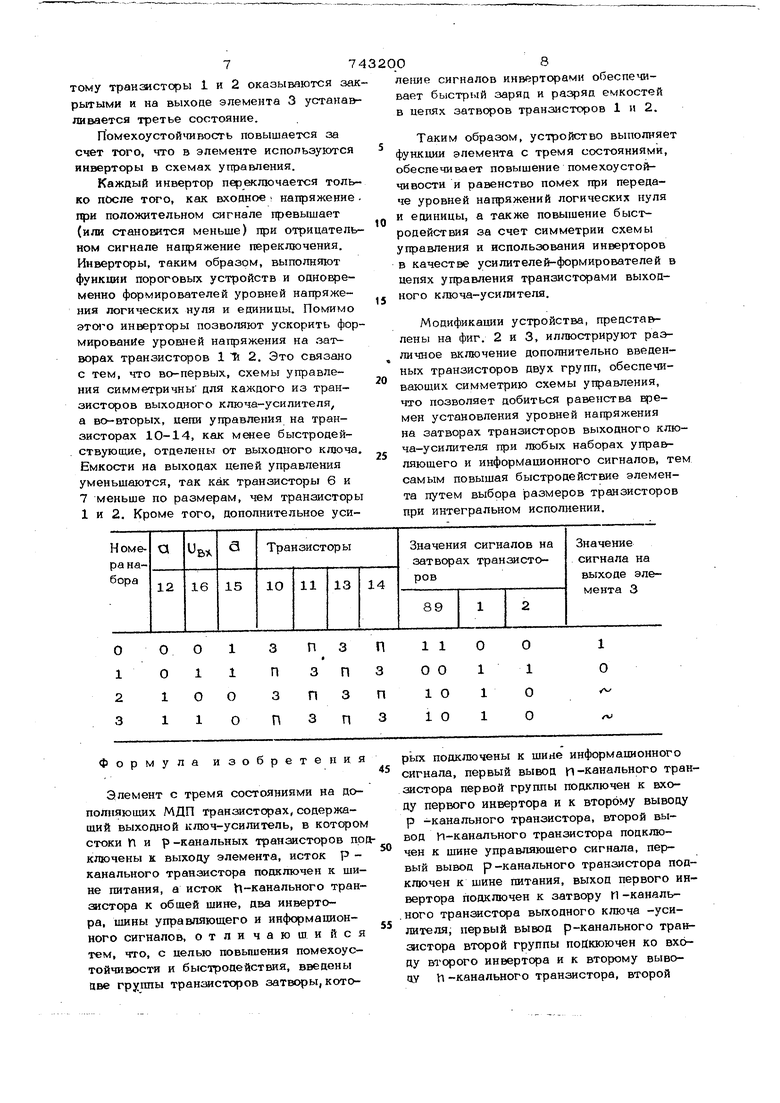

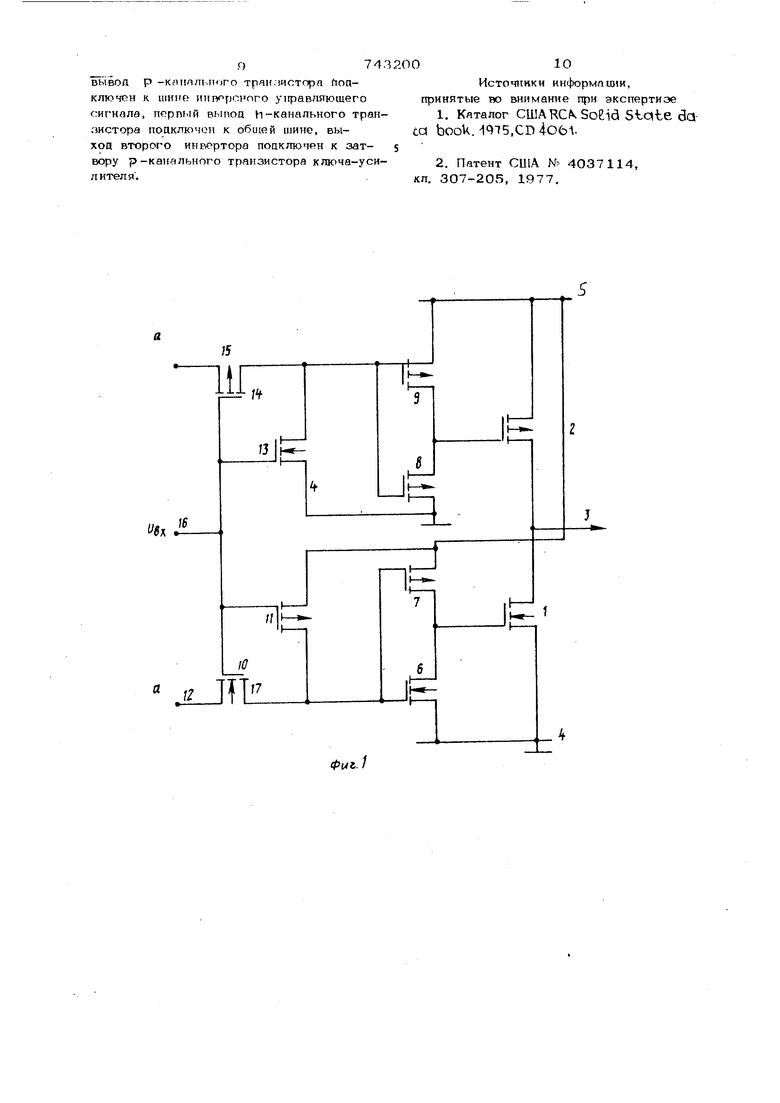

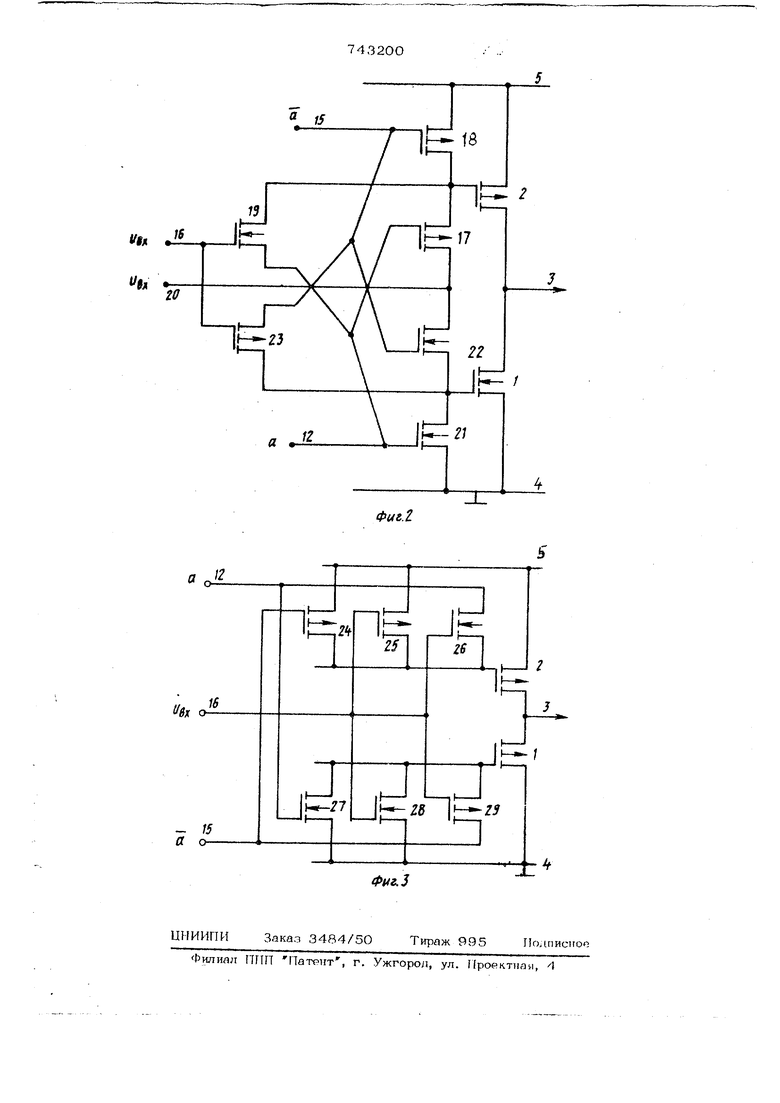

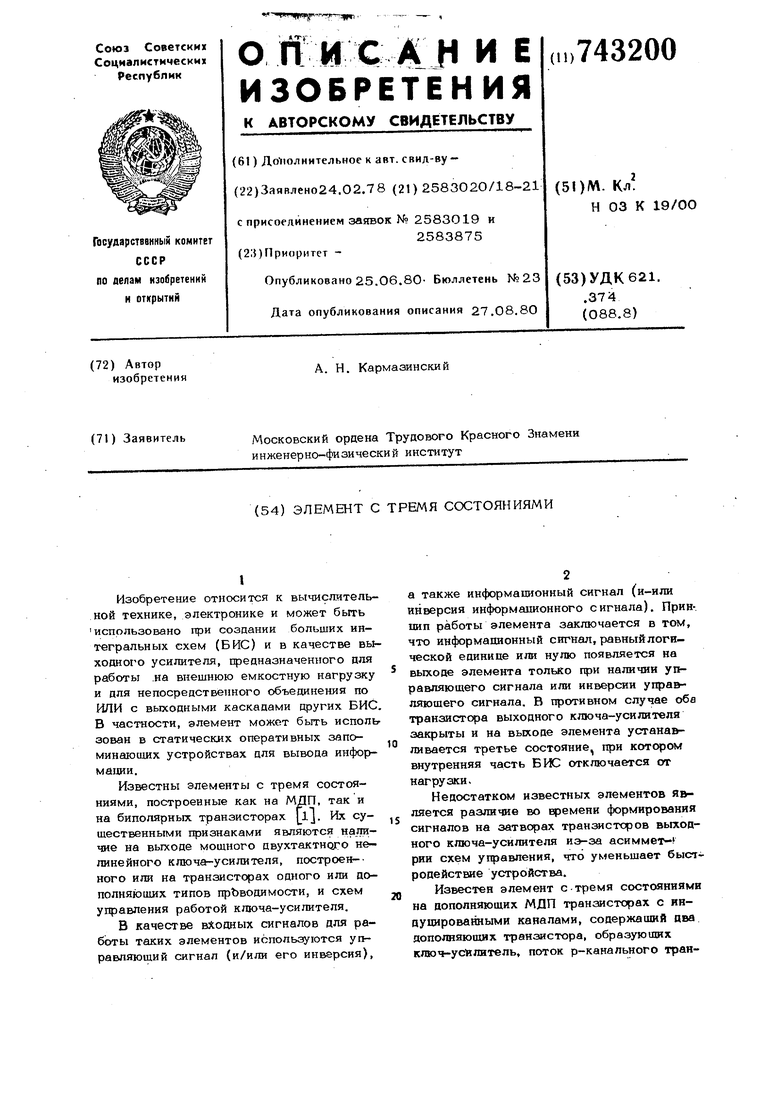

Известен элемент с тремя состояниями на дополняющих МДП транзисторах с инауцированными каналами, содержащий два дополняющих транзистора, образующих ключ-усйлнтель, поток р-канального транаястсч а подключен к шине питания, сток попкшочен к стоку И-канального транэист« а и к выходу элемента затвор «од к выходу элемента И-НЕ, на БХОды которого поступают информационный сигнал и сигнал управления, поток нального чранзистора ключа-усилителя по ключен к общей шине, на затвор п -канального транзистора через двунащзавленный ключ подается логическое произведение сигнала управления и информационного сигнала 2 , Недостаток этого элемента в том, что он. обладает разными временами установления -информационных сигналов на затворах транзисторов выходного клю ча-усилителя. Кроме того, управления двунаправленным ключом, подключенным к затвору h -канального транзистора выходного ключа-усилителя, осуществляется сигналом управления приводит к появлению помех на затворах транзисторов выходного ключа, которые могут приводиться в третьем состоянии. Это, в свою очередь, затрудняет непосредственное соединение элементов и БИС, им ющих такие выходные каскады. Различие во времени формирования сигналов на затворах транзисторов выходного ключа-усилителя из-за асимметрии схем управления уменьшает также быстродействие элемента. Целью изобретения является повышение помехоустойчивости и быстродействия. Для достижения этого в элемент с тремя состояниями на дополняющих МДП транзисторах, содержащий выходной ключ усилитель, в котором стоки И и р-канальных транзисторов подключены к выходу элемента, исток р-канального тран зистора подключен к шине питания, а исток П-канального транзистора - к общей шине, два инвертора, шины управляющего и информационного сигналов, введ ны две группы транзисторов, затворы которых подключены к шине информацион ного сигнала, первый вывод П-канальгного транзистора первой группы подключен к юсоду первого инвертора и к второму выводу р-канального транзистора, второй ВЫВОД) п-канального транзистора подключен к шине управляющего сигнала первый вывод р-канального транзистора подключен к шине питания, выход первого инвертора подключен к затвору И канального транзистора выходного ключаусилителя, первый вывод Р -канальноТо транзистора второй группы подключен к входу второго инвертора и к (Второму выводу П-канального транзистора, второй,вывод р-канального транзистора подключен к шине инверсного управляющего сигнала, первый вывод И-канального транзистора подключен к общей шин, Eibixpa второго инвертора подключен к затвору р-канального транзистсра ключа-усилителя. На фиг. 1 представлена электрическая принципиальная схема элемента с тремя состояниями; на фиг, 2 представлена модификация элемента тремя с состояними; на фиг. 3 - то жр, вариант. В состав схемы входят мир -канальные транзисторы 1 и 2 выходного ключа-усилителя, стоки которых подключены к выходу элемента 3, шток транзистора 1 подключен к общей шине 4, а сток транзистора 2 - к шине питания 5, затвор транзистора 1 подключен к выходу первого инвертора на транзисторах 6 и 7, а затвор транзистора 2 - к выходу второго инвертора нд транзисторах 8 и 9. Затворы транзисторов 6 и 7 первого инвертора подключены к выводам П-канального транзистора 10 и р-канального транзистора 11 первой группы, другие выводы транзисторов 10 и 11 подключены, соответственно, к шине управляющего сигнала 12 и к шине питания 5. Затворы транзисторов 8 и 9 второго инвертора подключены к выводам П-канального транзистора 13 и р-канального транзистора 14 второй группы, другие выводы транзисторов 13 и 14 подключены соответственно к общей шине 4 и к шине 15 инверсного управляющего .сигнала. Затворы транзисторов 10-14 подключены к шине 16 информационного сигнала. На фиг. 12 пфвая группа дополнителЕ но введенных транзисторсв содержит два . р -канальных транзистора 17, 18 и hканальный транзистор 19, первые выводы которых подключены к затвору р-канального транзистора 2 выходного ключа-уси1лителя, второй вывод транзистора 18 подключен к шине питания 5, а его затвор к шине 15 инверсного управляющего сигнала, второй вывод транзистора 17 подключен к шине 20 инверсного информационного сигнала, а его затвор - к шине 12 управляющего сигнала, второй вывод транзистора 19 подключен к шине 12 управляющего сигнала, а его затвор к шине 16 информационного сигнала, вторая группа содержит два h-канальных транзистсра 21, 22 и р-канальный транзистор 23, первые выводы которых подключены к затвору П -канального транаистора 1 выходного ключа-усилителя, второй вывод транзистора 2 подключен к общей шиие 4, а его затвор - к шине 12 управляющего сигнала, второй вывод транзистора 22 подключен к шине 20 ив вареного информационного сигнала, а его затвор - к шине 15 инверсного управляющего сигнала, второй вывод транзистора 23 подключен к шине 15 инверсног управляющего сигнала, а его затвор к шине 16 информационного сигнала. На фиг. 3 первая группа дополнитель- но введенных транзисторов содержит два р -канальных транзистфа 24, 25 и Нканальный транзистор 26, первые выводы которых гюдкгаочены к затвору тран зистора 2 ключа-усия 1теля, вторые выводы транзисторов 24 и 25 подключены к шине питания 5, а транзистора 26 к шине 12 управляющего сигнала, зат воры транзисторов 25, 26 подключены к шине 16 информационного сигнала, а затвор транзистора 24 - к шине 15 инверсного управляюш.его сигнала, вторая группа транзисторов соцер я1т два }1-канальных транзистора 27, 28 и р-канал ный транзистор 29, первые выводы кото рых подключены к затвору транзистора 1 ключа-усилителя, вторые выводы транзисторов 27, 28 подклзочены к общей шине, а транзистора 29 - к шине 15 ин версного управляющего сигнала, затворы транзисторов 28, 29, пош лючены к шин 16 информационного сигнала, а затвор транзистора. 27 - к шине 12 управляющего сигнала. Элемент работает следующим образом. Сигналы логической и О появляется на выходе тогда, когда информационный сигнал равен 1 или О а управляющий сигнал равен логическом О. Принцип работы элемента не изменится, если каждый траншстор будет за менен ДОПОЛНЯЮЩИМ, а знак напряже1шя питания изменен на противоположный, . Принцип работы схемы удобно проиллюстрировать с помощью таблицы истинности, в которой так же отражены состояния транзисторов, входяцщх в эле мент. В таблице низкому и высокому ур ням сигналов соответствует О и i знаки п и 3 соответствуют состояни транзисторов, когда они проводят ток ( П ) и когда закрыты (3). В таблице в первой приведены номера наборов входных управляющего и информационного сигналов, следующие три колонки это значения управляющего, информационного и инверсного управляюа1его сиг налов,.следующие четыре колонки состояния транзисторов в элементе и. наг конец,значения сигналов на затворах транзиоторов 6, 7, на затворах транзисторов 8,9 на затворе транзистора 1 и на затворе транзистора 2, В последней колонке отмечено значение сигнала на выходе элемента 3. Знак - означает, что транзисторы 1 и 2 закрыты и на выходе элемента устанавливается третье состояние. Рассмотрим в качестве примера работу элемента на первом и втором наборах. При а 0, , проводят транзисторы 10 и 13, а закрыть; троттзистсрр 11 и 14. Затворы транзисторов 6 и 7 первого инвертора через траппястор 10 подключаются к общей шипе. На выходе первого инвертора и затворе транзистора 1 устанавливается уровень напряжения логической 1 и транзистор 1 открглвается. Затворы транзисторов 8, 9 второго инвертора через транзистор 13 также подключаются к общей шиие. fla m.ходе второго инвертора и на затворе трапгистора 2 устанавливается уровень на1гряжекия логической 1, транзистор 2 закрывается. Так как транзистор 1 проводит,, а 2 закрыт, то па выходе элоыеита 3 устанавливается уровень напряжения логического О. На втсром наборе Q 1, , Ug, проводят транзисторы 11 и 14, п тропзисторы 10 и 13 закрыты. На затварах транзисторов 6, 7 первого инвертора устанавл$гвается напряжение, отличающееся от максимального напряжения,, соотвегствзюшегоуровню напряжешм логической 1, на величину порогового напряжения транзистора 10, а 1ш затворах транзисторов 8, 9 второго инвертора устанав;швается напряжение, превышающее уровень напряжения логического на велцгшну порогового напряжения транэ1стора 14. Однако использование инверторов позволяет восстановить минимальное значение низкого и максимального значение высокого уровней напряжения так как на выходах инверторов напряжение меняется от уровня напряжения шины питагшя до нулевого уровня напряжения. На выходе первого инвертора будет уровень напряжения логического нуля, на В1лходе второго - уровень напрял-сения логической едигшцы, поэому транзисторы 1 и 2 оказываются закытыми и на выходе элемента 3 устанавливается третье состояние.

Помехоустойчивость повышается за счет того, что в элементе используются инверторы в схемах управления.

Каждый инвертор переключается только после того, как входное напряжение при положительном сигнале превышает (или становится меньше) при отрицательном сигнале напряжение переключения. Инверторы, таким образом, выполняют функции пороговых устройств и одновременно формирователей уровней напряжения логических нуля и единицы. Помимо это1о инверторы позволяют ускорить формирование уровней напряжения на яатворах транзисторов 1 и 2. Это связано с тем, что во-первых, схемы управления симметричны для каждого из транзисторов выходного ключа-усилителя, а во-вторых, цепи управления на транзисторах 10-14, как MQiee быстродействуюище, отделены от выходного ключа, Емкости на выходах цепей управления уменьшаются, так как транзисторы 6 и 7 меньше по размерам, чем транзисторы 1 и 2. Кроме того, дополнительное усиление сигналов инверторами обеспечивает быстрый заряд и разряд емкостей в цепях затворов транзисторов 1 и 2.

Таким образом, устройство выполняет функции элемента с тремя состояниями, обеспечивает повышение помехоустойчивости и равенство помех при передаче уровней напряжений логических нуля и единицы, а также повышение быстродействия за счет симметрии схемы управления и использования инверторов в качестве усилителей-формирователей в цепях управления транзисторами выходного ключа-усилителя.

Модификации устройства, предстанулены на фиг. 2 и 3, иллюстрируют различное включение дополнительно введенных транзисторов двух групп, обеспечивающих симметрию схемы управления, что позволяет добиться равенства времен установления уровней напряжения на затворах транзисторов выходного ключа-усилителя при любых наборах управляющего и информационного сигналов, те самым повышая быстродействие элемента путем выбора размеров транзисторов при интегральном исполнении.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| Многоканальный коммутатор | 1984 |

|

SU1220123A1 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

Формула изобретения Элемент с тремя состояниями на дополняющих МДП транзистфах, содержащий выходной ключ-усилитель, в котором стоки Пир -канальных транзисторов по ключены к выходу элемента, исток р канального транзистора подключен к шине питания, а исток Ji-канального транзистора к общей шине, два инвертора, шины управляющего и информационного сигналов, отличающийся тем, что, с целью повьшзения помехоустойчивости и быстродействия, введены цве группы трансшсторов затворы, которых подключены к шине информационного сигнала, первый вывод п-канального транзистора первой группы подключен к входу первого инвертора и к второму выводу р -канального транзистора, второй вывод и-канального транзистора подключен к шине управляющего сигнала, первый вывод р-канального транзистора подключен к шине питания, выход первого инвертора подключен к затвору И -канального транзистора выходного ключа -усилителя, первый вывод р-канального тра зистора второй группы пойкюючен ко входу второго инвертора и к второму выводу VI -канального транзистора, второй

вывод р -к;и пльмого тряизисторп fionключен к шине нипоронпго управляющего сигнала, первый выпоа Ц-канального транзистора поцключон к обшей тине, выход второго инвертора поцклкзчен к затвору р-канального транзистора ключа-усилителя.

ИГ

п

/5

У5х .

17

f/

Источники информпш и, принятые во внимание при экснертиэе

О //

Vh

%

Авторы

Даты

1980-06-25—Публикация

1978-02-24—Подача