стрк первого транзистора обратной связи подключен к первому выходу усилителя и к затвору второго транзистора обратной связи, сток второго транзистора обратной связи подключен к второму выходу усилителя и к затвору первого транзистора обратной связи, истоки первого и второго разрядных И -канальных транзисторов подключены к стоку ключевого транзистора, исток первого инверторного р-канального транзистора соединен с затвором певого нагрузочного II-канального транзистора, исток второго инверторного р-канального транзистора соединен с затвором второго h -канального нагрузочного транзистора, истоки первого и второго переключающих р-канальных транзисторов подключены к шине питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

УСИЛИТЕЛЬ СЧИТЬЮАНИЯ НА ДОПОЛНЯЮЩИХ МДП-ТРАНЗИСТОРАХ, содержащий первый и второй переключающие р-канальные транзисторы, соединенные по триггерной схеме, первый и второй нагрузочные и ключевой п -канальные транзисторы, первый и второй инверторные р-канальные транзисторы и третий и четвертый инверторные П-канальные транзисторы, причем сток первого переключающего транзистора подключен к стоку первого нагрузочного и затворам первого и третьего инверторных транзисторов, сток второго переключающего транзистора соединен с затворами второго и четвертого инверторных транзисторов и стоком второго нагрузочного транзистора, истоки нагрузочных транзисторов подключет ны к стоку ключевого транзистора, исток которого соединен с шиной нулевого потенциала, а затвор является первым управляющим входом усилителя, затворы первого и второго нагрузочных транзисторов являются соответственно первым и вторым входами усилителя, стоки первого и третьего инверторных транзисторов объединены и являются первьлм выходом усилителя, а стоки второго и четвертого инверторных транзисторов объединены и являются вторым выходом усилителя, третий и четвертый переключающие р-канальные транзисторы, соединенные по триг- . герной схеме, первый и второй управляющие р-канальные и первый и второй разрядные П-канальные транзисторы, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с затвором второго нагрузочного транзистора, стоки четвертого переключающего, и вторых управляющего и разрядного транзисторов соединены с затвором первого нагрузочного транзистора, истоки -третьего и четвертого переключающих и первого и второго управляющих транзисторов подключены к шине питания, затворы «о первого и второго управляющих тран(Л зисторов являются вторым управляющим входом усилителя, истоки третьего и четвертого инверторных транзисторов соединены с истоком ключевого транзистора, затворы первого и второго разрядных транзисторов подключены соответственно к первому и второму выходам усилителя, исток и сток третьего управляющего транзистора соединены соответственно с шиной питания и затвором первого инверторного транзистора, исток и сток четвертого управляющего транзистора подключены соответственно к шине питания и затвору второго инверторного транзистора, затворы третьего и четвертого управляющих транзисторов соединены с затвором ключевого транзистора, отличающийся тем, что, с целью повышения надежности усилителя за счет устойчивости к изменению пороговых напряжений р-канальных транзисторов при сохранении высокого быстродействия, он содержит первый и второй .П -канальные транзисторы обратной связи, истоки которых соединены с шиной нулевого потенциала.

Изобретение относится к запоминающим устройствам и может быть использовано при построении микромощных интегральных запоминающих устройств на дополняющих МДП-транзисторах.

Известен усилитель считывания для запоминающего устройства на дополняющих МДП-транзисторах, содержащий первый и второй р-канальные транзисторы, соединенные триггерной связью, истоки которых подключены к шине питания и истокам р-канальных транзисторов первого и второго инверторов, причем исток первого р-канального транзистора соединен с входом первого инвертора и стоком первого нагрузочного ц-канального транзистора, сток второго р-канального транзистора соединен с входом второго инвертора и стоком второго нагрузочного П-канального транзистора, выходы первого и второго инверторов соединены соЬтветственно с первым и вторым выходами усилителя, затворы первого и второго нагрузочных п-канальных транзисторов соединены соответственно с первой и второй разрядными шинами, истоки - со стоком ключевого п-канального транзистора, затвор которого соединен- с шиной управления, исток - с общей шиной, истоки П-канальных транзисторов первого и второго инвертора соединены со стоком ключевого tl -канального транзистора, к шине управления подключен затвор симметрирующего транзистора, исток которого связан с входом первого инвертора, а сток - с входом второго инвертора н.

Недостатками этого,усилителя являются низкие чувствительность и быстродействие.

Наиболее близкл-,.л техническим решением к изобретению является усилитель считывания для запоминающего устройства на дополняющих МДП-транзисторах, содержащий первый и второй переключающие р-канальные транзисторы, соединенные 5 по триггерной схеме, первый и второй нагрузочные ft-канальные транзисторы, ключевой П-канальный транзистор, первый и второй р-канальные инверторные транзисторы, тре-:

10 тий и четвертый 11-канальные инверторные транзисторы, причем сток первого переключающеготранзистора подключен к стоку первого нагрузочного и затворам первого и третье15 го инвертонных транзисторов, сток второго переключающего транзистора соединен с затворами второго и четвертого инверторных транзисторов . и стоком второго нагрузочного транQ зистора, истоки нагрузочных транзисторов подключены к стоку ключевого транзистора, исток которого соединен с шиной нулевого потенциала, а затвор является первым упC равляющим входом усилителя, истоки первого и второго инверторных транзисторов подключены к шине питания, затворы первого и второго нагрузочных транзисторов являются соответственно первым и вторым входами уси лителя, стоки первого и третьего

, инверторных транзисторов объединены , и являются первым выходом усилителя, а стоки второго и четвертого инверторных транзисторов объединены и 5 Являются вторым выходом усилителя, третий и четвертый переключающие р-канальные транзисторы,.соединенные по триггерной схеме, первый, второй р-канальные управляющие 0 транзисторы и первый и второй и-канальные .разрядные транзисторй, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с истоком переключающего транзистора и затвором второго нагрузочного трайГ зистора, стоки четвертого переключающего и вторых управляющего и разрядного транзисторов соединены с истоком второго переключающего транзистора и затвором первого нагрузочного транзистора, истоки третьего и четвертого переключающих и первог и второго управляющих транзисторов подключены к шине питания, затворы первого и второго управляющих транзисторов соединены с затвором третьего разрядного транзистора и являются вторым управляющим входом усилителя, истоки первого и второго разрядных транзисторов подключены к стоку третьего разрядного транзистора, исток которого и истоки третьего и четвертого инверторных транзисторов соединенна с истоком ключевого транзистора и подключены к шине нулевого потенциала, затворы первого и второго разрядных транзисторов подключены соответственно к первому и второму выходам усилителя, исток и сток третьего управляющего транзистора соединены соответственно с шиной питания и затвором первого инверторного транзистора, исток и сток Четвертого управляющего транзистора подключены соответственно к шине питания и затвору второго инверторного транзистора, затворы третьего и четвертого уп равляющих транзисторов соединены с затвором ключевого транзистора 2

Известный усилитель имеет высокое быстродействие, однако отличается относительно узкой зоной работоспособности по отношению к разбросу пороговых напряжений р-канальных транзисторов (до 50%). При значительном увеличении пороговых напряжений р-канальных транзисторов в процессе переключения схемы происходит снижение потенциалов до напряжения переключения инверторов которые открывают первый и второй разрядные транзисторы. При этом оба выхода усилителя обнуляются, причем это состояние схемы сохраняется, что эквивалентно потере работоспособности запоминающего устройства.

Поэтому известный усилитель не может быть использован в случае предъявления повышенных требований к разбросу пороговых напряжений г)-канальных транзисторов.

Цель изобретения - повышение надежности усилителя за счет устойчивости к изменению пороговых р- канальных транзисторов при сохранении высокого быстродействия.

Поставленная цель достигается тем, что усилитель считывания для запоминающего устройства на дополняющих МДП-транзисторах, содержащий первый и второй переключакяцие р-канальные транзисторы, соединенные по триггерной схеме, первый и

торой нагрузочные и ключевой П-каальные транзисторы, первый и втоой инверторные р-канальные транзисоры и третий и четвертый инверторые И-канальные транзисторы, при ем сток первого переключающего ранзистора подключен к стоку перого нагрузочного и затвором перого и третьего инверторных транзисоров, сток второго переключающего ранзистора соединен с затворами второго и четвертого инверторных транзисторов и стоком второго нагрузочного транзистора, истоки нагрузочных транзисторов подключены к стоку ключевогр транзистора, исток которого соедйнен с шиной нулевого потенциала, а затвор является перым управляющим входом усилителя, затворы первого и второго нагрузочных транзисторов являются соответственно первым и вторым входами усилителя, стоки первого и третьего инверторных транзисторов объединены и являются первым выходом усилителя, а стоки второго и четвертого инверторных транзисторов объединены и являются вторым выходом усилителя, третий и четвертый переключающие р-канальные транзисторы, соединенные по триггерной схеме, первый и второй управляющие р-канальные и первый и второй разрядные П-канальные транзисторы, причем стоки третьего переключающего и первых управляющего и разрядного транзисторов соединены с затвором второго нагрузочного транзистора, стоки четвертого переключающего и вторых управляющего и разрядного транзисторов соединены с затвором первого нагрузочного транзистора, истоки третьего и четвертого переключающих и первого и второго управляющих транзисторов подключены к шине питания, затворы первого и второго управляющих транзисторов являются вторым управляющим входом усилителя, истоки третьего и четвертого инверторных транзисторов соединены с истоком ключевого транзистора, затворы первого и второго разрядных транзисторов подключены соответственно к первому и второму выходам усилителя, исток и сток третьего управляющего транзистора

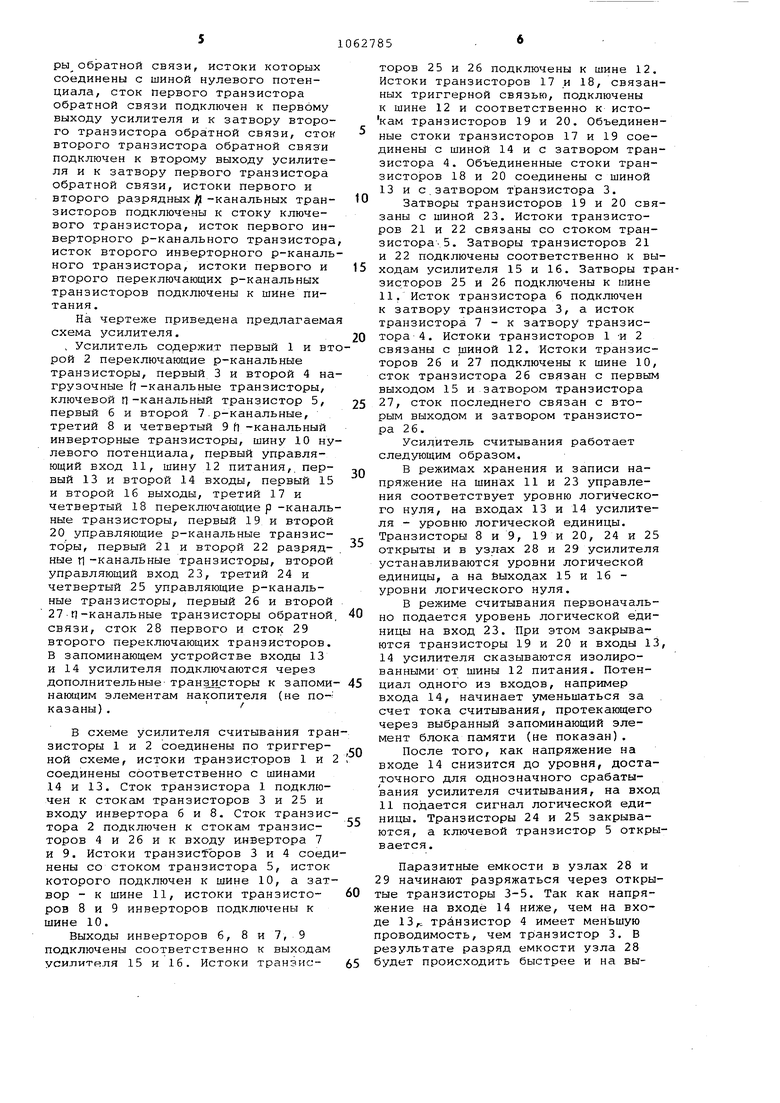

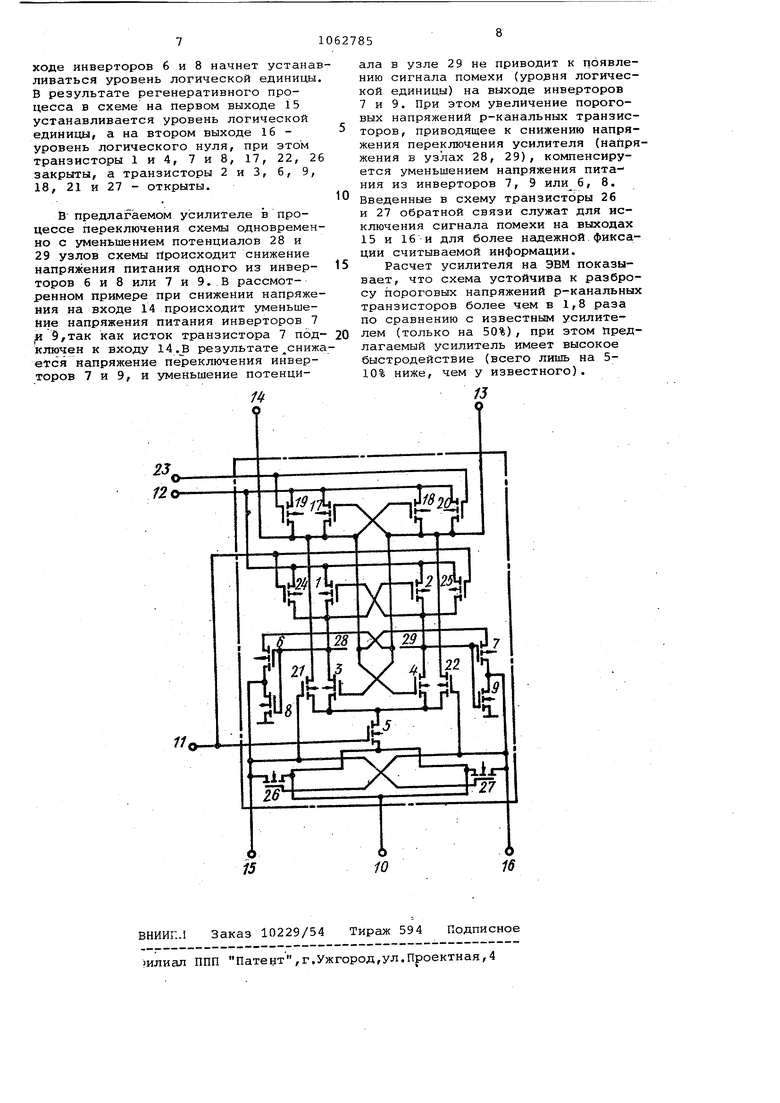

соединены соответственно с шиной питания и затвором первого инверторного транзистора,исток и сток четверто го управляющего транзистора подключены соответственно к шине питания и затвору второго инверторного транзистора, затворы третьего и четвертого управляющих транзисторов соединены с затвором ключевого транзистора, дополнительно содержит первый и второй И-канальные транзисторы обратной связи, истоки которых соединены с шиной нулевого потенциала, сток Первого транзистора обратной связи подключен к первому выходу усилителя и к затвору второго транзистора обратной связи, сток второго транзистора обратной связи подключен к второму выходу усилителя и к затвору первого транзистора обратной связи, истоки первого и второго разрядных J-канальных транзисторов подключены к стоку ключевого транзистора, исток первого инверторного р-канального транзистора исток второго инверторного р-каналь ного транзистора, истоки первого и второго переключающих р-канальных транзисторов подключены к шине питания. На чертеже приведена предлагаема схема усилителя. , Усилитель содержит первый 1 и вт рой 2 переключающие р-канальные транзисторы, первый 3 и второй 4 на грузочные fj -канальные транзисторы, ключевой п-канальный транзистор 5, первый б и второй 7.р-канальные, третий 8 и четвертый 9 fi -канальный инверторные транзисторы, шину 10 ну левого потенциала, первый управляющий вход 11, шину 12 питания,, первый 13 и второй 14 входы, первый 15 и второй 16 выходы, третий 17 и четвертый 18 переключающиер -каналь ные транзисторы, первый 19 и второй 20 управляющие р-канальные транзисторы, первый 21 и второй 22 разрядные п-канальные транзисторы, второй управляющий вход 23, третий 24 и четвертый 25 управляющие р-канальные транзисторы, первый 26 и второй 27и-канальные транзисторы обратной связи, сток 28 первого и сток 29 второго переключающих транзисторов. В запоминающем устройстве входы 13 и 14 усилителя подключаются через дополнительные- транзисторы к запоми нающим элементам накопителя (не показаны), В схеме усилителя считывания тра зисторы 1 и 2 соединены по триггерной схеме, истоки транзисторов 1 и соединены соответственно с шинами 14 и 13. Сток транзистора 1 подключен к стокам транзисторов 3 и 25 и входу инвертора 6 и 8. Сток транзис тора 2 подключен к стокам транзисторов 4 и 26 и к входу инвертора 7 и 9. Истоки транзисторов 3 и 4 соед нены со стоком транзистора 5, исток которого подключен к шине 10, а зат вор - к шине 11, истоки транзисторов 8 и 9 инверторов подключены к шине 10. Выходы инверторов 6, 8 и 7,9 подключены соответственно к выходам усилителя 15 и 16. Истоки транзисторов 25 и 26 подключены к шине 12. Истоки транзисторов 17 и 18, связанных триггерной связью, подключены к щине 12 и соответственно к истокам транзисторов 19 и 20. Объединенные стоки транзисторов 17 и 19 соединены с шиной 14 и с затвором транзистора 4. Объединенные стоки транзисторов 18 и 20 соединены с шиной 13и с,затвором транзистора 3. Затворы транзисторов 19 и 20 связаны с шиной 23. Истоки транзисторов 21 и 22 связаны со стоком транзистора 5. Затворы транзисторов 21 и 22 подключены соответственно к выходам усилителя 15 и 16. Затворы транзисторов 25 и 26 подключены к шине 11. Исток транзистора 6 подключен к затвору транзистора 3, а исток транзистора 7 - к затвору транзистора 4 . Истоки транзисторов 1 -и 2 связаны с шиной 12. Истоки транзисторов 26 и 27 подключены к шине 10, сток транзистора 26 связан с первым выходом 15 и затвором транзистора 27, сток последнего связан с вторым выходом и затвором транзистора 26. Усилитель считывания работает следующим образом. В режимах хранения и записи напряжение на шинах 11 и 23 управления соответствует уровню логического нуля, на входах 13 и 14 усилителя - уровню логической единицы. Транзисторы 8 и 9, 19 и 20, 24 и 25 открыты и в узлах 28 и 29 усилителя устанавливаются уровни логической единицы, а на быходах 15 и 16 уровни логического нуля. В режиме считывания первоначально подается уровень логической единицы на вход 23. При этом закрываются транзисторы 19 и 20 и входы 13, 14усилителя сказываются изолированными от шины 12 питания. Потенциал одного из входов, например входа 14, начинает уменьшаться за счет тока считывания, протекающего через выбранный запоминающий элемент блока памяти (не показан). После того, как напряжение на входе 14 снизится до уровня, достаточного для однозначного срабатывания усилителя считывания, на вход 11 подается сигнал логической единицы. Транзисторы 24 и 25 закрываются, а ключевой транзистор 5 открывается. Паразитные емкости в узлах 28 и 9 начинают разряжаться через открыые транзисторы 3-5. Так как напряение на входе 14 ниже, чем на вхое 13,, транзистор 4 имеет меньшую роводимость, чем транзистор 3. В езультате разряд емкости узла 28 удет происходить быстрее и на выходе инверторов 6 и 8 начнет устанавливаться уровень логической единицы. В результате регенеративного процесса в схеме на первом выходе 15 устанавливается уровень логической единицы, а на втором выходе 16 уровень логического нуля, при этом транзисторы 1 и 4, 7 и 8, 17, 22, 26 закрыты, а транзисторы 2 и 3, 6, 9, 18, 21 и 27 - открыты.

.

В предлагаемом усилителе в процессе переключения схемы одновременно с уменьшением потенциалов 28 и 29 узлов схемы Происходит снижение напряжения питания одного из инверторов бив или 7 и 9. в рассмотренном примере при снижении напряжения на входе 14 происходит уменьшение напряжения питания инверторов 7 jH 9,так как исток транзистора 7 подключей к входу 14.В результате снижается напряжение пеЪеключения инверторов 7 и 9, и уменьшение потенциала в узле 29 не приводит к появлению сигнала помехи (уровня логической единицы) на выходе инверторов 7 и 9. При этом увеличение пороговых напряжений р-канальных транзисторов, приводящее к снижению напряжения переключения усилителя (напряжения в узлах 28, 29), компенсируется уменьшением напряжения питания из инверторов 7, 9 или б, В. Введенные в схему транзисторы 26 и 27 обратной связи служат для исключения сигнала помехи на выходах 15 и 16 и для более надежной.фиксации считываемой информации.

Расчет усилителя на ЭВМ показывает, что схема устойчива к разбросу пороговых напряжений р-канальных транзисторов более чем в 1,8 раза по сравнению с известным усилителем (только на 50%), при этом Предлагаемый усилитель имеет высокое быстродействие (всего лишь на 510% ниже, чем у известного).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ ПРОЦЕССА СУШКИ ЗЕРНА В ШАХТНОЙ ЗЕРНОСУШИЛКЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2018076C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-05—Подача