Изобретение относится к измерительной технике и может быть использовано в системах регистрации однократных сигналов

Целью изобретения является повышение точности представления формы измеряемых сигналов.

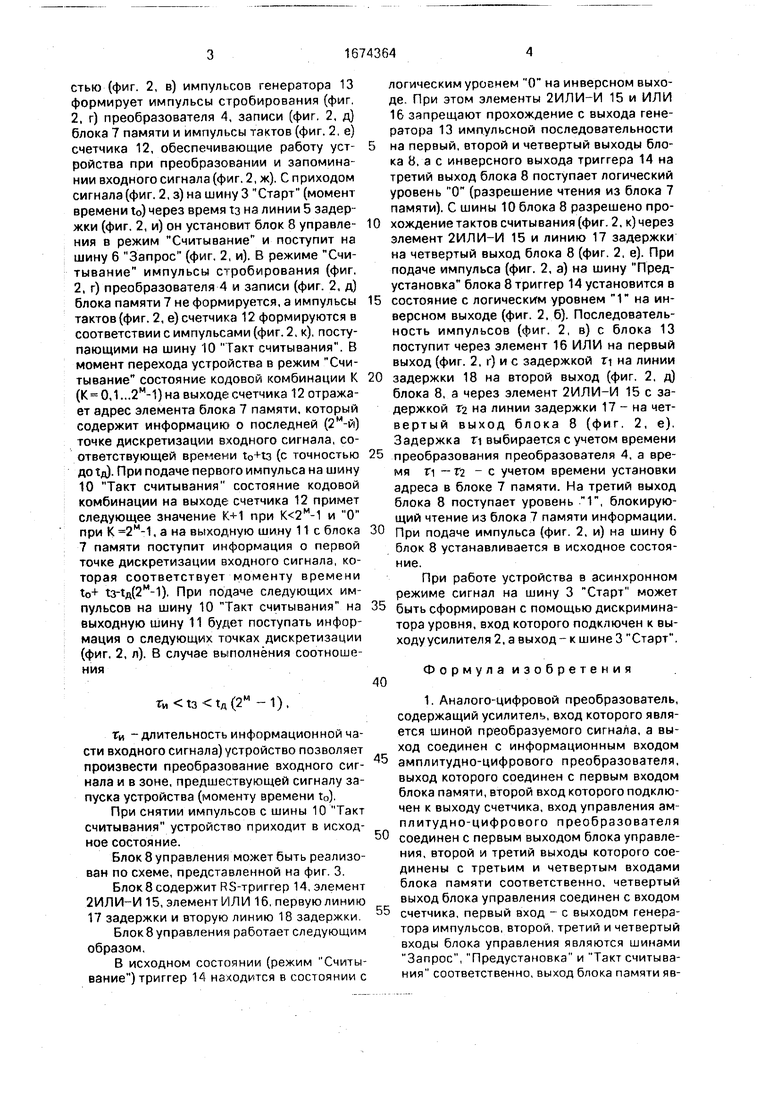

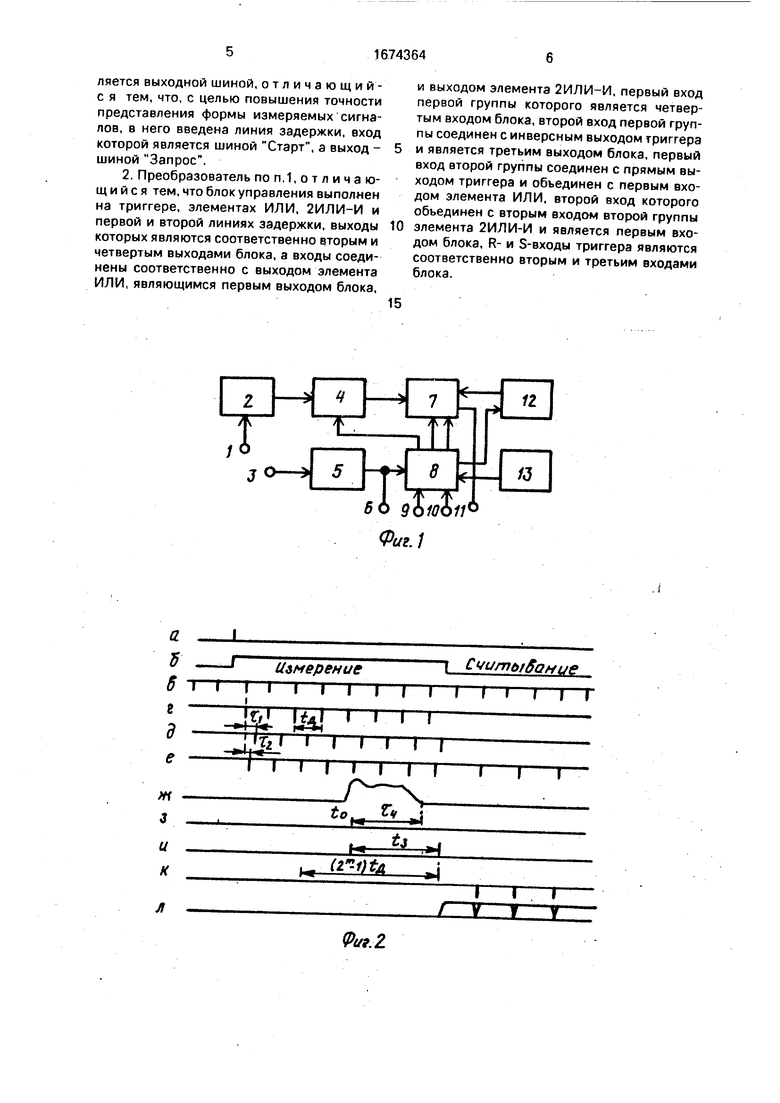

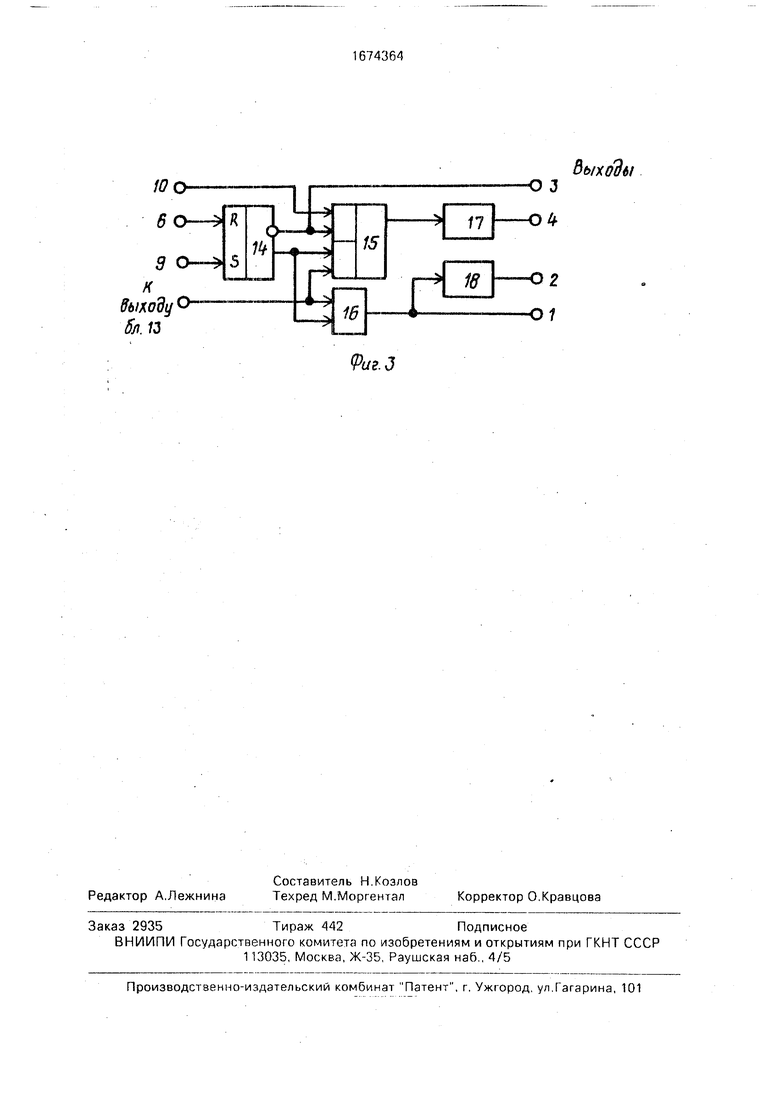

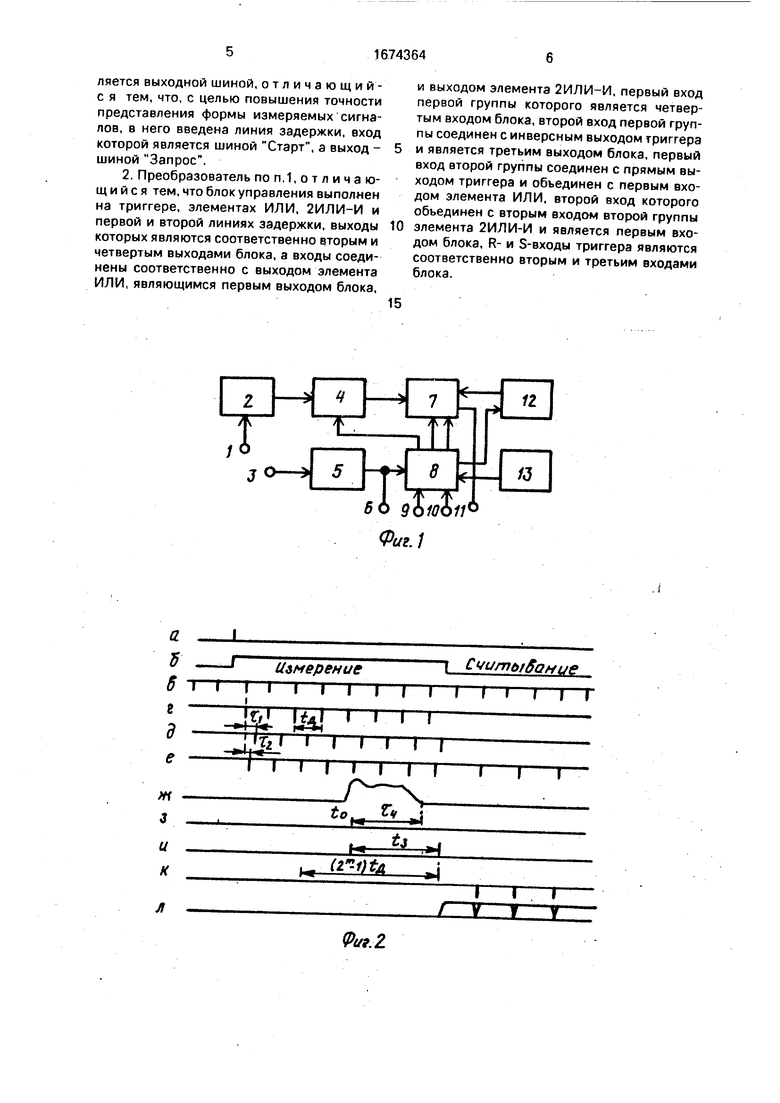

На фиг. 1 изображена структурная схема аналого-цифрового преобразователя; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - схема блока управления.

Аналого-цифровой преобразователь содержит шину 1 преобразуемого сигнала, усилитель 2, шину 3 Старт, амплитудно- цифровой преобразователь 4, линию 5 задержки, шину 6 Запрос, блок 7 памяти, блок 8 управления, шину 9 Предустановка, шину 10, Такт считывания, выходную шину 11, счетчик 12 и генератор 13.

При поступлении сигнала на шину 3 Старт (момент времени to - фиг. 2 и 3) через время задержки ta (фиг. 2, и) устройство устанавливается в режим Считывание. В результате из блока 7 памяти считывается информация о последних 2м (м - разрядность адресных шин блока памяти 7) преоб- разованиях амплитудно-цифрового преобразователя 4 или об амплитуде входного сигнала в моменты времени Гь+1з-(2м-1)тд; to+ tjj, где шаг т.д - дискретизации входного сигнала.

В исходном состоянии устройство находится в режиме Считывание, последовательность импульсов на шину 10 Такт считывания не подается, генератор 13 формирует последовательность импульсов (фиг. 2, в), блок 8 управления блокирует подачу импульсных сигналов на входы стробирова- ния преобразователя 4 и записи блока 7 памяти.

В режим Измерение (фиг. 2, б) устройство переводится подачей импульса (фиг. 2. а) на шину 9 Предустановка. Блок 8 управления в соответствии с последовательно VI

СО

о &

стью (фиг. 2, в) импульсов генератора 13 формирует импульсы стробирования (фиг. 2, г) преобразователя 4, записи (фиг. 2, д) блока 7 памяти и импульсы тактов (фиг. 2, е) счетчика 12, обеспечивающие работу устройства при преобразовании и запоминании входного сигнала (фиг. 2, ж). С приходом сигнала (фиг. 2, з) на шину 3 Старт (момент времени to) через время гз на линии 5 задержки (фиг. 2, и) он установит блок 8 управления в режим Считывание и поступит на шину 6 Запрос (фиг. 2, и). В режиме Считывание импульсы стробирования (фиг. 2, г) преобразователя 4 и записи (фиг. 2, д) блока памяти 7 не формируется, а импульсы тактов (фиг. 2, е) счетчика 12 формируются в соответствии с импульсами (фиг. 2, к), поступающими на шину 10 Такт считывания. В момент перехода устройства в режим Считывание состояние кодовой комбинации К (К 0,1.,.2м-1)на выходе счетчика отражает адрес элемента блока 7 памяти, который содержит информацию о последней (2м-й) точке дискретизации входного сигнала, соответствующей времени т.0+Хз (с точностью до т,д). При подаче первого импульса на шину 10 Такт считывания состояние кодовой комбинации на выходе счетчика 12 примет следующее значение К+1 при и О при К 2м-1, а на выходную шину 11с блока 7 памяти поступит информация о первой точке дискретизации входного сигнала, которая соответствует моменту времени Ь+ 1з-1д(2м-1). При подаче следующих импульсов на шину 10 Такт считывания на выходную шину 11 будет поступать информация о следующих точках дискретизации (фиг. 2, л). В случае выполнения соотношения

ти ,д(2м - 1),

Ти -длительность информационной части входного сигнала) устройство позволяет произвести преобразование входного сигнала и в зоне, предшествующей сигналу запуска устройства (моменту времени т0).

При снятии импульсов с шины 10 Такт считывания устройство приходит в исходное состояние.

Блок 8 управления может быть реализован по схеме, представленной на фиг. 3.

Блок8 содержит RS-триггер 14. элемент 2ИЛИ-И 15, элемент ИЛИ 16, первую линию 17 задержки и вторую линию 18 задержки.

Блок 8 управления работает следующим образом.

В исходном состоянии (режим Считывание) триггер 14 находится в состоянии с

логическим уроснем О на инверсном выходе. При этом элементы 2ИЛИ-И 15 и ИЛИ 16 запрещают прохождение с выхода генератора 13 импульсной последовательности

на первый, второй и четвертый выходы блока 8, а с инверсного выхода триггера 14 на третий выход блока 8 поступает логический уровень О (разрешение чтения из блока 7 памяти). С шины 10 блока 8 разрешено прохождение тактов считывания (фиг. 2, к) через элемент 2ИЛИ-И 15 и линию 17 задержки на четвертый выход блока 8 (фиг. 2, е). При подаче импульса (фиг. 2, а) на шину Предустановка блока 8 триггер 14 установится в

состояние с логическим уровнем 1 на инверсном выходе (фиг. 2, б). Последовательность импульсов (фиг. 2, в) с блока 13 поступит через элемент 16 ИЛИ на первый выход (фиг. 2, г) и с задержкой ri на линии

задержки 18 на второй выход (фиг. 2, д) блока 8, а через элемент 2ИЛИ-И 15 с задержкой Т2 на линии задержки 17 - на четвертый выход блока 8 (фиг. 2, е). Задержка т выбирается с учетом времени

преобразования преобразователя 4, а время п - т/2 - с учетом времени установки адреса в блоке 7 памяти. На третий выход блока 8 поступает уровень Г, блокирующий чтение из блока 7 памяти информации.

При подаче импульса (фиг. 2, и) на шину 6 блок 8 устанавливается в исходное состояние.

При работе устройства в асинхронном режиме сигнал на шину 3 Старт может

быть сформирован с помощью дискриминатора уровня, вход которого подключен к выходу усилителя 2, а выход- к шине 3 Старт.

40

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий усилитель, вход которого является шиной преобразуемого сигнала, а выход соединен с информационным входом

амплитудно-цифрового преобразователя, выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу счетчика, вход управления амплитуд но-цифрового преобразователя

соединен с первым выходом блока управления, второй и третий выходы которого соединены с третьим и четвертым входами блока памяти соответственно, четвертый выход блока управления соединен с входом

счетчика, первый вход - с выходом генератора импульсов, второй,третий и четвертый входы блока управления являются шинами Запрос, Предустановка и Такт считывания соответственно, выход блока памяти является выходной шиной, отличающий- с я тем, что, с целью повышения точности представления формы измеряемых сигналов, в него введена линия задержки, вход которой является шиной Старт, а выход - шиной Запрос.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок управления выполнен на триггере, элементах ИЛИ, 2ИЛИ-И и первой и второй линиях задержки, выходы которых являются соответственно вторым и четвертым выходами блока, а входы соединены соответственно с выходом элемента ИЛИ, являющимся первым выходом блока,

и выходом элемента 2ИЛИ-И, первый вход первой группы которого является четвертым входом блока, второй вход первой группы соединен с инверсным выходом триггера и является третьим выходом блока, первый вход второй группы соединен с прямым выходом триггера и обьединен с первым входом элемента ИЛИ, второй вход которого обьединен с вторым входом второй группы элемента 2ИЛИ-И и является первым входом блока, R- и S-входы триггера являются соответственно вторым и третьим входами блока.

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1377894A1 |

| Устройство для зондовой диагностики плазмы | 1987 |

|

SU1525587A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для измерения перемещений | 1986 |

|

SU1357695A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

| Многоканальный преобразователь кода во временной интервал | 1985 |

|

SU1298922A1 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

Изобретение относится к измерительной технике и может быть использовано в системах регистрации однократных сигналов. Целью изобретения является повышение точности представления формы измеряемых сигналов. Цель изобретения достигается тем, что в устройство, содержащее амплитудно-цифровой преобразователь, вход которого через усилители соединен с шиной преобразуемого сигнала, блок памяти, блок управления, счетчик и генератор, введены линия задержки, вход которой является шиной "Старт", а выход шиной "Запрос". 1 з.п. ф-лы, 3 ил.

56 9бмб11°

Фиг.1

I i I

/УГУ

9U9.Z

дь/ходы

Риг.З

| Гитис Э.И Преобразователи информации для электронных вычислительных уст ройств, М | |||

| Энергия, 1975 | |||

| Корнерез для пней | 1921 |

|

SU448A1 |

| Боримский В В | |||

| и др | |||

| Быстродействующий аналого-цифровой преобразователь для физических исследований | |||

| - Приборы и техника эксперимента, 1987 г, № 6, с.71-72. | |||

Авторы

Даты

1991-08-30—Публикация

1988-12-19—Подача