О

VJ о

о

GJ

Изобретение относится к измерительной технике и может быть использовано в системах автоматического контроля.

Целью изобретения является повышение функциональной надежности путем обеспечения непрерывного контроля.

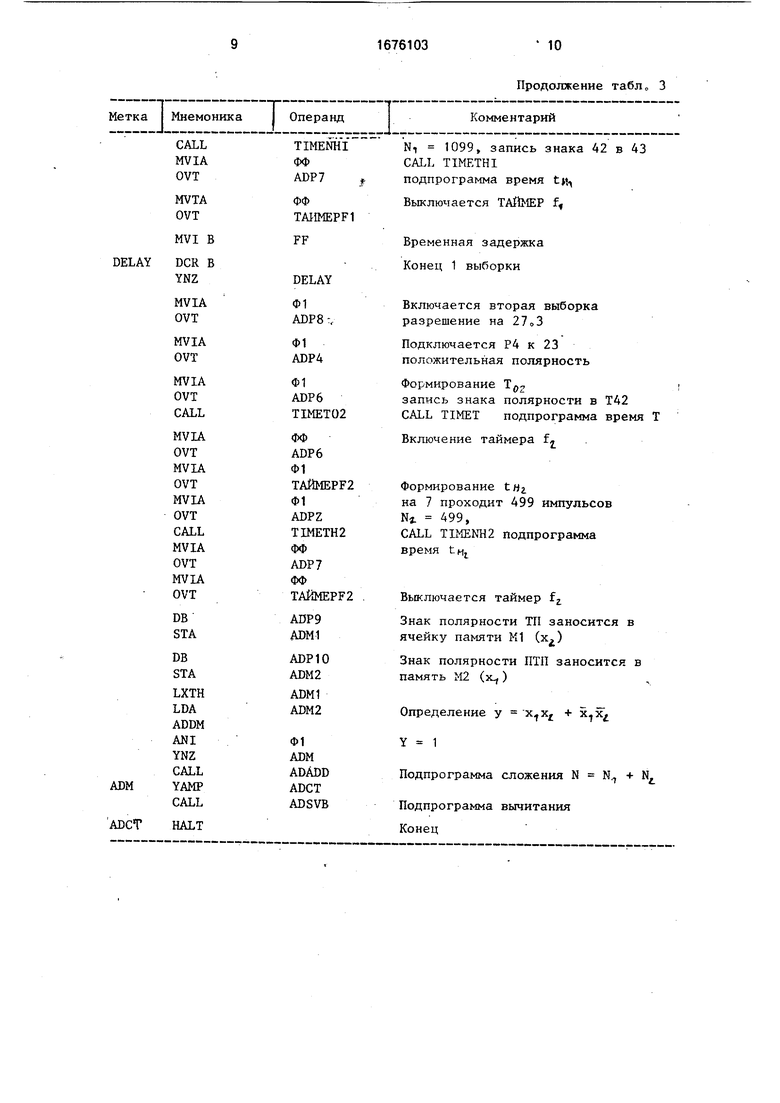

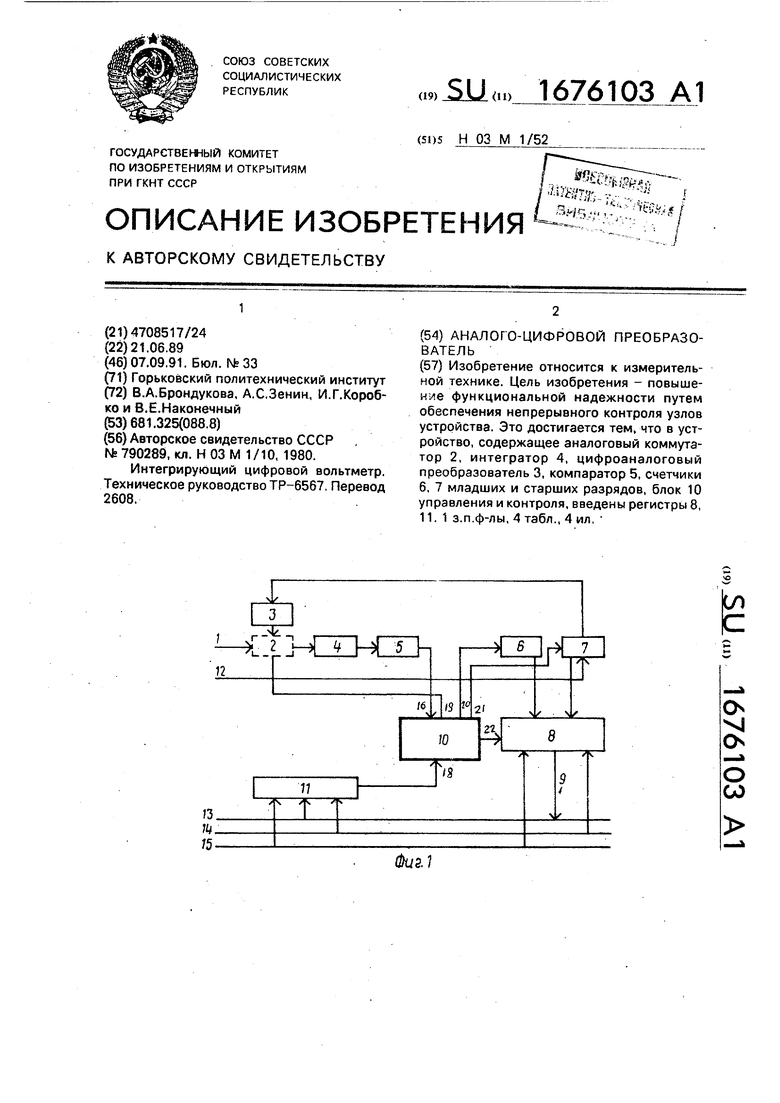

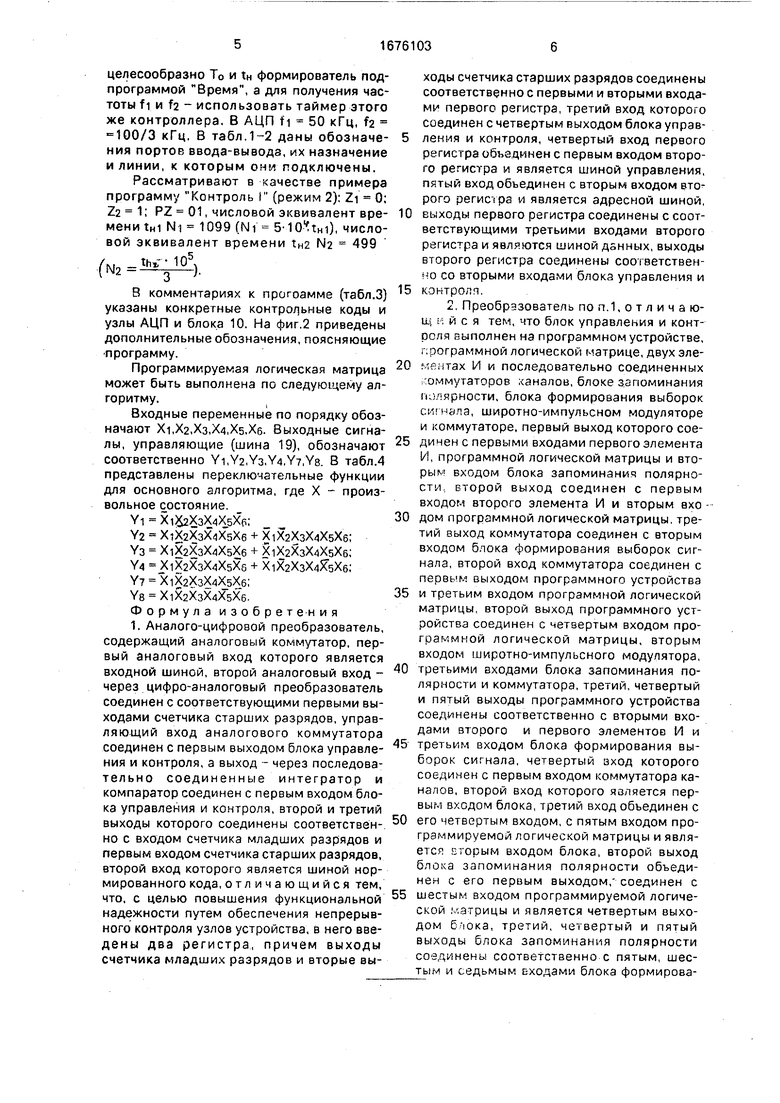

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З - фун- кциональная схема аналогового коммутатора; на фиг.4 - временная диаграмма работы АЦП.

Устройство (фиг.1) содержит аналоговый вход 1, аналоговый коммутатор 2, циф- роаналоговый преобразователь 3, построенный по принципу широтно-им- пульсной модуляции, интегратор 4, компаратор 5, счетчик 6 младших разрядов 6, счетчик 7 старших разрядов, регистр 8, программное устройство 9, блок 10 управления и контроля, регистр 11, шину 12 нормированного кода NH, ширину 13 данных, шину 14 адреса, шину 15 управления.

Блок управления и контроля (фиг.2) содержит входы 16, программное устройство 17, вход 18, выходы 19-22. коммутатор 23 каналов, блок 24 запоминания полярности, блок 25 формирования выборок сигнала, широтно-импульсный модулятор 26, коммутатор 27, элементы И 28 и 29, программную логическую матрицу 30, выходы 31, 32 и 33 коммутатора, программное устройство 1-7 имеет выход 34 сигналов нормированной длительности tH, выход 35 сигнала образцовой частоты fi, выход 36 сигнала образцовой частоты f2, выход 37 образцового времени То, выход 38 сигнала разделения выборок tp, вход 18 содержит линию 39 логического сигнала коммутации Ф, линию 40 режимов, коммутатор 23 содержит элемент И 41, блок 24 содержит триггеры 42 и 43, элементы И-НЕ 44 и 45, инвертор 46, блок 25 содержит элементы И-НЕ 47, широтно- импульсный модулятор 26 содержит инверторы 48, триггеры 49, коммутатор 27 содержит элементы И-НЕ 50. Аналоговый коммутатор (фиг.З) содержит источники 51-54 напряжений, ключи 55 и 56, резисторы 57.

На фиг.4 обозначено: 58 - напряжение на выходе интегратора; 61 - логические уровни на выходе компаратора 5; 59 - образцовое время первой Т01, и второй Т02 выборок на выходе блока V7; 60 - напряжение сигнала разделения выборок. tp; 62 - импульсы формирования сигналов с нормированной длительностью tH; 63 - напряжение сигналов рабочей txi и нормированный tHi длительности первой выборки; 64 - напряжение сигналов рабочей txi и нормированной tH2 длительности второй выборки.

Блок 10 обеспечивает работу АЦП в шести основных режимах: Режим I, Режим

II, Режим III,Контроль , Контроль II,Контроль III1 .

В режиме I работает только первая выборка и АЦП измеряет напряжение как вольтметр, преобразуя входное напряже0 ние в цифровой код, фиксированный в счетчике старших разрядов.

В режиме II работают обе выборки, обеспечивая дифференциальные измерения входного напряжения,

5 В режиме III измеряется отклонение входной величины от номинального напряжения, заданного кодом Мн. При Мн О АЦП работает как милливольтметр, фиксируя выходной код в счетчике младших раз0 рядов.

Изменение режимов производится с по- мощью двух разрядов регистра 11, которые обозначены Zi и 7.2. Режимам I, II, III соответствуют следующие коды Zi и 22. Режим

5 Г (00); Режим И (01); Режим lit (10).

В режиме Контроль I производится проверка блоков 6-11. В этом режиме блок 10 формирует определенные логические уровни и импульсы нормированной дли0 тельности, которые преобразуются в определенные кодовые комбинации, В режиме Контроль I можно проверять коды NI; N2; N N1 + N2; N N1 - N2, что позволяет проводить выборочную проверку опреде5 ленных блоков.

В режиме Контроль II производится проверка блоков 2,4 и 5 и аддитивных ошибок при работе АЦП в режимах 1,11,111,

В режиме Контроль III, кроме блоков

0 2,4 и 5, производится проверка блока 3, а также мультипликативных ошибок при работе АЦП в режимах 1,11,111.

Режимы контроля задаются с помощью разрядов регистра 11.

5 Данное устройство обеспечивает непрерывный контроль как всего АЦП, так и его основных узлов, что повышает достоверность контроля и надежность систем, в которых он применяется.

0 Функции программного устройства могут выполнять самые различные аппаратные средства, например, контроллер К-20 (МС 2702), однокристальная микро-ЭВМ {КР 1816 BE 48). Так как контроллер систе5 мы имеет связь с АЦП по шинами 13,14 и 15, то функции программного устройства 17 могут выполняться тем же контроллером через соответствующие порты ввода- вывода. Ввиду того, что тактовая частота контроллера стабилизирована кварцем,

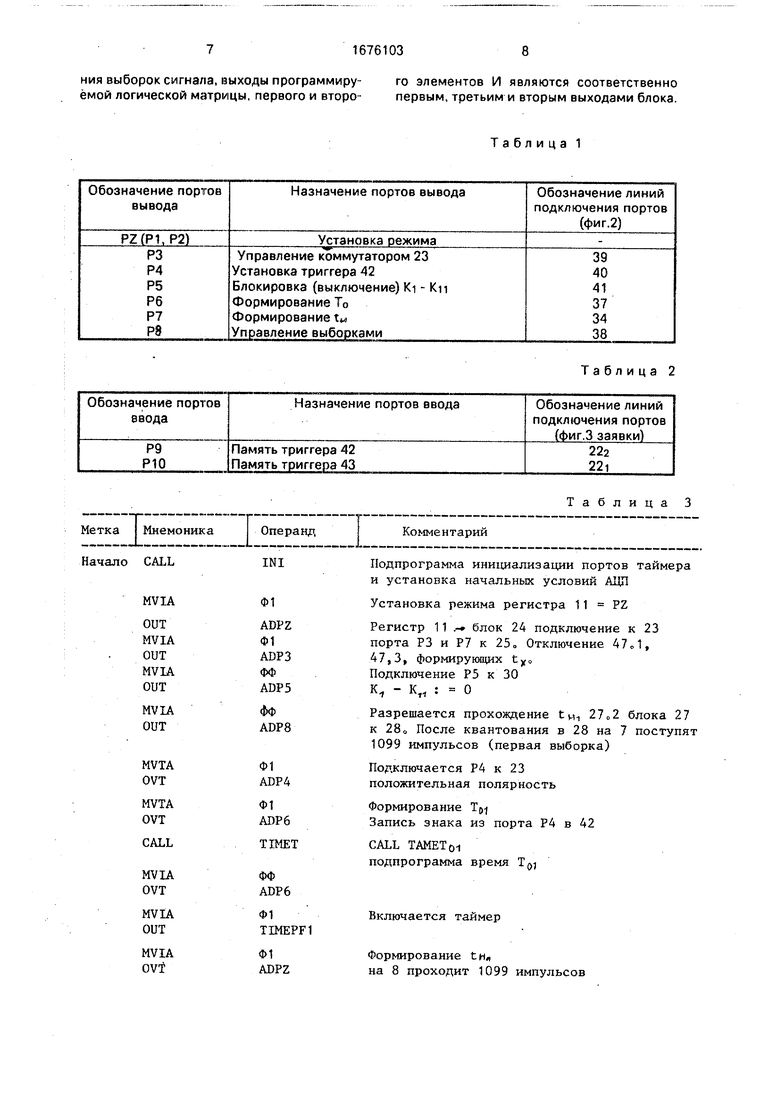

целесообразно Т0 и tH формирователь подпрограммой Время, а для получения частоты fi и f2 - использовать таймер этого же контроллера. В АЦП ti 50 кГц, fa 100/3 кГц. В табл.1-2 даны обозначения портов ввода-вывода, их назначение и линии, к которым они подключены.

Рассматривают в качестве примера программу Контроль (режим 2): Zi 0; 7.1 1; PZ 01, числовой эквивалент времени tHi N1 1099 (N1 ), числовой эквивалент времени tH2 N2 499

(N2

В комментариях к прогоамме (табл.3) указаны конкретные контрольные коды и узлы АЦП и блока 10. На фиг.2 приведены дополнительные обозначения, поясняющие -программу.

Программируемая логическая матрица может быть выполнена по следующему алгоритму.

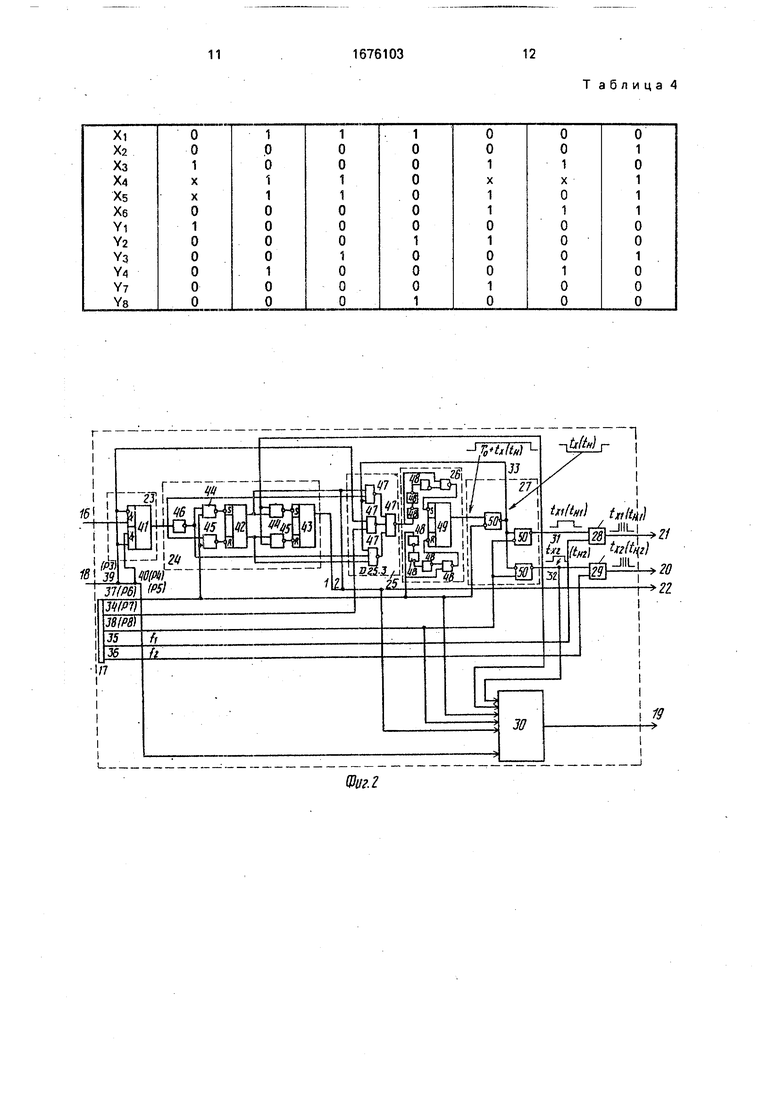

Входные переменные по порядку обозначают Х-|,Х2,Хз,Х4,Х5,Хб. Выходные сигналы, управляющие (шина 19), обозначают соответственно Yi,Y2,Y3.Y4,Y7,Ya. В табл.4 представлены переключательные функции для основного алгоритма, где X - произвольное состояние.

YI X1X2X3X4X5X6:

Y2 Х1Х2ХзХ4Х5Хб + Х1Х 2ХзХ4Х5Хб;

Ys XiX2X3X4XsXe + Х ХзХ ХбХе;

Y4 X1X2X3X4X5X5 + Х1Х2ХзХ4Х 5Хб;

Y Х 1X2X3X4X5X6;

Ys X 1X2X3X4X5X6.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий аналоговый коммутатор, первый аналоговый вход которого является входной шиной, второй аналоговый вход - через цифро-аналоговый преобразователь соединен с соответствующими первыми выходами счетчика старших разрядов, управляющий вход аналогового коммутатора соединен с первым выходом блока управления и контроля, а выход - через последова- тельно соединенные интегратор и компаратор соединен с первым входом блока управления и контроля, второй и третий выходы которого соединены соответственно с входом счетчика младших разрядов и первым входом счетчика старших разрядов, второй вход которого является шиной нормированного кода, отличающийся тем, что, с целью повышения функциональной надежности путем обеспечения непрерывного контроля узлов устройства, в него введены два регистра, причем выходы счетчика младших разрядов и вторые выходы счетчика старших разрядов соединены соответственно с первыми и вторыми входами первого регистра, третий вход которого соединен с четвертым выходом блока управления и контроля, четвертый вход первого регистра объединен с первым входом второго регистра и является шиной управления, пятый вход объединен с вторым входом второго регистра и является адресной шиной,

0 выходы первого регистра соединены с соответствующими третьими входами второго регистра и являются шиной данных, выходы второго регистра соединены соо ветствен- чо со вторыми входами блокз управления и

5 контроле

2, Преобразователе по л.1, о т л и ч а ю- щ и и с я тем, что бпок управления и контроля выполнен на программном устройстве, программной логической матрице, двух эле0 ментах И и последовательно соединенных оммутаторов каналов, блоке запоминания полярности, блока формирования выборок сигнала, широтно-импульсном модуляторе и коммутаторе, первый выход которого сое5 дичен с первыми входами первого элемента И, программной логической матрицы и вторым входом блокз запоминсзнич полярности, второй выход соединен с первым входом второго элемента И и вторым вхо

0 дом программной логической матрицы, третий выход коммутатора соединен с вторым входом блока формирования выборок сигнала, второй вход коммутатора соединен с первым выходом программного устройства

5 и третьим входом программной логической матрицы, второй выход программного устройства соединен с четвертым входом программной логической матрицы, вторым входом широтно-импульсного модулятора,

0 третьими входами блока запоминания полярности и коммутатора, третий, четвертый и пятый выходы программного устройства соединены соответственно с вторыми входами второго и первого элементов И и

5 третьим входом блока формирования выборок сигнала, четвертый вход которого соединен с первым входом коммутатора каналов, второй вход которого является первым входом блока третий вход объединен с

0 его четвертым входом, с пятым входом программируемой логической матрицы и является Еторым входом блока, второй выход блока запоминания полярности объединен с его первым выходом, соединен с

5 шестым входом программируемой логической матрицы и является четвертым выходом б 1ока, третий, четвертый и пятый выходы блока запоминания полярности соединены соответственно с пятым, шестым и седьмым сходами блока формирования выборок сигнала, выходы программируемой логической матрицы, первого и второго элементов И являются соответственно первым, третьим и вторым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Система автоматического пожаротушения | 1987 |

|

SU1461486A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

Изобретение относится к измерительной технике. Цель изобретения - повышение функциональной надежности путем обеспечения непрерывного контроля узлов устройства. Это достигается тем, что в устройство, содержащее аналоговый коммутатор 2, интегратор 4, цифроаналоговый преобразователь 3, компаратор 5, счетчики 6, 7 младших и старших разрядов, блок 10 управления и контроля, введены регистры 8, 11. 1 з.п ф-лы, 4 табл., 4 ил.

п

етка Мнемоника ачало CALL

MVIA

OUT

MVIA

OUT

MVIA

OUT

MVIA OUT

MVTA OVT

MVTA OVT

CALL

MVIA OVT

MVIA OUT

MVIA OVT

Операнд

INI

Ф1

ADPZ

Ф1

ADP3

ФФ

ADP5

ФФ ADP8

Ф1 ADP4

Ф1 ADP6

TIMET

фф ADP6

Ф1 TIMEPF1

Ф1 ADPZ

Таблица 1

Таблица 2

Таблица 3

I

Комментарий

Подпрограмма инициализации портов тайм и установка начальных условий АЦП

Установка режима регистра 11 PZ

Регистр 11 .- блок 24 подключение к 23 порта РЗ и Р7 к 25 Отключение 4701, 47,3, формирующих tXo Подключение Р5 к 30 К, - К„ : - О

Разрешается прохождение tm блока к 28„ После квантования в 28 на 7 пост 1099 импульсов (первая выборка)

Подключается Р4 к 23 положительная полярность

Формирование Тв

Запись знака из порта Р4 в 42

CALL TAMEToi подпрограмма время TOJ

Включается таймер

Формирование tn«

на 8 проходит 1099 импульсов

1676103

1 10

Продолжение табл„ 3

CD-J.&.CJNJ- CnOl CJM-.

OOOOO- OX X

oo- oooo- - o o-

- ooo- oooooo-

К дых 79

Я

59

60

61

62

66

64

К

| Устройство контроля аналого-цифрового преобразователя | 1974 |

|

SU790289A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегрирующий цифровой вольтметр | |||

| СТАКАН ДЛЯ СУШИЛЬНОГО ШКАФА | 1927 |

|

SU6567A1 |

| Прибор для измерения глубины воды под судном в мелководные, местах с применением качающегося рычага | 1925 |

|

SU2608A1 |

Авторы

Даты

1991-09-07—Публикация

1989-06-21—Подача