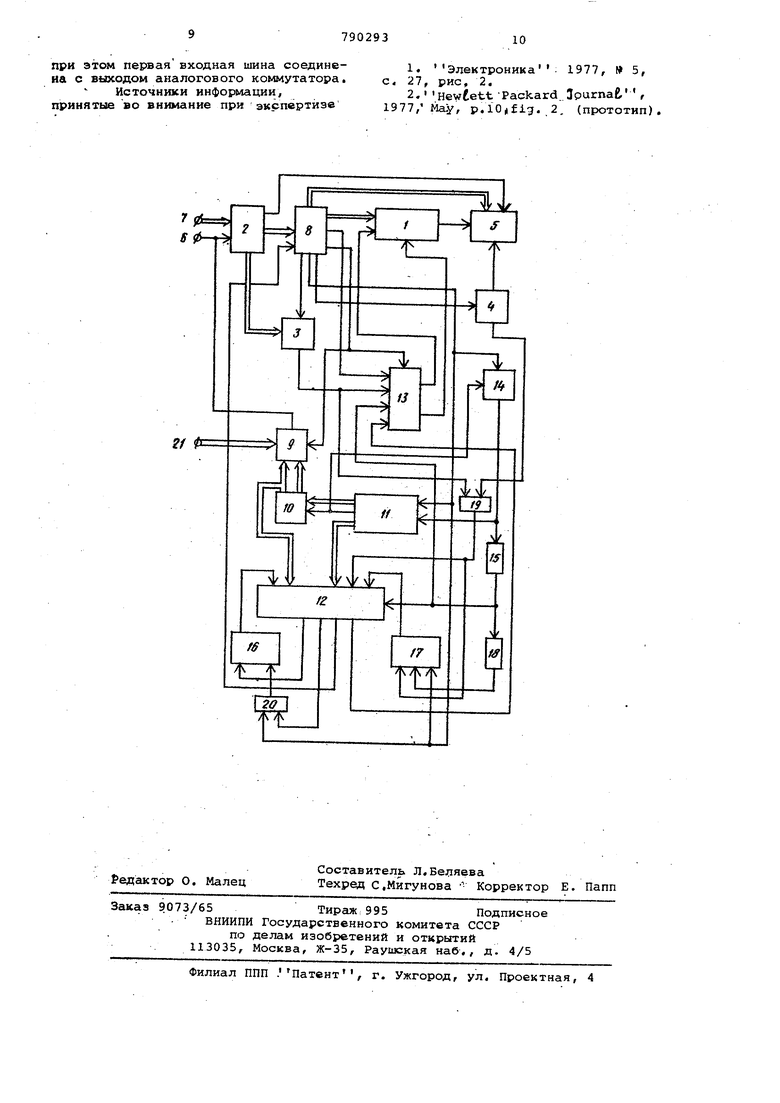

Изобретение относится к импульсной технике и,в частности преднаэначено для проведения проверки правильности функционирования аналого-цифровых преобразователей. Известно устройство сигнатурной проверки правильности функционирования логических блоков, содержащее анализатор, состоящий из сдвигающего регистра с обратными связями через входной су иматор по моду.гао два, и цифровой индикатор. Сигнатурная проверка заключается в том,что последовательность выходны сигналов проверяемого логического уз ла подают на информационный вход сцг натурного анализатора. За время межд импульсами начала и конца проверки из этой последовательности на выхода регистра сигнатурного анализатора . формируется код сигнатуры (четырехразрядное шестнадцатеричное число), который высвечивается на индикаторе. Неправильно работающий логический узел определяется по несовпадению по лученной и контрольной для этого узл сигнатуры 1. Недостатком этого устройства является отсутствие проверки уровней .сигналов, представляющих проверяемую входную последовательность, а также отсутствие средств для контроля узлов устройства. Известно также устройство сигнатурной проверки, содержащее сигнатурный анализатор, блок детекторов, элемент фиксации кода, блок контроля, . блок индикации, первую и вторые входные шины и блок управления, при этом первая и вторые входные шинь соединены соответственно с первым и вторыми входами блока детекторов, соединенного первыми выходами с первыми входами элемента фиксации кода, вторыми выходами - с первыми входами блока управления и третьим выходом с первым входом блока индикации, в котором вторые входы соединены с первыми выходами блока управления, третий вход - с первым выходом блока контроля и четвертый вход - с ВЕЫХОДОМ сигнатурного анализатора, соединенного первыми входами со вторыми выходами блока управления, третий выход которого соединен со входом блока контроля и четвертый выход - со вторым входом элемента фиксации кода, выход которого соединен с информационным входом сигнатурного анализатора. 1соединённого входом синхронизации с |пятым-выходом блока управления 2. Недостаток этого устройства заключается в отсутствии возможности Г1роверки правильности функционирования аналого-цифровых преобразователе при поквантовом изменении аналогового сигнала на всем диапазоне. Цель изобретения - повышение достоверности проверки аналого-цифровых преобразователей. Поставленная цель, достигается тем что в устройство сигнатурной проверки аналого-цифровых преобразователей,. .содержащее первую и вторую входные шины, соединенные соответственно с первым и вторыми входами бло ка детекторов, соединенного первыми.выходами с первыми входами- элемента фиксации кода, вторыми выходами - с первыми входами блока управления и третьим выходом- с первым входом блок индикации, в котором вторые входы сое динены с первыми выходами блока упра ления,третий вход - с первым выходом блока контроля и четвертый вход. - с. выходом сигнатурного анализатора,соединенного первыми входами со вторыми выходами блока управления,третий выход которого соединен со входом блок контроля и четвертый выход - со вторы входом элемента фиксации кода, введены аналоговый коммутатор, дешифратор счетчик, блок постоянной памяти, блок перек.лючателей, запускаемый генератор импульсов, формирователь импульсов, первый и второй триггеры, элемент задержки, первый и второй элементы ИЛИ причем шина кодовых входов соединена с первыми входами аналогового коммутатора, вторые , входы которого соедине ны с первыми выходами дешифратора,тре тьи входы соединены со вторыми входам дешифратора и с первыми входами блок постоянной памяти, четвертый вход с пятым выходом блока управления и с первым входом блока переключателей, первым и вторым выходами соединенного соответственно с информационным и синхронизирующим входами сигнатурного анализатора, вторым входом - с шестьм выходом блока управления, третьим входом - с выходом элемента фиксации кода и с первым входом первого элемента ИЛИ, четвертым входом - с выходом формирователя импульсоё, со вторым входом блока постоянной памяти и( со входом элемента задерижи, выхс)д .которого подключен к синхрониэирующему входу первого триггера, при этом пятый вход блока переключателей соединен с первым выходом блока постоянной памяти, второй и третий входы которого, соединены с единичными выходами соотйетствённо первого и второго триггеров,- четвертьй вход с выходом первого элемента ИЛИ и с информационным входом первого трйг гера пятые входы - с первыми выходам I счетчика, вторым выходом подсоединен1НОГО к первому входу дешифратора и ко входу сброса запускаемого генератора импульсов, третьими выходами го вторьнии входами дешифратора,счетным входом - с выходом запускаемого, ге нератора импульсов и со входом формирователя импульсов, входом гашения - с седьмым выходом блока управления, с запускающим входом запускаемого генератора импульсов, со входом гашения первого триггера и с первым входом второго элемента ИЛИ, подсоединенного выходом и вторым входом соответственно к входу гашения вторЬго триггера и к второму выходу блОка постоянной памяти, третий и четвертый выходы которого соединены соответственно с единичным входом второго триггера и со вторым входом блока управления,а второй выход блока контроля соединен со вторым входом первого- элемента ИЛИ,, при .этом первая входная шина соединена с выходом аналогового коммутатора. Да- чертеже представлена структурная схема устройства сигнатурной проверки аналого-цифровых преобразователей. . . Устройство содержит сигнатурный анализатор 1, блок 2 детекторов, элемент 3 фиксации кода,блок 4 контроля, блок 5 индикации, первую 6 и вторую 7 входные шины, блок 8 управления, аналоговый коммутатор 9, дешифратор 10, сЧетчйк 11, блок 12 постоянной памяти, блок 13 переключа теле йс, запускаемый генератор 14 импульсов, формирователь 15 импульса,- второй 1.6 и. первый 17 триггеры,элемент 18 задер-. жки, первый 19 и 20 элементы ИЛИ, шину 21 кОд.овых входов. Проверка аналого-цифрового преобразователя (АЦП) производится путем получения сигнатуры из кодов результатов преобразо вания, выполняемых п оследовательно во времени для всех квантовых уровней входного сигнала. Параллельный код результата каждого преобразования преобразуется в соответствующий последовательный код,который подается на информационный вход сигнатурного анализатора. При этом коды результатов преобразований,выполняемых с допустимой погрешностью ±1 младшего з начащего разряда.,- преобразуется в последовательный код, эквивалентный эталонному значению проверяемого квантового уровня аналогового сигнала,; Непосредственное и.спользование кода результата преобразования Для проверки АЦП сигнатурным анализатором без промежуточного преобразования кода в эталонньгй код -.невозможно, так как при правильной, ра-боте АЦП для одного и того же в.ходнОго. сигнала могут образовываться на его выходах коды,отличающиеся на +1 младшего зна чающего разряда. Таким образом, если АЦП выполняет преобразование для всех квантовых уровней входного сигнала с погрешностью, не превращающей ±.1 младшего значащего разряда, то полученная ито говая сигнатура не должна отличаться от контрольной, эквивалентной иде альной работе АЦИ, При выполнении преобразования для одного или нескольких квантовых уровней входного сигнала с погрешностью, превышающей +1 младшего значащего разряда, итоговая сигнатура отличается от контрольной, что говорит о работе АЦП с погрешностью, превышающей допустимую. Устройство работает следующим образом. При проверке правильности функцио нирования АЦП его кодовые выходы под соединяют к шине 21, а входные шины соединяют с выходами элементов, формирующих импульсы начала и конца про верки и импульсы синхронизации. Последними в данном случае являются импульсы конца выполнения каждого анало го-цифрового преобразования, В качес ве импульса конца проверки может быть использован импульс переполнения счет чика внешнегокалибра, вырабатывающе контрольные аналоговые сигналы, поступающие на вход проверяемого АЦП и изменяющиеся на квант от ка-ждого импульса конца преобразования. В режиме проверки АЦП по сигналу начала проверки, поступающему через одну из входных шин 7 и блок 2 на вход блока 8 управления, последний устанавливает в исходное состояние сигнатурный анализатор 1,элемент 3 фиксации кода и блок 4 контроля,а та же устанавливает сигналом на пятом выходе в соответствующее состояние блок 13 переключателей и подключает выход коммутатора 9 к первой в.ходной шине 6.в результате этого вход синхро низации и информационный вход сигнатурного анализатора соединяются через блок 13 соответстйенно с выходом формироватеЛя 15 и первым выходом блока Каждый внешний импульс синхрониза ции проходит через блок 2 и элемент фиксации кода и производит гашение счетчика 11 и триггеров 16 и 17, а также запускает генератор 14, импуль сов. Выходные импульсы генератора 14 пересчитываются счетчиком 11, а также поступают через формирователь 15 на стробирующий вход блока 12 постоя ной памяти и через блок 13 - на сиихронйзирующий вход сигнатурного анализатора 1.Кроме того,через элемент 18 импульсы с выхода формирователя 1 поступают на вход синхронизации триг гера . 17. Второй и третий выходы счетчика 11 управляют через дешифратор 10 переключением каналов коммутатора 9. Последний преобразует параллельный код, поступающий с выходов проверяемого АЦП, в последовательный код,начиная с младшего разряда.Таким образом, после появления первого импульса на выходе генератора 14 к первой входной шине б подключается с помощью коммутатора 9 младший разряд выходного кода АЦП. Далее этот сигнал проходит через блок 2, в котором осуществляется проверка соответствия уровня этого разряда стандартному нулевому или единичному уровням логического сигнала . При правильном значении этого уровня сигнал запоминается в элементе 3 фиксации кода и, пройдя через элемент ИЛИ 19, поступает на информационный вход триггера 17 и на четвертый вход блока 12. Адресными входами блока 12 являются также выходы двух старших разрядов счетчика 11 (первые его выходы), выходы триггеров 16 и 17, а также два младших выхода дешифратора 10 (его вторые выходы). Выходной код блока 12 в этом случае определяется только значением младшего разряда кода результата преобразования в АЦП. ЕСЛИ значение этого разряда равно нулю, то на всех выходах блока 12 устанавливается нулевой код. Если указанное значение равно единице, то на третьем выходе блока 12 появляется единичный сигнал, которым триггер 16 устанавливается в единичное .состояние. .Сигнал с первого выхода блока 12 поступает через блок 13 на информационный вход сигнатурного анализатора 1 , в котором фиксируется в соответствии с его алгоритмом работы. Через время, определенное элементом 18, значение младшего разряда выходного кода АЦП фиксируется в триггере 17. Формирование на первом выходе блока 12 нулевого значения в случае еди ничного значения младшего разряда выходного кода АЦП эквивалентно изменению этого кода на единицу. Установление триггера 16 в единичное состояние является подготовкой к возможной инверсии Значения последуюц их разрядов выходного кода АЦП. Вторым выходным импульсом генератора 14 с помощью счетчика 11, дешифратора 10 и коммутатора 9 подключается к четвертому входу блока 12 второй разряд выходного кода АЦП. При этом, если значение этого разряда нулевое, то блок 12 формирует на первом выходе нулевой сигнал, а на втором выходе единичный сигнал.1 Последним гасится триггер 16 через элемент 20.. Если значение второго разряда единичное, то нулевой сигнал формируется не только на первом,но также и на втором е выходе,и Триггер 16 остается в един ном.сос то янии. При появлении последующих выходных мипульсов генератора 14, число которых на единицу или более превышает число разрядов проверяемого АЦ блок 12 формирует на своем первом выходе нулевое значение (в общем случае инверсное по отношению к зна чению подключенного разряда выходно кода АЦП до тех пор, пока не будет несовпадения значений, очередного и предыдущего разрядов кода результата АЦП. В последнем случае на перво выходе блока 12 формируется сигнал, совпадающий со значением подключенн го разряда АЦП. Следовательно, если код двух старших разрядов счетчика 11 ке соответствует коду двух младш разрядов кода результата преобразов ния АЦП, то последний изменяется (уменьшается или увеличивается) на единицу. Преобразованное таким образом зн чение кода результата преобразовани далее поступает младшими разрядами вперед на информационный вход сигнатурного анализатора. Если преобразованное значение каж,цого выходного кода АЦП соответствует контрольному значению каждого входного квантового уровня, то следовательно, преобразования выпол нены с допустимой погрешностью, не превышающей ±1 младшего значащего разряда, и окончательное значение сигнатуры н-е изменяется по сравнени с эталонным ее значением. Сигнатурная проверка аналого-циф вых преобразователей в этом устройстае выполняется не поразрядно, а целиком для всего кода результата .. . преобразования, что значительно сокращает время проверки таких сложны устройствJ какими являются аналогецифровые преобразователи. Формула изобретения Устройство сигнатурной проверки аналого-цифровых преобразователей, содержащее первую и вторую входные шины, соедин-енне соответственно с первым и вторыми входами блока .деTei TopoB ,,: соединенного первыми выхЪдами с первьзми входами элемента фиксации кода, вторыми выходами с первь5ми входами блока управления третьим выходом - с первым входом блока .индикации, в котором вторые входы соединены с первыми выходами блока управления, третий вход --с первым выходом блока контроля и чет вертьай вход.- с выходом сигнатурног анализатора, соединенного первыми входами со вторыми выходами блока управления, третий выход которого соединен со входом блока контроля и четвертый выход - со вторым входом элемента фиксации кода, о т л и ч аю щ е е с я тем, что, с целью повышения добтоверности проверки аналого-цифровых преобразователей, в него введены аналоговый коммутатор, де- i шифратор, счетчик, блок постоянной памяти, блок переключателей,запускаемый генератор импульсов, формирова-. тель импульсов, первый и второй триггеры, элемент задержки, первый и второй элементы ИЛИ, причем шина кодовых входов соединена с первыми входамианалогового коммутатора, вторые входы которого соедине-; ны с первыми выходами дешифратора, третьи входы соединены со вторыми вы-, ходами дешифратора и с первыми входами блока постоянной п&мяти,четвертый вход - с пятым выходом блока управления и с первым входом блока переключателей, первым и вторым вЕ Ходамй сов- диненного соответственно с информационным и синхронизирующим входами сигнатурного анализатора, вторым вхо-. дом - с шестым выходом блока управления, третьим входом - с выходом элемента фиксации кода и с первым входом первого элемента ИЛИ, четвертьам входом - выходом формирователя импульсов, со вторым входом блока постоянной памяти и со входом элемента, задержки, выход которого подключен к синхронизирующему входу первого триггера, при этом пятый вход блока переключателей соединен с первым выходом блока постоянной памяти, второй и . третий входы которого соединены с единичными выходами соответственно первого и второго триггеров, четвертый вход - с.выходом первого элемента ИЛИ и с информационным входом первого триггера; пятые входы - с первыми выходами счетчика, вторым выходо м подсоединенного е первому входу дешифратора .и ко входу сброса запускаемого генератора импульсов, третьими выходами - со вторыми входами дешифратора, счетным входом - с выходом, запускаемого генератора импульсов и со входом формирователя импульсов, входом гашения и с седьмь1м выходом блока управления, с запускающим входом запускаемого генератора импульсов, со входом гашения первого триггера и с первым входом второго элемента ИЛИ, подсоединенного выходом и вторым входом соответственно ко вхолу гашения второго триггера и ко второму выходу блока постоянной памяти, третий и четвериый выход которого соединены соответственно с единичным входом второго триггера и со вторым входом блока управления, а второй выход блока контроля соединен со вторым входом первого элемента ИЛИ,

при этом первая входная шина соединена с выходом аналогового коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Электроника : 1977, 5, с. 27, рис, 2.

2.Hewlett Packard. ЗригпаЬ , 1977, May, p.iO(fig..2, (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

Авторы

Даты

1980-12-23—Публикация

1979-02-20—Подача