Изобретение относится к импульсной технике и может быть использовано в системах дискретной-автоматики

Целью изобретения является уменьшение потребляемой мощности.

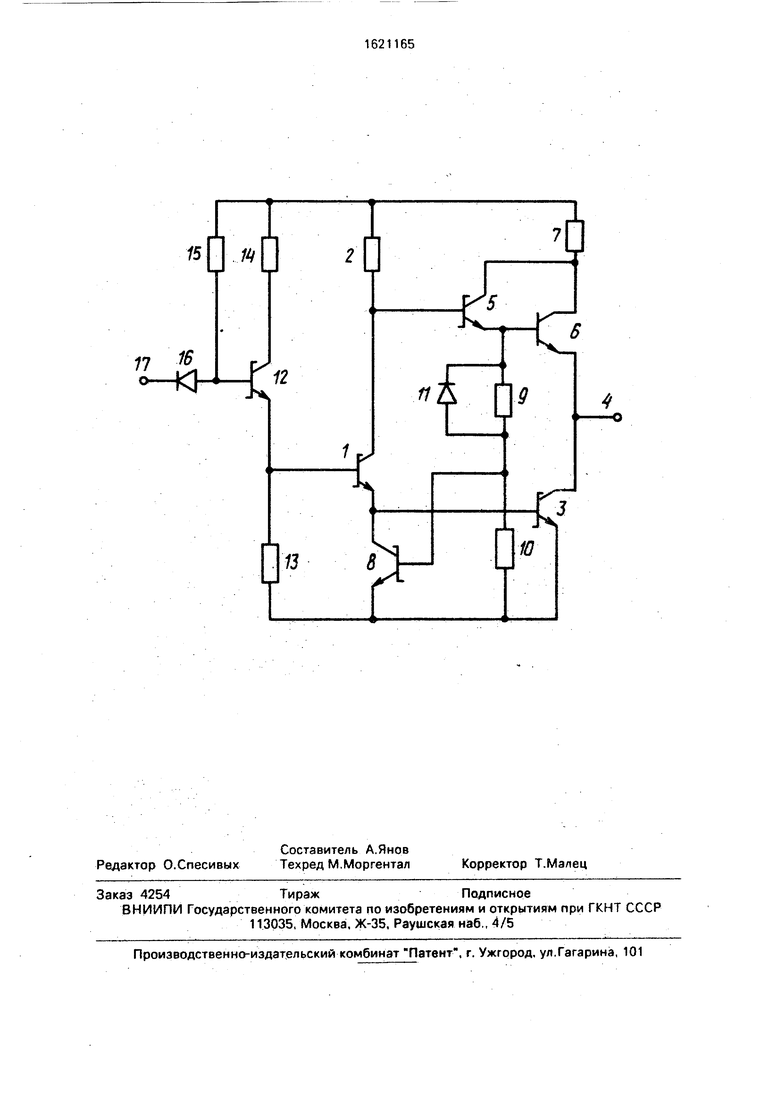

На чертеже приведена принципиальная электрическая, схема транзисторного логического элемента.

Транзисторный логический элемент, содержит фазоразделительный транзистор 1, коллектор которого подключен через первый резистор 2 к шине питания, эмиттер к базе выходного транзистора 3, эмиттер которого соединен с общей шиной, а коллектор с эмиттером составного транзистора и выходом 4. Составной транзистор включает первый 5 и второй 6 транзисторы, соединенные так, что коллекторы их объединены и образуют коллектор составного транзистора, подключенный через седьмой резистор 7 к шине питания, база транзистора 5 образует базу составного транзистора, эмиттер транзистора 5 соединен с базой транзистора 6, а эмиттер транзистора 6 образует эмиттер составного транзистора, коллектор третьего транзистора 8 подключен к базе

транзистора 3 эмиттер к общей шине, а база соединена с выводами третьего 9 и второго 10 резисторов, анодом второго диода 11, катод которого подключен к второму выводу резистора 9 и эмиттеру транзистора 5, второй вывод резистора 10 подключен к общей шине, база транзистора 5 подключена к коллектору транзистора 1, база которого подключена к эмиттеру входного транзистора 12 и через четвертый резистор 13 к общей шине, коллектор и база транзистора 12 через пятый 14 и шестой 15 резисторы соединены с шиной питания, база транзистора 12 подключена к аноду первого диода 16, катод которого соединен с входом 17.

Транзисторный логический элемент работает следующим образом

Пусть на входе 17 низкий уровень напряжения, Тогда транзисторы 1,12,3 закрыты, так как отсутствует ток в базовых цепях этих транзисторов. На выходе 4 будет установлен высокий уровень напряжения, определяемый открытыми транзисторами 5 и 6 составного транзистора Транзистор 8 открыт, так как на его базу передается напрясл

с

ч

Жение высокого уровня через резистивный делитель, образованный резисторами 9 и 10. При изменении напряжения на входе с низкого на высокий диод 16 запирается и в базу транзистора 12 поступает ток от шины 5 питания через резистор 15. Транзистор 12 открывается и в его коллекторной цепи протекает ток, определяемый резистором 14 и поступающий в базу транзистора 1. Транзистор 1 открывается, в его коллекторной 10 цепи протекает ток, определяемый рези- стором 2, который через цепь коллектор - эмиттер открытого транзистора 8 протекает в общую шину и потенциал на коллекторе транзистора 1 уменьшается. Цепь коллек- 15 тор - эмиттер транзистора 8 шунтирует переход база - эмиттер выходного транзистора 3 и он продолжает оставаться закрытым. Таким образом, происходит снижение потенциала на базе составного транзистора 20 и соответственно снижение высокого уровня напряжения на выходе схемы при отключенном выходном транзисторе. Резистивный делитель передает понижение напряжения с базы составного транзистора 25 на базу транзистора 8 и он начинает выключаться. Эмиттерный ток транзистора 1 начинает поступать в базу выходного транзистора 3, и транзистор 3 открывается. Следовательно, установление на выходе 30 схемы низкого уровня напряжения происходит при уже отключенном составном транзисторе и таким образом сквозной ток при переходе выхода 4 из высокого состояния в низкое устраняется.35

При переходе входного сигнала с высокого уровня на низкий происходит открывание диода 16 , транзисторы 12 и 1 закрываются.

Возрастание потенциала на коллекторе 40 транзистора 1 до величины двух переходов база - эмиттер приводит к броску тока в базу транзистора 8 через короткозамкнутую в первый момент времени емкость обратно смещенного диода 11. Транзистор 8 откры- 45 вается, и на эмиттере транзистора 1 происходит резкое снижение потенциала. Так как напряжение на базе транзистора 1 из-за .1чия высокоомного резистора 13 изменяется медленно, то происходит кратковре- 50 менное дополнительное открывание транзистора 1 за счет разряда его диффузионной емкости через эмиттерный переход и, таким образом, замедление нарастания потенциала на коллекторе транзистора 1.55

Это замедление нарастания потенциала на базе составного транзистора и наличие низкоомной цепи коллектор - эмиттер транзистора 8 для выключения выход-. ного транзистора.3 обеспечивает устранение сквозного тока при переходе выхода схемы из низкого состояния в высокое. Резистор 7 необходим для ограничения тока при коротком замыкании на выходе схемы. Таким образом, предложенное техническое решение позволяет устранить сквозной ток при переключении элемента, т.е. уменьшается средняя потребляемая схемой мощность, а также повысить быстродействие при переходе с низкого уровня в высокий

Формула изобретения

Транзисторный логический элемент, содержащий два диода, фазоразделительный транзистор, коллектор которого подключен через первый резистор к шине питания и базе составного транзистора, который включает в себя первый и второй транзисторы, коллекторы которых объединены и образуют коллектор составного транзистора, база первого транзистора образует базу составного транзистора, эмиттер первого транзистора соединен с базой второго транзистора, а эмиттер второго транзистора образует эмиттер составного транзистора, который подключен к выходу и коллектору выходного транзистора, эмиттер которого подключен к общей шине, а база - к эмиттеру фазоразделитель- ного транзистора и коллектору третьего транзистора эмиттер которого подключен к общей шине, а база через второй резистор подкпюченэ к общей шине, эмиттер первого транзистора соединенс первым выводом третьего резистора-, база фазоразде- лительного транзистора подключена к эмиттеру входного транзистора и через четвертый резистор к общей шине, коллектор и база входного транзистора соответственно через пятый и шестой резисторы подключены к шине питания, база входного транзистора подключена к аноду первого диода, катод которого соединен с входом логического элемента, коллектор составного транзистора через седьмой резистор соединен с шиной питания, отличаю щи й- с я тем, что. с целью уменьшения потребляемой мощности, второй вывод третьего резистора подключен к базе третьего транзистора и Y аноду второго диода, катод которого соединен с первым аыводом третьего резистора.

«U

/4

77

/5

o-KF

U

с

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| ТТЛШ-вентиль | 1988 |

|

SU1599984A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

Изобретение относится к импульсной технике и может быть использовано в системах дискретной автоматики. Цель изобретения - уменьшение потребляемой мощности. Транзисторный логический элемент, содержит два диода, семь резисторов, фазораз- делительный транзистор, составной транзистор, выполненный на первом и втором транзисторах, выходной транзистор, третий транзис ор и входной транзистор Введение новых связей позволяет уменьшать среднюю потребляемую мощность путем исключения протекания сквозных токов. 1 ил

#

| Патент США №4552389, кл.Н 03 К 19/088, 1985 | |||

| Патент США N 4330723, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-15—Публикация

1988-08-15—Подача