о Я ft о////

tfmt

1Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для построения устройств для деления чисел. Целью изобретения является повышение быстродействия. Устройство содержит группу вычислительных узлов 1-i-1m группу узлов 2 формирования функций генерации и транзита переноса и введен ную группу узлов формирования переноса из старшего разряда. 6 ил.

гг

дг

///

art

о

ы о о о

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Цель изобретения - повышение быстродействия устройства.

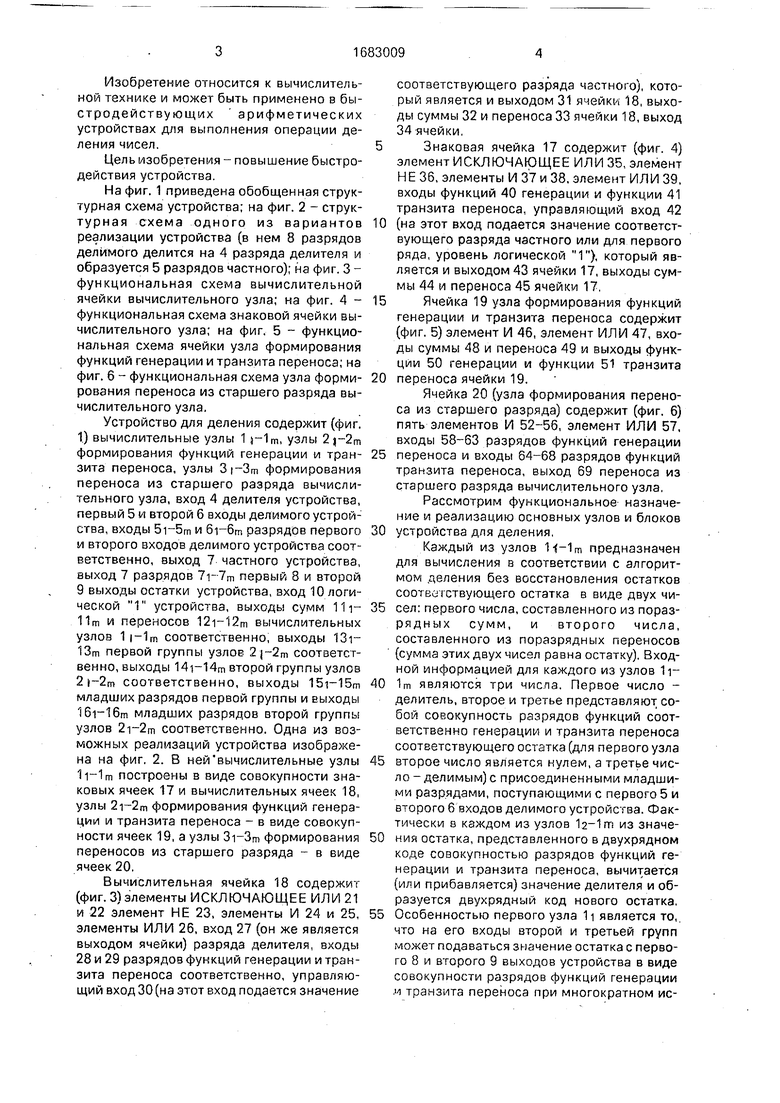

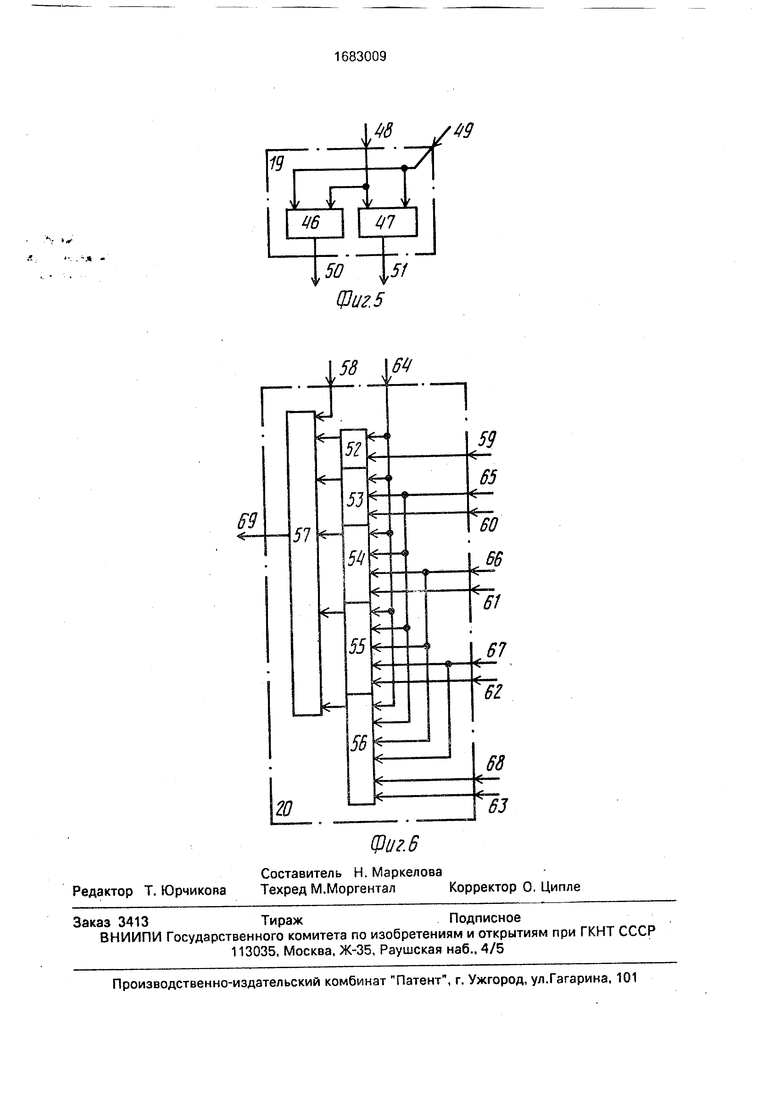

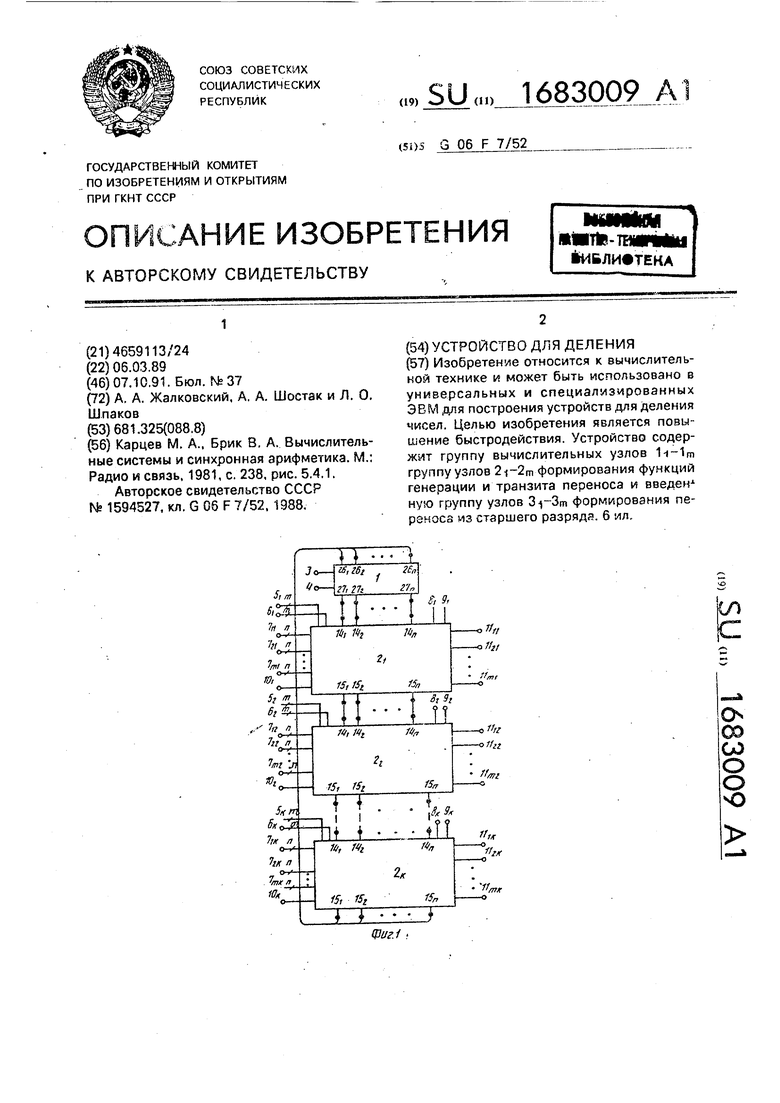

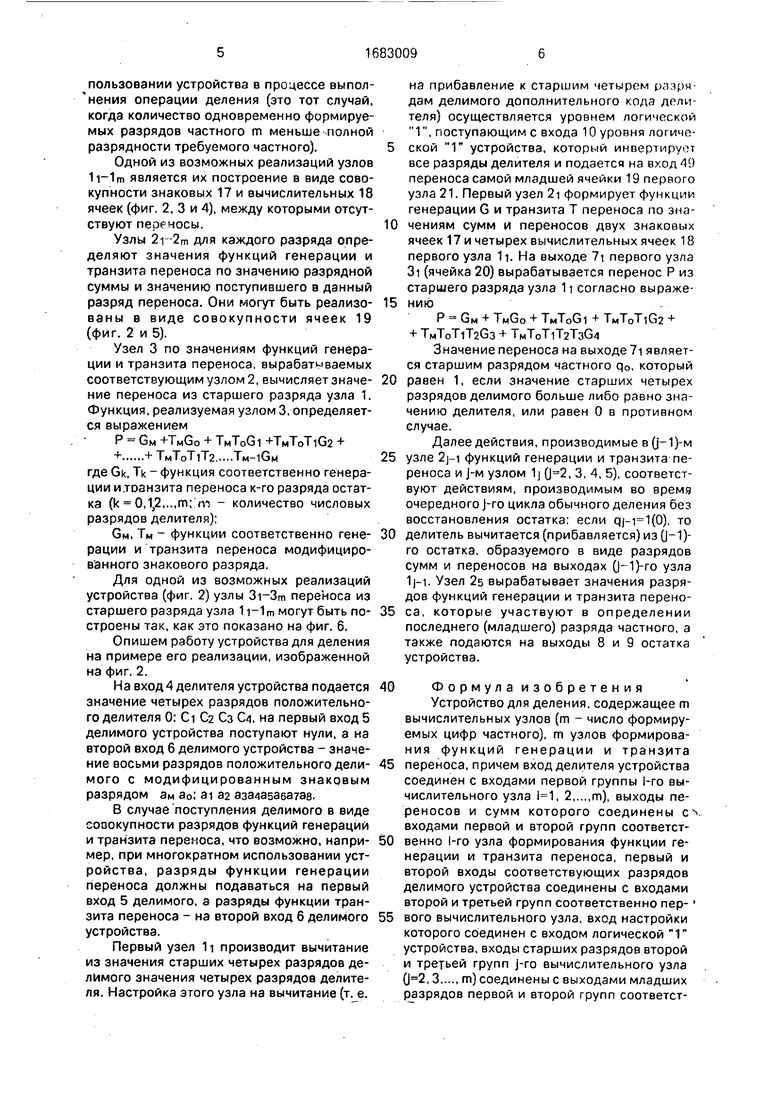

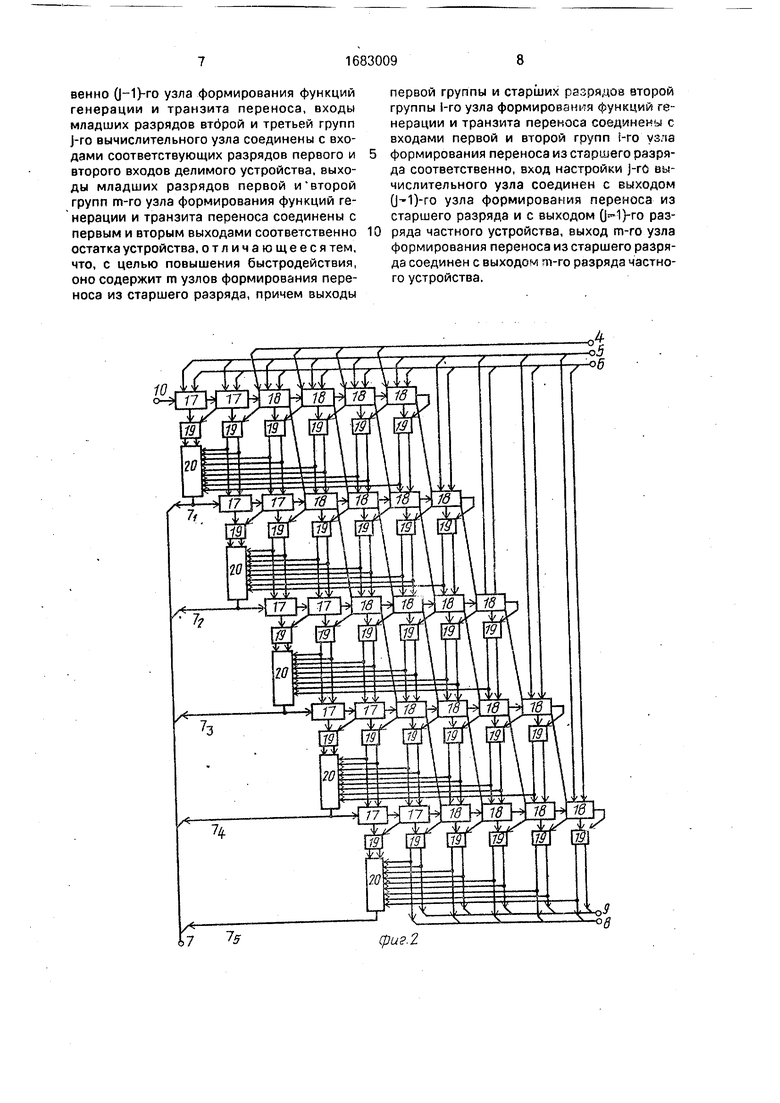

На фиг. 1 приведена обобщенная структурная схема устройства; на фиг. 2 - структурная схема одного из вариантов реализации устройства (в нем 8 разрядов делимого делится на 4 разряда делителя и образуется 5 разрядов частного); на фиг. 3 - функциональная схема вычислительной ячейки вычислительного узла; на фиг. 4 - функциональная схема знаковой ячейки вычислительного узла; на фиг. 5 - функциональная схема ячейки узла формирования функций генерации и транзита переноса; на фиг. 6 - функциональная схема узла формирования переноса из старшего разряда вычислительного узла.

Устройство для деления содержит (фиг. 1) вычислительные узлы 1 &-1т, узлы 2|-2т формирования функций генерации и транзита переноса, узлы 3|-3т формирования переноса из старшего разряда вычислительного узла, вход 4 делителя устройства, первый 5 и второй 6 входы делимого устройства, входы и разрядов первого и второго входов делимого устройства соответственно, выход 7 частного устройства, выход 7 разрядов первый 8 и второй 9 выходы остатки устройства, вход 10 логической 1 устройства, выходы сумм 11 )- 11m и переносов 12i-12m вычислительных узлов 1 |-1т соответственно, выходы 13i- 13m первой группы узлов 2j-2m соответственно, выходы 14i-14m второй группы узлов 2 j-2m соответственно, выходы 15i-15m младших разрядов первой группы и выходы 16i-16m младших разрядов второй группы узлов 2i-2m соответственно. Одна из возможных реализаций устройства изображена на фиг, 2. В ней вычислительные узлы 1l-1m построены в виде совокупности знаковых ячеек 17 и вычислительных ячеек 18, узлы 2i-2m формирования функций генерации и транзита переноса - в виде совокупности ячеек 19, а узлы 3i-3m формирования переносов из старшего разряда - в виде ячеек 20.

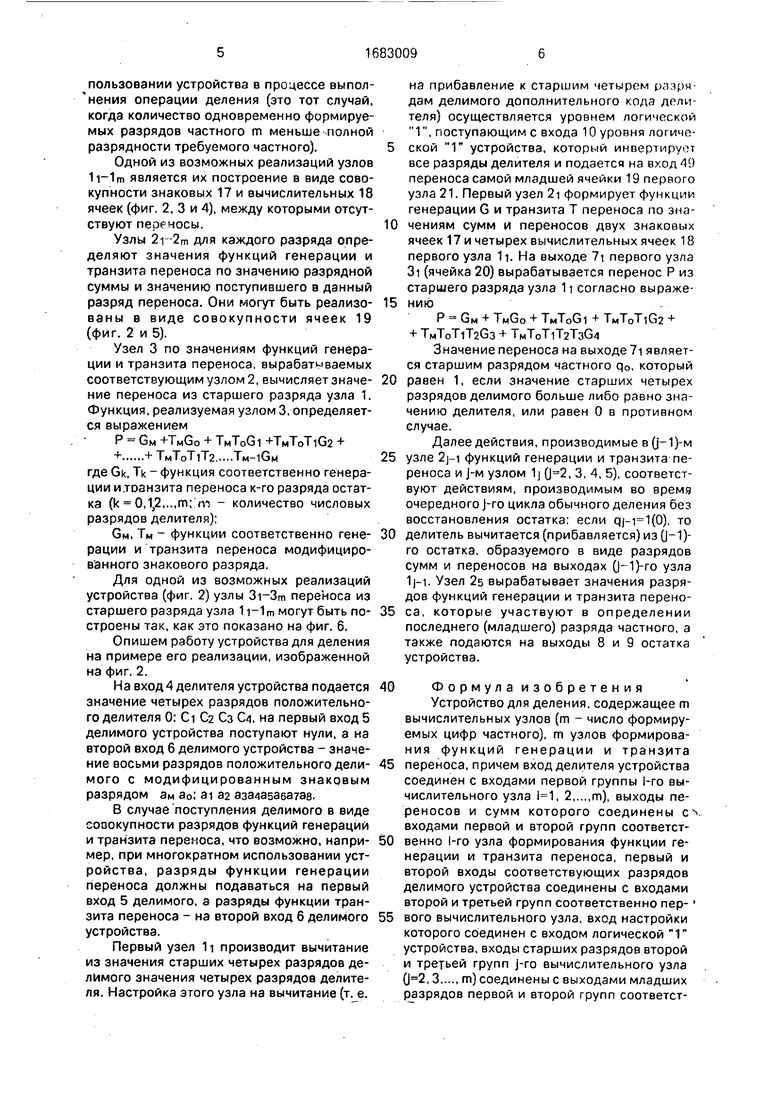

Вычислительная ячейка 18 содержит (фиг. 3) элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21 и 22 элемент НЕ 23, элементы И 24 и 25, элементы ИЛИ 26, вход 27 (он же является выходом ячейки) разряда делителя, входы 28 и 29 разрядов функций генерации и транзита переноса соответственно, управляющий вход 30 (на этот вход подается значение

соответствующего разряда частного), который является и выходом 31 ячейки 18, выходы суммы 32 и переноса 33 ячейки 18, выход 34 ячейки,

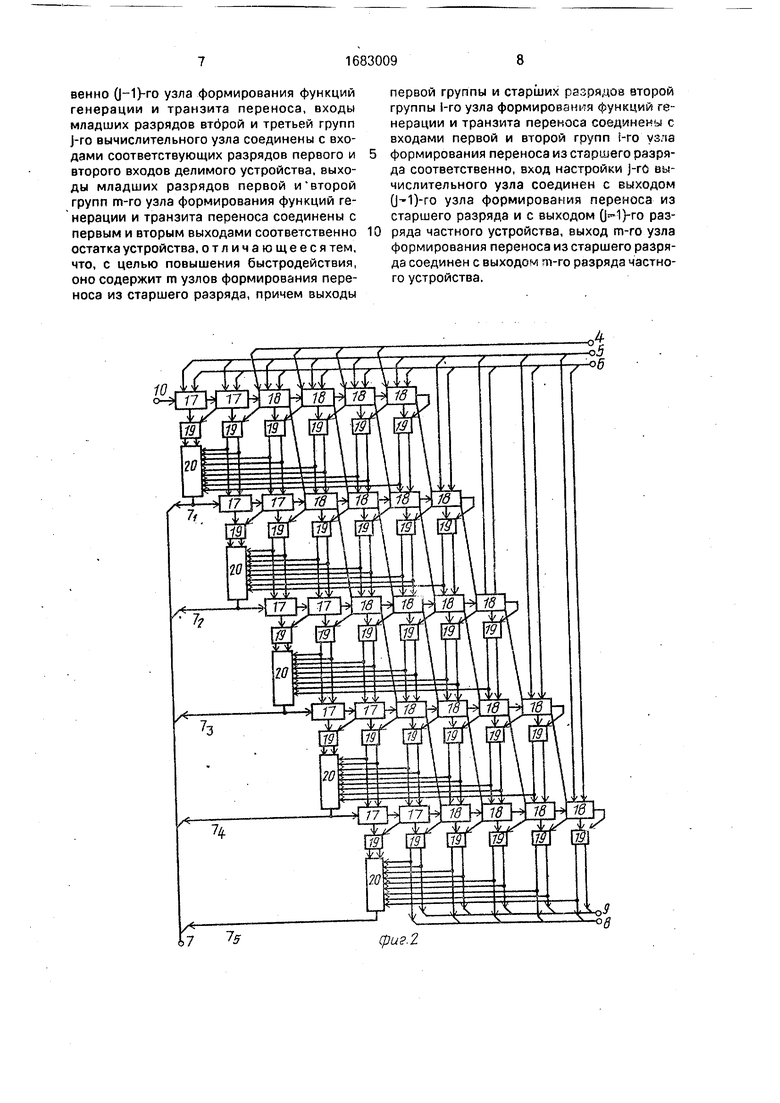

Знаковая ячейка 17 содержит (фиг. 4)

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 35, элемент НЕ 36, элементы И 37 и 38, элемент ИЛИ 39, входы функций 40 генерации и функции 41 транзита переноса, управляющий вход 42

0 (на этот вход подается значение соответствующего разряда частного или для первого ряда, уровень логической 1), который является и выходом 43 ячейки 17, выходы суммы 44 и переноса 45 ячейки 17.

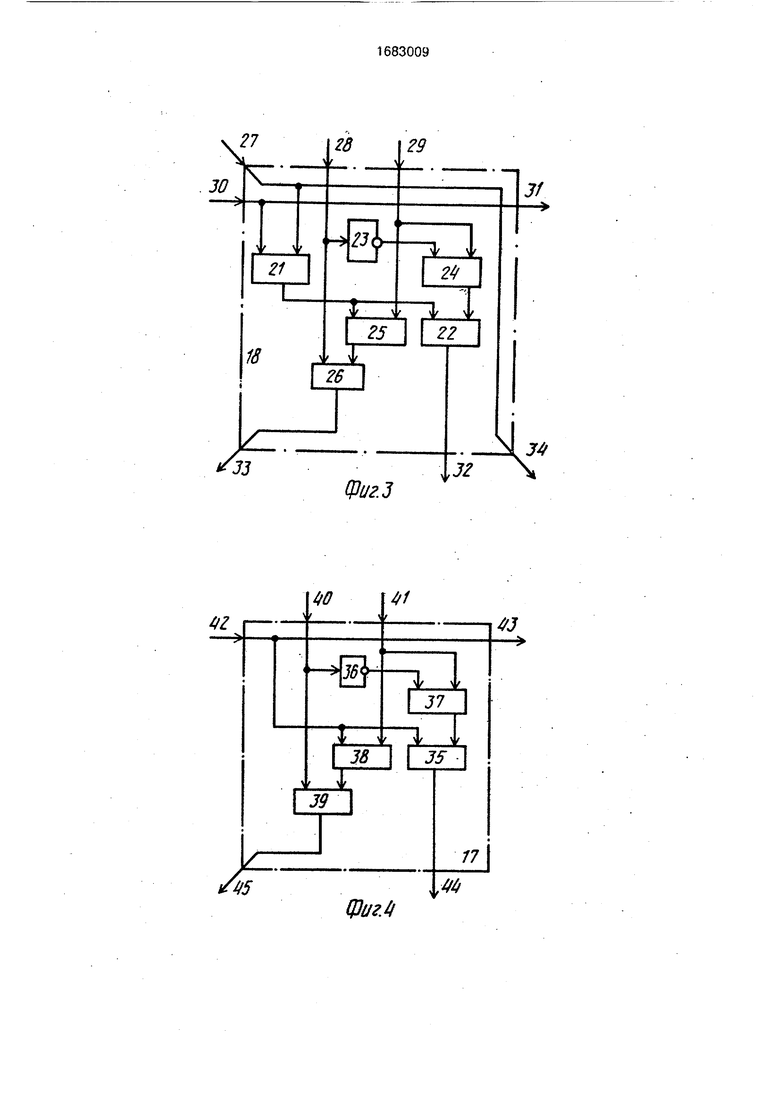

5 Ячейка 19 узла формирования функций генерации и транзита переноса содержит (фиг, 5) элемент И 46, элемент ИЛИ 47, входы суммы 48 и переноса 49 и выходы функции 50 генерации и функции 51 транзита

0 переноса ячейки 19.

Ячейка 20 (узла формирования переноса из старшего разряда) содержит (фиг. 6) пять элементов И 52-56, элемент ИЛИ 57, входы 58-63 разрядов функций генерации

5 переноса и входы 64-68 разрядов функций транзита переноса, выход 69 переноса из старшего разряда вычислительного узла,

Рассмотрим функциональное назначение л реализацию основных узлов и блоков

0 устройства для деления,

Каждый из узлов 1-f-1m предназначен для вычисления в соответствии с алгоритмом деления без восстановления остатков соотвлствующего остатка в виде двух чи5 сел: первого числа, составленного из поразрядных сумм, и второго числа, составленного из поразрядных переносов (сумма этих двух чисел равна остатку). Входной информацией для каждого из узлов 1ч

0 1m являются три числа. Первое число - делитель, второе и третье представляют собой совокупность разрядов функций соответственно генерации и транзита переноса соответствующего остатка (для первого узла

5 второе число является нулем, а третье число - делимым) с присоединенными младшими разрядами, поступающими с первого 5 и второго 6 входов делимого устройства. Фактически в каждом из узлов 12-1т из значе0 ния остатка, представленного в двухрядном коде совокупностью разрядов функций генерации и транзита переноса, вычитается (или прибавляется) значение делителя и образуется двухрядный код нового остатка.

5 Особенностью первого узла 1i является то, что на его входы второй и третьей групп может подаваться значение остатка с первого 8 и второго 9 выходов устройства в виде совокупности разрядов функций генерации ч транзита переноса при многократном использовании устройства в процессе выпол- нения операции деления (это тот случай, когда количество одновременно формируемых разрядов частного m меньше полной разрядности требуемого частного).

Одной из возможных реализаций узлов 1i-1m является их построение в виде совокупности знаковых 17 и вычислительных 18 ячеек (фиг. 2, 3 и 4), между которыми отсутствуют переносы.

Узлы 2t -2m для каждого разряда определяют значения функций генерации и транзита переноса по значению разрядной суммы и значению поступившего в данный разряд переноса. Они могут быть реализованы в виде совокупности ячеек 19 (фиг. 2 и 5).

Узел 3 по значениям функций генерации и транзита переноса, вырабатываемых соответствующим узлом 2, вычисляет значение переноса из старшего разряда узла 1. Функция, реализуемая узлом 3, определяется выражением

Р GM +TMG0 + TMToG 1 +TMT0TiG2 +

++ TMT0TiT2Т„-1См

где Gk. Tk - функция соответственно генерации и.транзита переноса к-го разряда остатка (k 0,1,2,...m; rn - количество числовых разрядов делителя);

GM, Тм - функции соответственно генерации и транзита переноса модифицированного знакового разряда.

Для одной из возможных реализаций устройства (фиг. 2) узлы переноса из старшего разряда узла 1 i-1m могут быть построены так, как это показано на фиг. 6.

Опишем работу устройства для деления на примере его реализации, изображенной на фиг. 2.

На вход 4 делителя устройства подается значение четырех разрядов положительного делителя 0: Ci €2 Сз СА, на первый вход 5 делимого устройства поступают нули, а на второй вход 6 делимого устройства - значение восьми разрядов положительного делимого с модифицированным знаковым разрядом ам а0; ai аг asa asaeayae.

В случае поступления делимого в виде совокупности разрядов функций генерации и транзита переноса, что возможно, например, при многократном использовании устройства, разряды функции генерации переноса должны подаваться на первый вход 5 делимого, а разряды функции транзита переноса - на второй вход б делимого устройства.

Первый узел 1i производит вычитание из значения старших четырех разрядов делимого значения четырех разрядов делителя. Настройка этого узла на вычитание (т. е.

на прибавление к старшим четырем разрядам делимого дополнительного кода ДРЛИ- теля) осуществляется уровнем логической 1, поступающим с входа 10 уровня логиче- 5 ской 1 устройства, который инвертирует все разряды делителя и подается на вход 49 переноса самой младшей ячейки 19 первого узла 21. Первый узел 2i формирует функции генерации G и транзита Т переноса по зна0 чениям сумм и переносов двух знаковых ячеек 17 и четырех вычислительных ячеек 18 первого узла 1ч. На выходе 1 первого узла 3i (ячейка 20) вырабатывается перенос Р из старшего разряда узла 11 согласно выраже5 нию

Р GM + TMGo + TMT0Gi + TMT0TiG2 + + TMT0TiT2G3 + TMT0TiT2T3G4

Значение переноса на выходе 7i является старшим разрядом частного q0, который

0 равен 1, если значение старших четырех разрядов делимого больше либо равно значению делителя, или равен 0 в противном случае.

Далее действия, производимые в(|-1)-м

5 узле 2j-i функций генерации и транзита переноса и J-м узлом 1j (, 3, 4, 5), соответствуют действиям, производимым во время очередного J-ro цикла обычного деления без восстановления остатка: если (0), то

0 делитель вычитается (прибавляется) из (J-1)- го остатка, образуемого в виде разрядов сумм и переносов на выходах (J- 1)-го узла 1j-i. Узел 2s вырабатывает значения разрядов функций генерации и транзита перено5 са, которые участвуют в определении последнего (младшего) разряда частного, а также подаются на выходы 8 и 9 остатка устройства.

0 Формулаизобретения

Устройство для деления, содержащее m вычислительных узлов (т - число формируемых цифр частного), m узлов формирования функций генерации и транзита

5 переноса, причем вход делителя устройства соединен с входами первой группы 1-го вычислительного узла , 2т), выходы переносов и сумм которого соединены cs входами первой и второй групп соответст0 венно 1-го узла формирования функции генерации и транзита переноса, первый и второй входы соответствующих разрядов делимого устройства соединены с входами второй и третьей групп соответственно пер-

5 вого вычислительного узла, вход настройки которого соединен с входом логической 1 устройства, входы старших разрядов второй и третьей групп j-ro вычислительного узла

, 3т) соединены с выходами младших

разрядов первой и второй групп соответственно (J-1}-ro узла формирования функций генерации и транзита переноса, входы младших разрядов втброй и третьей групп j-ro вычислительного узла соединены с входами соответствующих разрядов первого и второго входов делимого устройства, выходы младших разрядов первой и второй групп m-ro узла формирования функций генерации и транзита переноса соединены с первым и вторым выходами соответственно остатка устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит m узлов формирования переноса из старшего разряда, причем выходы

Ч

7ff

0

первой группы и старших разрядов второй группы 1-го узла формирования функций генерации и транзита переноса соединены с входами первой и второй групп 1-го узла формирования переноса из старшего разряда соответственно, вход настройки j-ro вычислительного узла соединен с выходом (j-1)-ro узла формирования переноса из старшего разряда и с выходом (jH)-ro разряда частного устройства, выход m-ro узла формирования переноса из старшего разряда соединен с выходом m-ro разряда частного устройства.

фиг 2

ъ-60

Ј

47

4/

i-{

гю

iT

j

/#г

fej

У j

,J/

4/

47

17

№

фигЛ

f i

-. ,

50

фиг. 5

i

Ј /

-т

49

51

| Карцев М | |||

| А., Брик В | |||

| А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.; Радио и связь, 1981, с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для деления | 1988 |

|

SU1594527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-07—Публикация

1989-03-06—Подача