где L V/Pr, h - шаг сеточной области, блоки конечно-разностной модели, процессоры S.-Sj,,, . Это позволяет разбить исходную задачу на ряд подзадач по расчету поля, выполняемых параллельно со смещением во времени в блоках конечно-разностной модели, что позволяет достигнуть цель изобретения. 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1310839A1 |

| Матричный процессор | 1985 |

|

SU1354204A1 |

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1348854A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Матричный процессор | 1987 |

|

SU1534466A1 |

| Устройство для сопряжения | 1990 |

|

SU1753478A1 |

| АССОЦИАТИВНЫЙ КОММУТАТОР | 1991 |

|

RU2101760C1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Ассоциативный матричный процессор | 1990 |

|

SU1795467A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

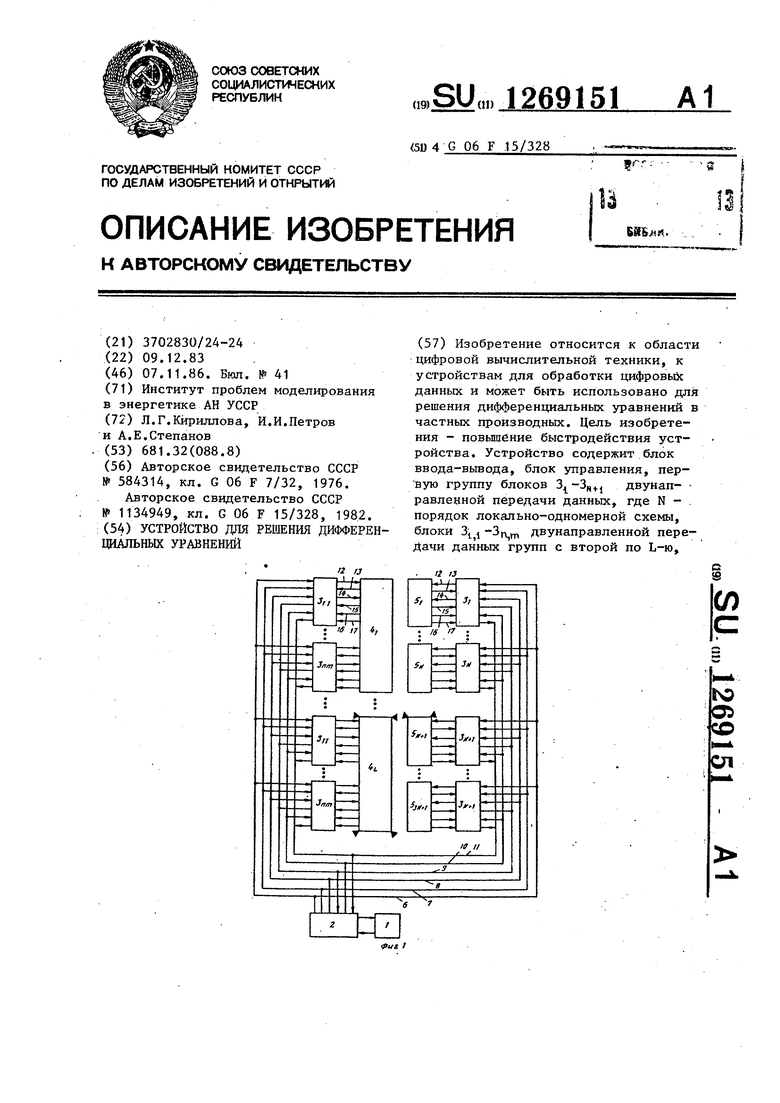

Изобретение относится к области цифровой вычислительной техники, к устройствам для обработки цифровьйс данных и может быть использовано для решения дифференциальных уравнений в частных производных. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок ввода-вьтода, блок управления, первую группу блоков двунап- равленной передачи данных, где N - . порядок локально-одномерной схемы, блоки 3 3|л,ц1 двунаправленной передачи данных групп с второй по L-ю,

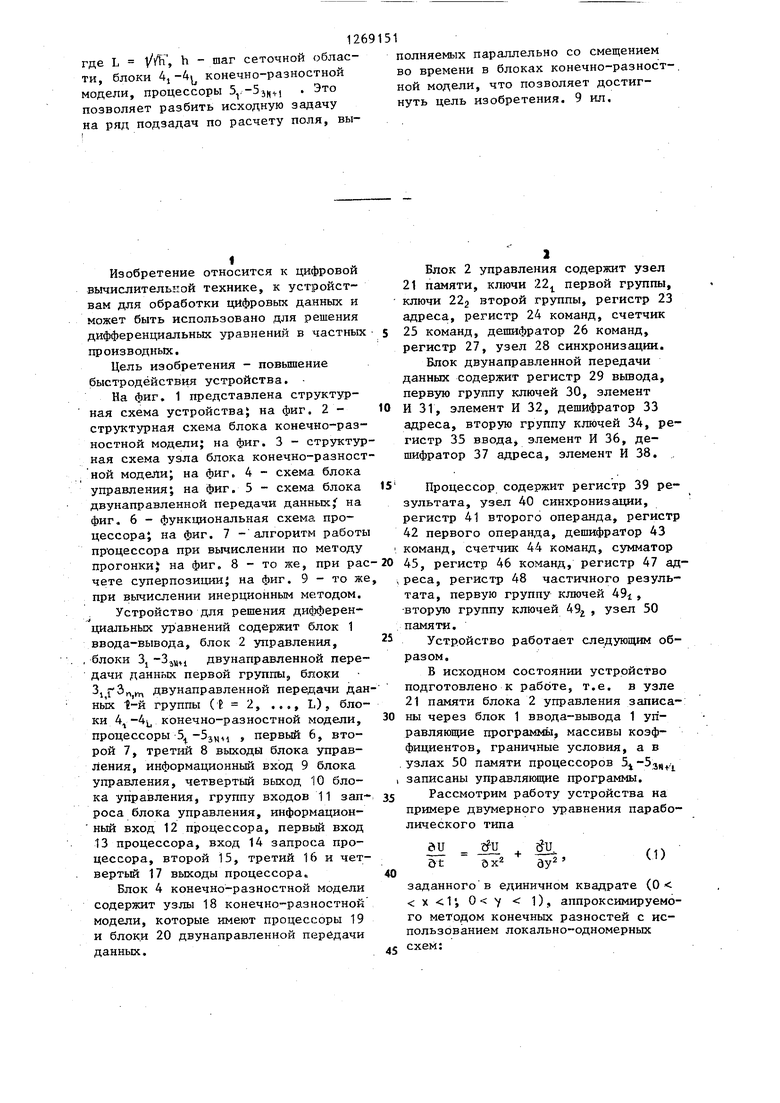

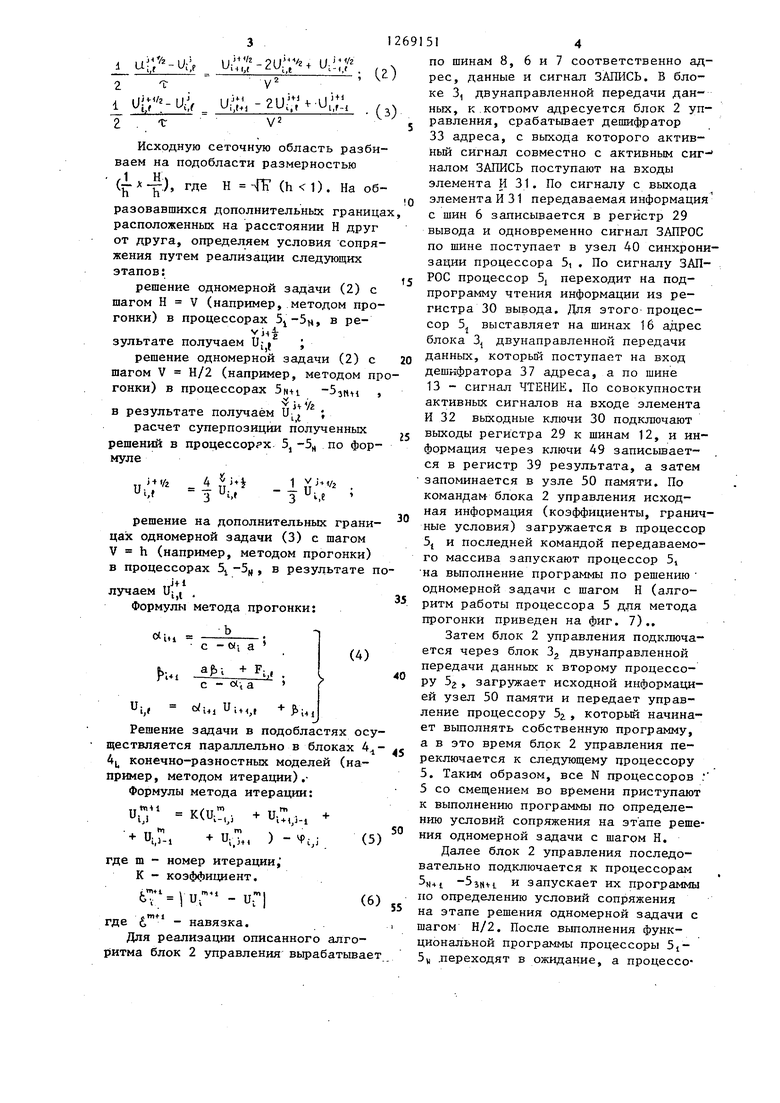

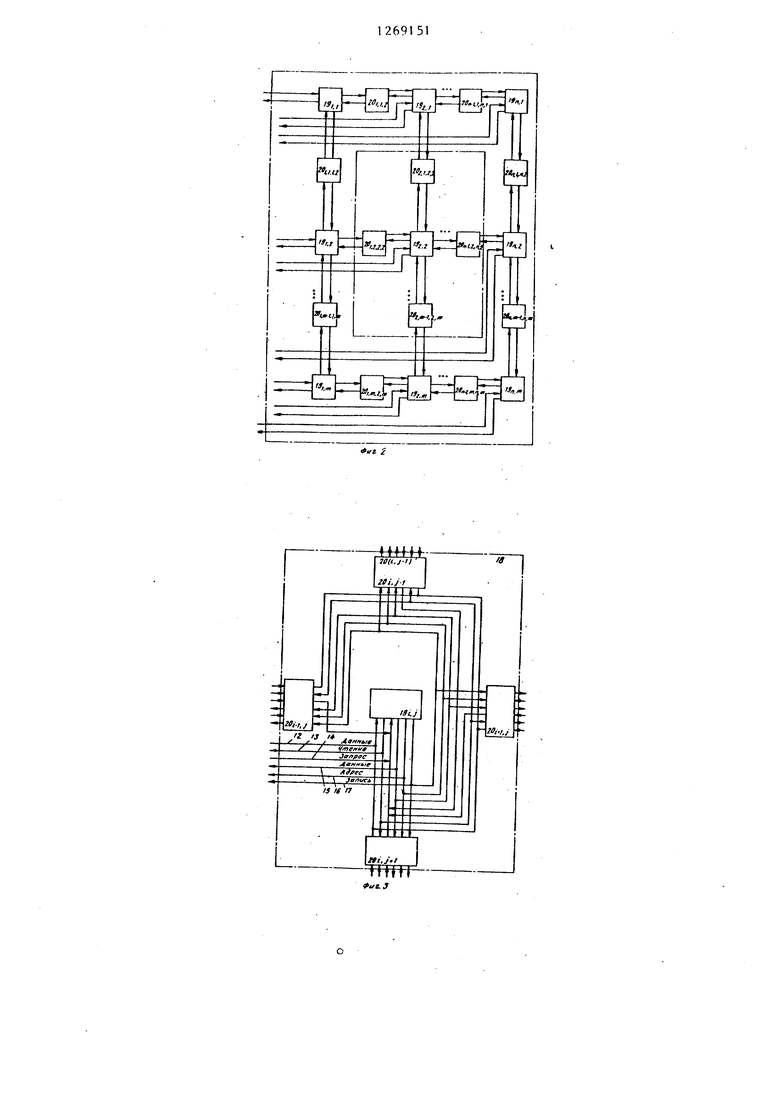

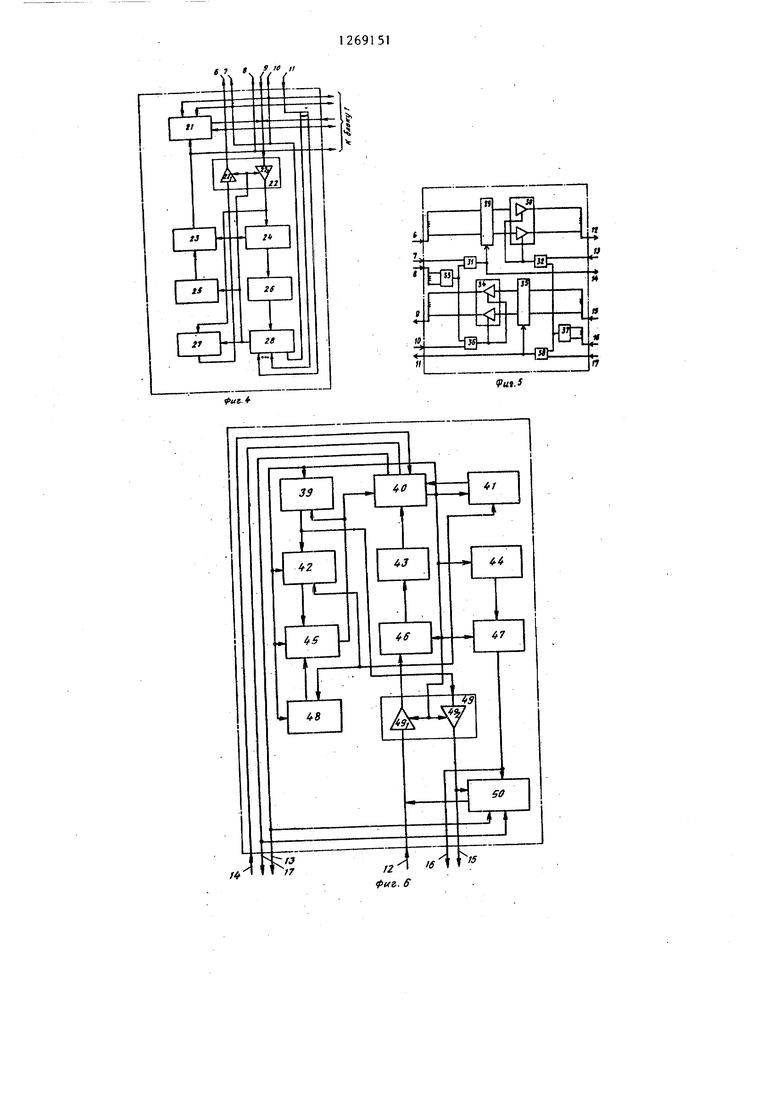

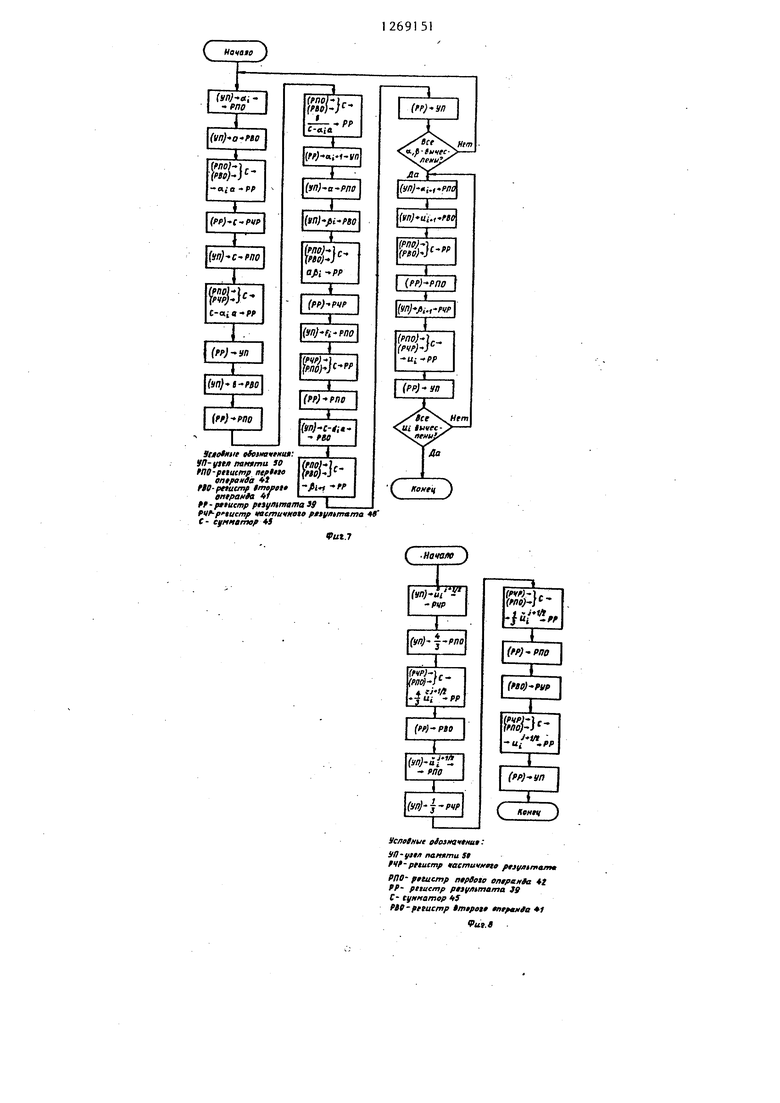

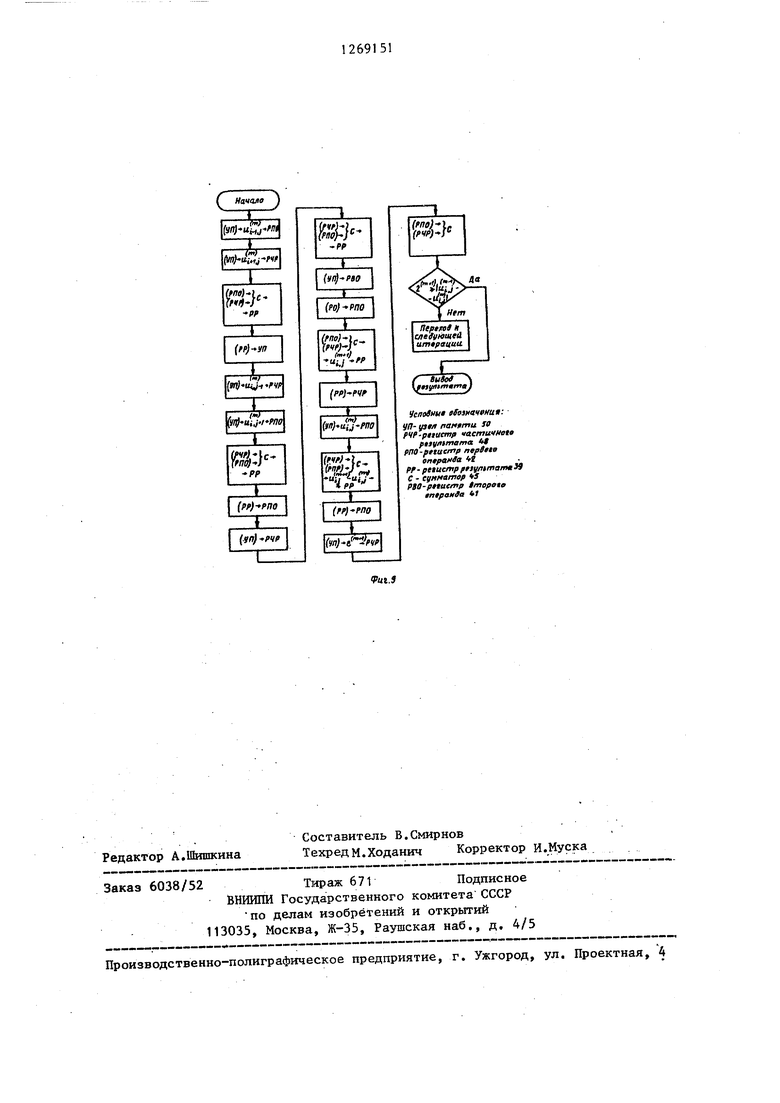

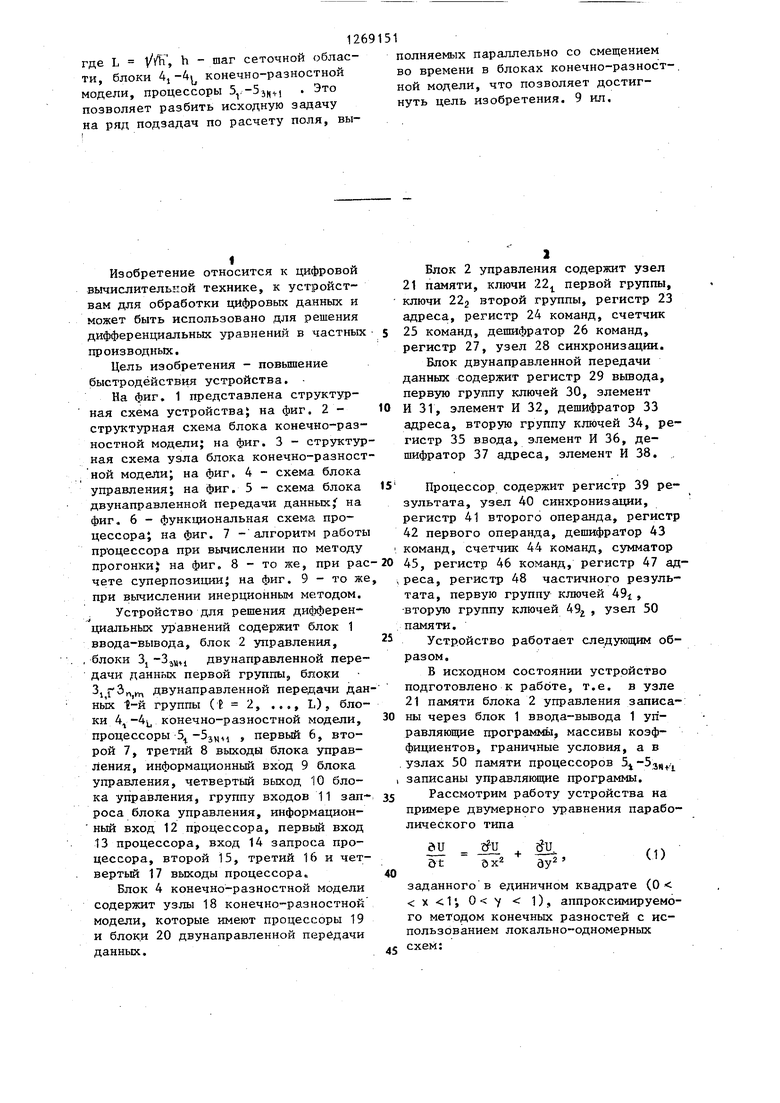

Изобретение относится к цифровой вычислительной технике, к устройствам для обработки цифровых данных и может быть использовано для решения дифференциальных уравнений в частных производных. Цель изобретения - повышение быстродействия устройства. На фиг. 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока конечно-разностной модели; на фиг. 3 - структур ная схема узла блока конечно-разност ной модели; на фиг. 4 - схема блока управления; на фиг. 5 - схема блока двунаправленной передачи данных на фиг« 6 - функциональная схемз процессора; на фиг. 7 - алгоритм работы процессора при вычислении по методу прогонкиJ на фиг. 8 - то же, при рас чете суперпозиции; на фиг. 9 - то же при вычислении инерционным методом. Устройство для решения ди оференциальных уравнений содержит блок 1 ввода-вывода, блок 2 управления, блоки 3j -3j,,ti двунаправленной передачи данных первой группы, блоки ,,т двунаправленной передачи дан ньк t-й группы (, ..., L), блоки 4 -4j конечно-разностной модели, процессоры 5 -5змм , первый 6, второй 7, третий 8 выходы блока управления, информационный вход 9 блока управления, четвертый выход 10 блока управления, группу входов 11 запроса блока управления, информационный вход 12 процессора, первьй вход 13 процессора, вход 14 запроса процессора, второй 15, третий 16 и четвертьй 17 выходы процессора,, Блок 4 конечно-разностной модели содержит узлы 18 конечно-разностной модели, которые имеют процессоры 19 и блоки 20 двунаправленной передачи данных. Блок 2 управления содержит узел 21 памяти, ключи 22 первой группы, ключи 222 второй группы, регистр 23 адреса, регистр 24 команд, счетчик 25 команд, дешифратор 26 команд, регистр 27, узел 28 синхронизации. Блок двунаправленной передачи данных содержит регистр 29 вьшода, первую группу ключей 30, элемент И 31, элемент И 32, дешифратор 33 адреса, вторую группу ключей 34, регистр 35 ввода элемент И 36, дешифратор 37 адреса, элемент И 38. , Процессор содержит регистр 39 результата, узел 40 синхронизации, регистр 41 второго операнда, регистр 42 первого операнда, дешифратор 43 команд, счетчик 44 команд, сумматор 45, регистр 46 команд, регистр 47 адреса, регистр 48 частичного результата, первую группу ключей 49, вторую группу ключей 49 , узел 50 памяти. Устройство работает следующим образом. В исходном состоянии устройство подготовлено к работе, т.е. в узле 21 памяти блока 2 управления записа-: ны через блок 1 ввода-вывода 1 управляющие программы, массивы коэффициентов, граничные условия, а в узлах 50 памяти процессоров 5 , записаны управляющие программы. Рассмотрим работу устройства на примере двумерного уравнения параболического типа заданного в единичном квадрате (О X 1, О V 1) , аппроксимируемого методом конечных разностей с использованием локально-одномерных схем: Исходную сеточную область раз ваем на подобласти размерностью Н -fH (h 1). На разовавшихся дополнительных гран расположенных на расстоянии Н др от друга, определяем условия соп жения путем реализации следующих этапов: решение одномерной задачи (2) шагом Н V (например, методом п гонки) в процессорах , в ре VH зультате получаем U;( ; решение одномерной задачи (2) шагом V Н/2 (например, методом гонки) в процессорах 5м+1 -5зпи JV Уг В результате U- ; расчет суперпозиции полученны решений в процессорах по ф муле - iV . . - U;,, 3 . решение на дополнительных гра цах одномерной задачи (3) с шаго V h (например, методом прогонк в процессорах , в результат ,J+i лучаем . Формулы метода прогонки: с - W-1 а + F,,, , с - «ia 4,1 o/Ui U,i + fui Решение задачи в подобластях о ществляется параллельно в блоках AI конечно-разностных моделей (на пример, методом итерации),Формулы метода итерации: С к(м ,:,ь. Ci . ) . где m - номер итерации, К - коэффициент. ьГ ГиГ-иГ где , - навязка. Для реализации описанного алго ритма блок 2 управления вырабатыв 514 по шинам 8, 6 и 7 соответственно адрес, данные и сигнал ЗАПИСЬ, В блоке 3, двунаправленной передачи данных, к KOTDOMV адресуется блок 2 управления, срабатьшает дешифратор 33 адреса, с выхода которого активньш сигнал совместно с активным сиг- налом ЗАПИСЬ поступают на входы элемента И 31, По сигналу с выхода элемента И 31 передаваемая информация с шин 6 записывается в регистр 29 вывода и одновременно сигнал ЗАПРОС по шине поступает в узел 40 синхронизации процессора 5, , По сигналу ЗАПРОС процессор 5j переходит на подпрограмму чтения информации из регистра 30 вывода. Для этого-процессор 5. выставляет на шинах 16 адрес блока 3 двунаправленной передачи данных, который поступает на вход дешифратора 37 адреса, а по шине 13 - сигнал ЧТЕНИЕ. По совокупности активньйс сигналов на входе элемента И 32 выходные ключи 30 подключают выходы регистра 29 к шинам 12, и информация через ключи 49 записьшает- , ся в регистр 39 результата, а затем запоминается в узле 50 памяти. По командам блока 2 управления исходная информация (коэффициенты, граничные условия) загружается в процессор 5 и последней командой передаваемого массива запускают процессор 5i на выполнение программы по решению одномерной задачи с шагом Н (алгоритм работы процессора 5 для метода прогонки приведен на фиг, 7)., Затем блок 2 управления подключается через блок 3 двунаправленной передачи данных к второму процессору 52 , загрзгжает исходной информацией узел 50 памяти и передает управление процессору 52. , который начинает выполнять собственную программу, а в это время блок 2 управления переключается к следующему процессору 5, Таким образом, все N процессоров . 5 со смещением во времени приступают к выполнению программы по определению условий сопряжения на этапе решения одномерной задачи с шагом Н. Далее блок 2 управления последовательно подключается к процессорам N41 5iHti и запускает их программы по определению условий сопряжения на этапе решения одномерной задачи с шагом Н/2. После выполнения функциональной программы процессоры 5i5 .переходят в ожидание, а процессозаканчивают выполнение функциональных программ в соответствии с алгоритмом, приведенным на фиг. 7. После того, как выполнено вычис ление в любом из процессоров Зщч -5j,(,j и определено значение поля с шагом Н/2, процессор 5 сообщает об этом блоку 2 управления. Для это го процессор 5 выставляет на шинах 16адрес блока 3 двунаправленной передачи данных, на шинах 15 данные для передачи в блок 2, а на шине 17- активный сигнал ЗАПИСЬ. По совокупности этих сигналов блок 3 дву направленной передачи данных {фиг,5 принимает информацию в регистр 35 и далее управляющим сигналом ЗАПРОС п шине 11 передает управление блоку 2 Подпрограмма чтения включает вьщачу по шинам 8 адрес блока 3 двунаправленной, передачи данных, который пос тупает на вход дешифратора 33 адреса, и управляющего сигнала ЧТЕНИЕ по шине 10. По активному сигнапу с выхода элемента И 36 информация с регистра 35 через ключи 34 поступае по информационным шинам 9 через буфер ввода-вывода в регистр 27 блока 2, а затем записывается в узел 21 памяти. Далее, таким образом, прини маются остальные слова полученного массива из процессора 5 в блок 2 управления. ; Аналогично после завершения вычислений каждьш из процессоров 5н1-1 последовательно, передает полученные значения функций в блок 2 управления, который пересьшает эти значения через блоки двунаправленной передачи данных в процессоры 5|-5tj для расчета суперпозиции полученных решений с шагом Н и Н/2 согласно алгоритму, приведе ному на фиг. 8. Результат вычисления суперпозиции (используется процессорами 5 -5н для расчета одномерных задач с шагом h) из процессоров 5 -5 через блоки 3j -3ц .двунаправленной передачи данных пос ледовательно передается в узел 21 .памяти блока 2 управления, который через блоки 3n,m двунаправле ной передачи данных последовательно пересыпает значения на дополнительньк границах в блоки 4 -4j конечноразностных моделей, где осуществляется расчет поля итерационным мето516ом по алгоритму, приведенному на фиг, 9с Результат расчета поля из процессоров 19 пересылается в блок 2 управления для вывода в блок 1. Формула изобретения Устройство для решения дифференциальных уравнений, содержащее 3N процессоров, где N - порядок локально-одномерной схемы, с первого по ЗМ-й блоки двунаправленной передачи данных первой группы, с второй по (Ь+1)-ю группы по mn блоков двунаправленной передачи данных в каждой группе, где L , п , m , h - шаг сеточной области, блок управления, блок ввода-вьшода, первые информационные входы блока двунаправленной передачи данных с первой по (L + 1)-ю группы подключены к первому выкоду блока управления, первые входы записи блоков двунаправленной передачи данных групп с первой по (I, + 1)-ю подключены к второму выходу блока управления, первые адресные входы блоков двунаправленной передачи данных групп с первой по (L + 1)-ю подключенык третьему выходу блока управления, первые входы чтения блоков двунаправленной передачи данных групп с первой по (L + 1)-ю подключены к четвертому выходу блока управления, группа информационных входов блока управления подключена к первым выходам блоков двунаправленной передачи данных групп с первой по (L + 1)-ю, группа входов запросов блока управления подключена к вторым выходам блоков двунаправленной передачи данных групп с первой по (L + 1)-ю, первый выход х-го блока двунаправленной передачи данных первой группы (i 1, ..., 3N) подключен к информационному входу i-ro процессора, второй выход i-ro блока двунаправленной .передачи данных первой группы подключен к входу запроса i-ro процессора, информационные выходы с первого по четвертый i-ro процессора подключены соответственно к второму входу чтения, к второму информационному входу, второму адресному входу и к второму входу записи i-ro блока двунаправленной передачи данных первой группы, при блок управления содержит узел памяти, регистр адреса, регистр команд, счетчик команд.

дешифратор, регистр и узел синхронизации, выход регистра адреса подключен к адресному входу узла памяти, к третьему и пятому выходам блока управления, первьй выход узла синхронизации подключен к входу считывания регистра, счетному входу счетчика команд, входам считывания регистра команд и регистра адреса, второй выход узла синхронизации под ключей к второму выходу блока управ.лeнияjl выход регистра команд подключен к входу дешифратора, выход которого подключен к входу запуска узла синхронизации, выход счетчика команд подключен к информационному входу регистра адреса, вход задания режим узла синхронизации подключен к группе входов запросов блока управления отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введены L матриц размером пх m каждая процессоров и L матриц размером пхш каждая блоков двзнаправленной передачи данных, первый информационный выход процессора j -и строки (,...,m) k-ro столбца (k 1, ... n) f-й матрицы процессоров (f 2, ..., L + 1) подключен к вторым входам чтения блока двунаправленной передачи данных j-й строки k-ro столбца, блока двунаправленной передачи данных j-й строки (k + 1)-го столбца, блоки двунаправленной передачи данных (j-1)-й строки k-ro столбца, блока двунаправленной передачи данных (+1)-й строки k-ro столбца 1-й матрицы блоков двунаправленной передачи данных и к второму входу чтения (j-1)m + + k-ro блока двунаправленной передачи данных 1-й группы, второй информационный выход процессора j-й строки k-ro столбца 1-й матрицы процессоров подключен к вторым информационным входам блока двунаправленной передачи данных j-й строки k-ro столбца, блока двунаправленной передачи данных j-й строки (k+1)-ro столбца, блока двунаправленной передачи данных (j - 1)-й строки k-ro столбца, блока двунаправленной передачи данных (j + 1)-й строки k-ro столбца f-й матрицы блоков двунаправленной передачи данных и к второму информационному входу (j - 1)m + + k-ro блока двунаправленной передачи данных 6-й группы, третий инфор691518

мационный вход процессора j-й строки k-ro столбца f-й матрицы процессоров подключен к вторым адресным входам блока двунаправленной передачи дан5 Hbtx j-й строки k-ro столбца, блока двунаправленной передачи данных j-й строки (k + 1)-го столбца, блока двунаправленной передачи данных (j -1)-й строки k-ro столбца, блока

10 двунаправленной передачи данных (j + + 1)-й строки k-ro столбца Е-Й матрицы блоков двунаправленной передачи данных и к второму адресному входу (j - 1)m + k-ro блока двунаправлен15 ной передачи данных Е-й группы, четвертый информационный выход процессора j-й строки k-ro столбца матрицы процессоров подключен к вторым входам записи блока двунаправленной

20 передачи данных j-й строки k-ro столбца, блока двунаправленной передачи данных j-й строки (.R + столбца, блока двунаправленной передачи данных (j - 1)-й строки k-ro столбца,

25 блока двунаправленной передачи данных (j + 1)-й строки k-ro столбца -й матрицы блоков двунаправленной передачи данных и к второму входу записи (j - l)m + k-ro блока двунап0 равленной передачи данных С-й группы, информационный вход процессора j-й строки столбца t-й матрицы процессоров подключен к первым вы- ходам блока двунаправленной передачи

5 данных j-й строки k-ro столбца блока двунаправленной передачи данных j-й строки (k + 1)-го столбца, блока двунаправленной передачи данных (j -1)-и строки k-ro столбца, блока

0 двунаправленной передачи данных (j + + 1)-и строки k-ro столбца 1-й матрицы блоков двунаправленной передачи данных и к первому выходу (j -1)m + k-ro блока двунаправленной 5 передачи данных Е-й группы, вход

запроса процессора j-й строки k-го столбца t-й матрицы процессоров подключен к вторым выходам, блока двунаправленной передачи данных j-й стро0 ки k-ro столбца, блока двунаправленной передачи данных j-й строки (k + + 1)-го столбца, блока двунаправленной передачи данных (j - 1)-й строки k-ro столбца,блока двунаправленной

5 передачи данных (j-1)-й строки k-ro столбца 1-й матрицы блоков двунаправленной передачи данных и к второму выходу (j-1)m+k-го блока двунаправленной пе- 9 редачи данных t-й группы,третий информационный вход блока двунаправленной передачи данных j-й строки k-ro столбца t-й матрицы блоков двунаправ ленной передачи данных подключен к вторым информационным выходам процессора j-й строки (k-l)-ro столбца, процессора (j - 1)-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца t-й матрицы процессоров, первый вход записи блока двунап равленной передачи данных j-й строки k-ro столбца t-й матрицы блоков двунаправленной передачи данных подключен к четвертым информационным вы ходам процессора j-й строки (k-l)-ro столбца, процессора (j -1)-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца f-й матрицы процессоров, первьй адресный вход блока двунаправленной передачи данных j-й строки.k-ro столбца t-й матри11;ы бло.ков двунаправленной передачи данных подключен к третьим информационным выходам процессора j-й строки (k -1)-го столбца, процессо1 а (j-1)-й строки k-ro столбца, процессора ( 1)-й строки k-ro столбца Р-й матри -цы процессоров,первый вход чтения блока двунаправленной передачи данньк j-й строки k-столбца -й матрицы блоков двунаправленной передачи данных подключен к первым информационным выхбдам процессора j-й строки (k - 1)-го столбца, процессора (j -.1)-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца Р-й матрицы процессоров,третий выход блока двунаправленной передачи данных j-й строки k-ro столбца f-й матри1№1 блоков двунаправленной передачи данных подключен к информационным входам процессора j-й строки - 1)-го столбца, процессора (j-1)-й строки k-ro столбца, процессора (j + 1)-й строки k-ro столбца f-й матрицы процессоро)з, четвертый выход блока двунаправленной передачи данных j-й строки k-ro столбца -й матрицы блоков двунаправленной передачи данных подключен к входам запроса процессора j-й строки (k - 1)-го столбца, процессора (j - 1)-й строки k-ro столбца, процессора (j + + 1)-й строки Н-го столбца f-й матрицы процессоров,при этом шестой, седьмой и восьмой выходы блока управления подключены соответственно к первому, второму и третьему входам блока ввода-вьшода, вход начальных значений блока управления подключен к выходу блока ввода-вывода, при этом в блок управления дополнительно введены первая и вторая группы ключей, информационный вход ключей первой группы подключен к выходу регистра, информационный вход ключей второй группы подключен к выходу узла цамяти, информационному входу блока управления и к входу начальных значений блока управления, выход ключей первой группы подключен к первому и восьмому выходам блока управления и к информационному входу узла памяти, выход ключей второй группы подключен к информационным входам регистра команд и регистра, управляющий вход ключей первой и второй групп подключен к первому выходу узла синхронизации, вход чтения, вход записи узла памяти, а также второй, четвертый, шестой и седьмой выходы блока управления подключены к второму выходу узла синхронизации.

- , S If II

Л N // /

ri

.t

iPut.f

llcnftMui ftpiHanmu :

У11-уг л

f4f-i ftucmf mcmuwne ffiyatmam

РПО- ftiucmp ntftoia entpatita 4/ tt- fttacmp ptiff/nmama 38 C- tj/HHamep J nt-frtucmp tmffttf tntfoiiia 1

Vui.e

| Устройство для решения уравнения математической физики | 1976 |

|

SU584314A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| i | |||

Авторы

Даты

1986-11-07—Публикация

1983-12-09—Подача