Изобретение относится к электроизмерительной технике,в частности к электроизмерительным приборам, имеющим нелинейную передаточную характеристику

Цель изобретения - расширение обла- сти использования устройства.

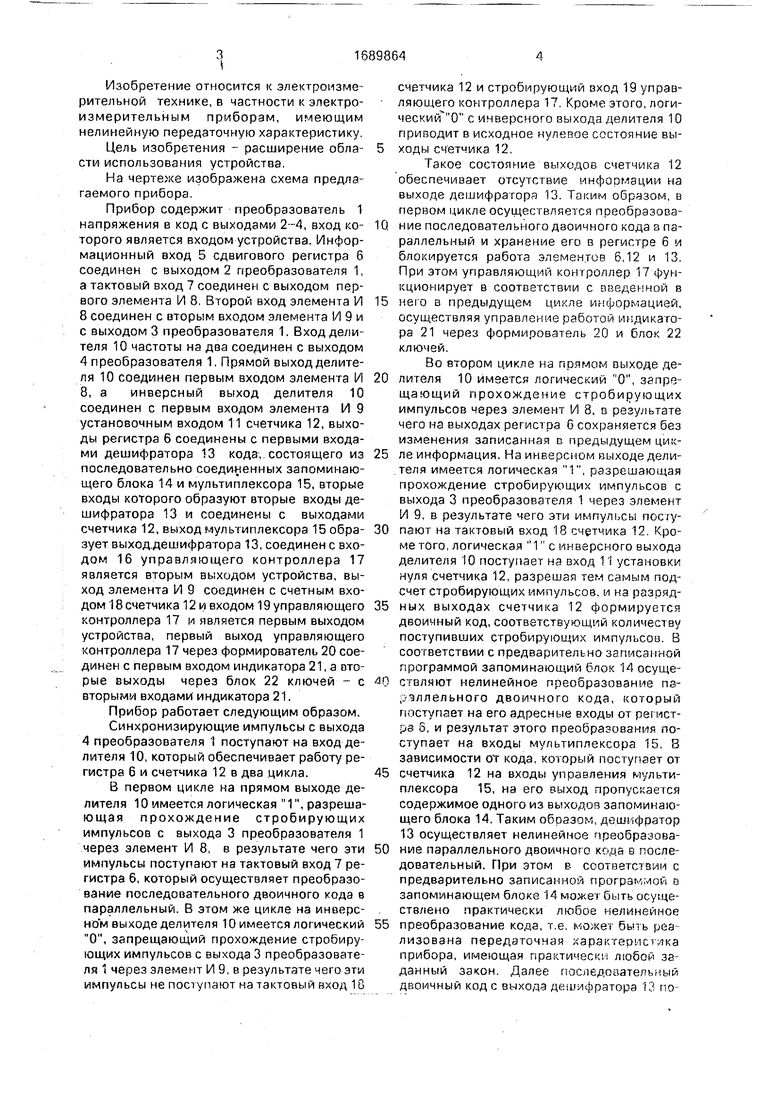

На чертеже изображена схема предлагаемого прибора

Прибор содержит преобразователь 1 напряжения в код с выходами 2-4, вход ко- торого является входом устройства. Информационный вход 5 сдвигового регистра 6 соединен с выходом 2 преобразователя 1, а тактовый вход 7 соединен с выходом первого элемента И 8 Второй вход элемента И 8 соединен с вторым входом элемента И 9 и с выходом 3 преобразователя 1. Вход делителя 10 частоты на два соединен с выходом 4 преобразователя 1. Прямой выход делителя 10 соединен первым входом элемента И 8, а инверсный выход делителя 10 соединен с первым входом элемента И 9 установочным входом 11 счетчика 12, выходы регистра 6 соединены с первыми входами дешифратора 13 кода, состоящего из последовательно соединенных запоминающего блока 14 и мультиплексора 15, вторые входы которого образуют вторые входы дешифратора 13 и соединены с выходами счетчика 12, выход мультиплексора 15 обра- зует выход дешифратора 13, соединен с входом 16 управляющего контроллера 17 является вторым выходом устройства, выход элемента И 9 соединен с счетным входом 18 счетчика 12 и входом 19 управляющего контроллера 17 и явпяется первым выходом устройства, первый выход управляющего контроллера 17 через формирователь 20 соединен с первым входом индикатора 21, а вторые выходы через блок 22 ключей - с вторыми входами индикатора 21.

Прибор работает следующим образом. Синхронизирующие импульсы с выхода 4 преобразователя I поступают на вход делителя 10, который обеспечивает работу регистра 6 и счетчика 12 в два цикла.

В первом цикле на прямом выходе делителя 10 имеется логическая 1, разрешающая прохождение стробирующих импульсов с выхода 3 преобразователя 1 через элемент И 8, в результате чего эти импульсы поступают на тактовый вход 7 регистра 6, который осуществляет преобразование последовательного двоичного кода в параллельный. В этом же цикле на инверсном выходе делителя 10 имеется логический О, запрещающий прохождение стробирующих импульсов с выхода 3 преобразователя 1 через элемент И 9, в результате чего эти импульсы не пост упают на тактовый вход 1В

счетчика 12 и стробирующий вход 19 управляющего контроллера 17 Кроме этого, логи- ческий 0 с инверсного выхода делителя 10 приводит в исходное нулевое состояние выходы счет«ика 12

Такое состояние выходов счетчика 12 обеспечивает отсутствие инфоомации на выходе дешифрагоря 13 Таким образом, в первом цикле осуществляется поеобразова- ние последовательного двоичного кода з параллельный и хранение его в регистре 6 и блокируется работа элементов 6,12 и 13 При этом управляющий контроллер 17 функционирует в соответствии с введенной в него в предыдущем цикле информацией, осуществляя управление работой икдикаго- ра 21 через формирователь 20 и блок 22 ключей

Во втором цикпе на почмом выходе делителя 10 имеется логический О, запрещающий прохождение стробирующих импульсов иерез элемент И 8, в результате чего на выходах регист оа G сохраняется без изменения записанная в предыдущем цикле информация. На инверсном выходе делителя имеется логическая 1, разрешающая прохождение стробирующих импульсов с выхода 3 преобразователя 1 через элемент И 9, в результате чего эти импульсы поступают на тактовый вход 18 счетчика 12 Кроме тйго, логическая 1 с инверсного выхода делителя 10 поступает на вход 1 i установки нуля счетчика 12, разрешая тем самым подсчет стробирующих импульсов, и на разояд- ных выходах счетчика 12 формируется двоичный код, соответствующий количеству поступивших стробирующих импульсов В соответствии с предварительно записанной программой запоминающий блок 14 осуществляют нелинейное преобразование п,э- .„ эллельного двоичного кода, который поступает на его адресные входы от регистре 5, и результат этого преобразования поступает на входы мультиплексора 15, В зависимости от кода, который поступает от счетчика 12 на входы управления мультиплексора 15, на его выход пропускается содержимое одного из выходоч запоминающего блока 14. Таким обоазом, дешифратор 13 осуществляет нелинейное преобразование параллельного двоичного кола в последовательный. При этом в соответствии с предварительно записанной прогрзк мо в запоминающем блоке 14 может бить осуществлено практически любое нелинейное преобразование кода, т е к-южет бьпь pea лизована передагоччан характеристика прибора, имеющая практически любой заданный закон Далее последозатель ый двоичный код с выхода дешифратора I по

ступает на информационный вход 16 управляющего контроллера 17, на стробирующий вход 18 которого поступают стробирующие импульсы с выхода элемента И 9. Кроме того, выход элемента И 9 и дешифратора 13 образуют первый и второй выходы устрой- ства. В соответствии с поступившей дво- ичной информацией управляющий контроллер 17 через формирователь 20 и блок 22 осуществляет управление работой индикатора 21.

Формула изобретения

1. Электроизмерительный прибор, содержащий преобразователь напряжения в код, вход которого является входом прибора, газоразрядный индикатор, анод которого соединен с выходом формирователя анодного напряжения, а катоды соединены с выходами блока ключей, дешифратор ко- да, входы управления которого соединены с выходами счетчика, два элемента И и делитель частоты на два, прямой выход которого соединен с входом первого элемента И, отличающийся тем, что, с целью расширения области использования прибора, в него введены сдвиговый регистр и управляющий контроллер, первый и вторые

выходы которого соединены соответственно с входом формирователя анодного напряжения и входами блока ключей, выходы сдвигового регистра соединены с адресными входами дешифратора кода, выход которого соединен с информационным входом управляющего контроллера, стробирующий вход которого соединен с выходом второго элемента И и тактовым входом счетчика, установочный вход которого соединен с первым входом второго элемента И и инверсным выходом делителя частоты на два, вход которого соединен с третьим выходом преобразователя напряжения в код, второй выход которого соединен с вторыми входами первого и второго элементов И, а первый выход соединен с информационным входом сдвигового регистра, тактовый вход которого соединен с выходом первого элемента И.

2. Прибор по п.1, отличающийся тем, что дешифратор катода содержит запоминающий блок и мультиплексор, выход которого является выходом дешифратора кода, выходы запоминающего блока соединены с входами мультиплексора, входы управления которого и адресные входы запоминающего блока являются первыми и вторыми входами дешифратора кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

| Система управления многоканальнымэлЕКТРОпРиВОдОМ РОбОТА | 1979 |

|

SU805246A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

Авторы

Даты

1991-11-07—Публикация

1988-11-09—Подача