Изобретение относится к области электроизмерительной техники и может быть использовано для измерения девиации сопротивлений резистивных датчиков.

Цель изобретения - расширение функциональных возможностей преобразователя за счет возможности измерения девиации сопротивления.

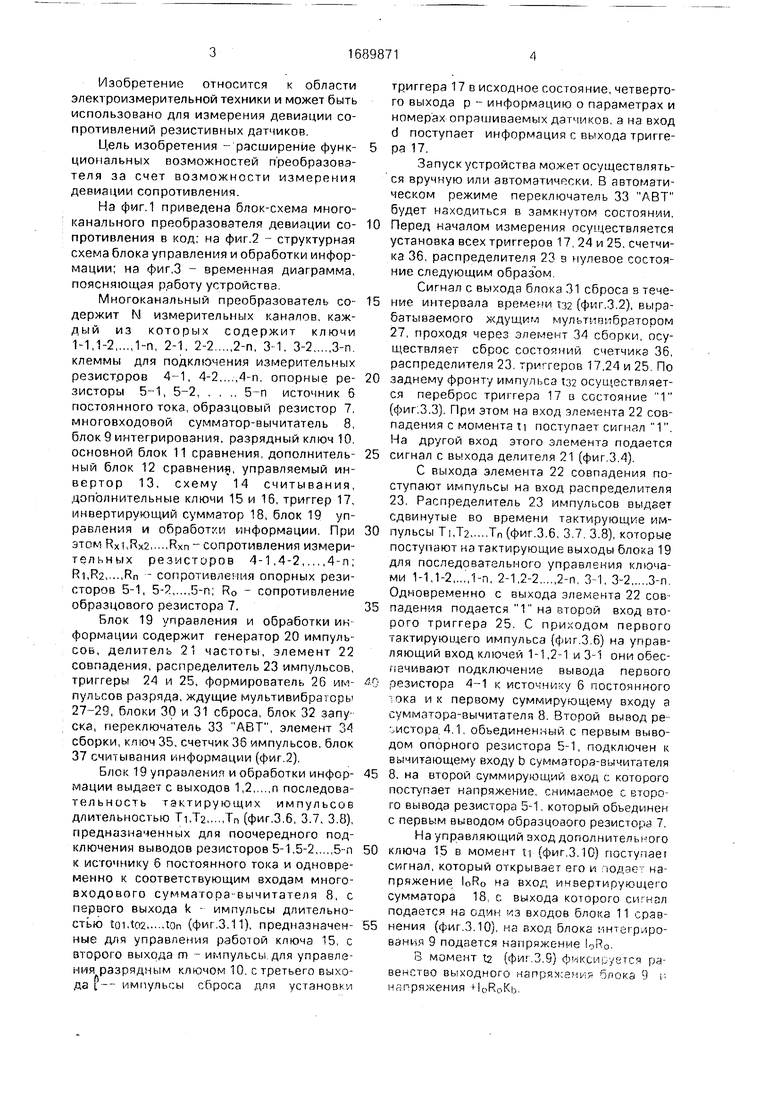

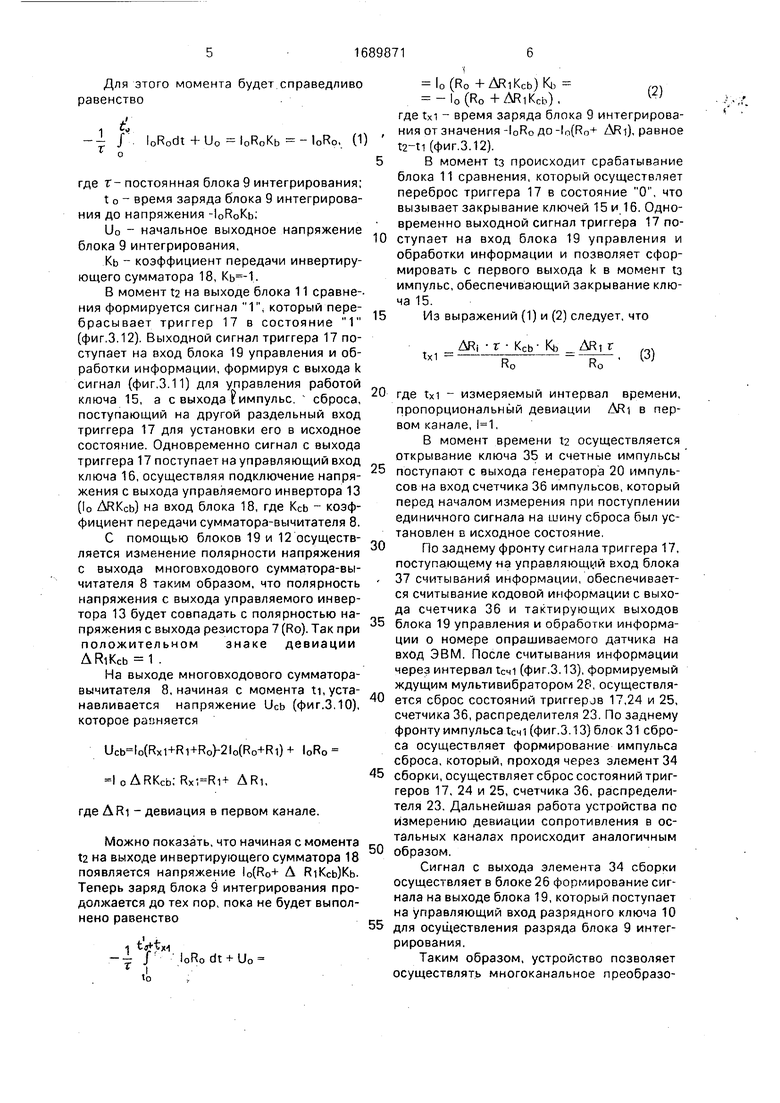

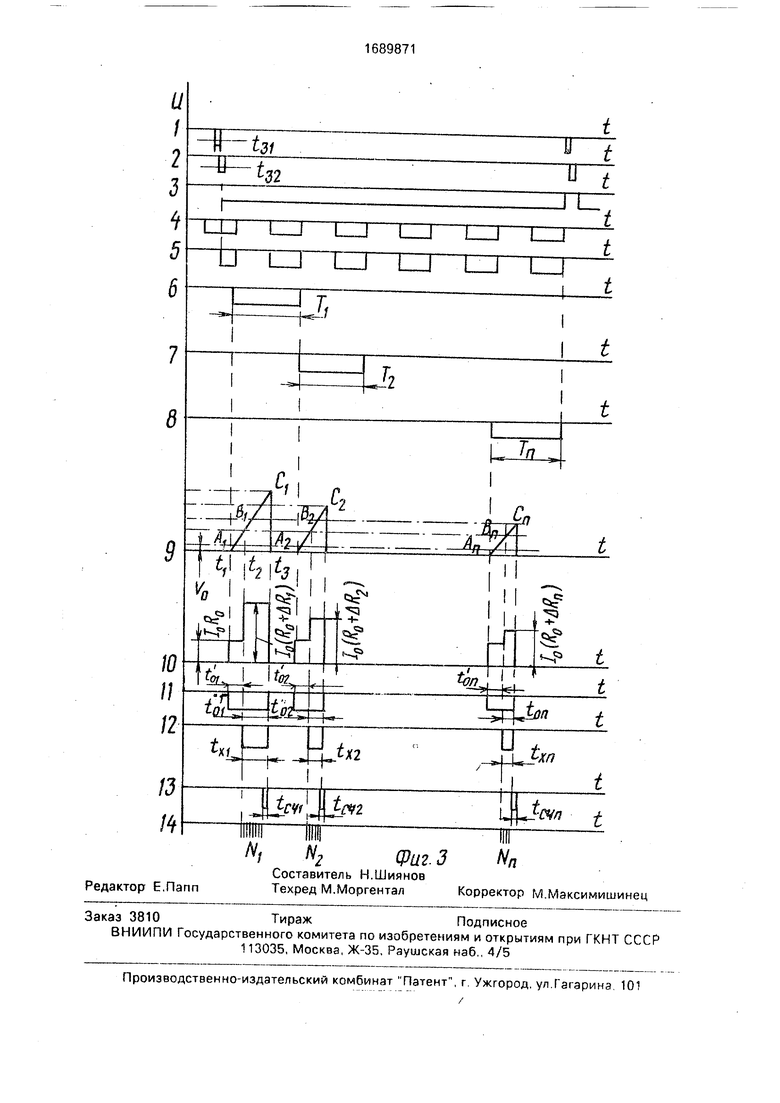

На фиг. 1 приведена блок-схема многоканального преобразователя девиации сопротивления в код; на фиг.2 - структурная схема блока управления и обработки информации; на фиг.З - временная диаграмма, поясняющая работу устройства.

Многоканальный преобразователь содержит N измерительных каналов, каждый из которых содержит ключи

1-1,1-21-п, 2-1, 2-22-п, 3-1. 3-23-п.

клеммы для подключения измерительных резисторов 4-1, 4-24-п, опорные резисторы 5-1, 5-2, . , ., 5-п источник 6 постоянного тока, образцовый резистор 7, многовходовой сумматор-вычитатель 8, блок 9 интегрирования, разрядный ключ 10. основной блок 11 сравнения, дополнительный блок 12 сравнения, управляемый инвертор 13, схему 14 считывания, дополнительные ключи 15 и 16, триггер 17, инвертирующий сумматор 18, блок 19 управления и обработки информации. При

этом Rxi,Rx2Rxn - сопротивления измерительных резисторов 4-1,4-2, ,.,,4-л; Ri.RaRn - сопротивления опорных резисторов 5-1, 5-25-n; RO - сопротивление

образцового резистора 7.

Блок 19 управления и обработки информации содержит генератор 20 импульсов, делитель 21 частоты, элемент 22 совпадения, распределитель 23 импульсов, триггеры 24 и 25, формирователь 26 импульсов разряда, ждущие мультивибраторы 27-29, блоки 30 и 31 сброса, блок 32 запуска, переключатель 33 АВТ, элемент 34 сборки, ключ 35, счетчик 36 импульсов, блок 37 считывания информации (фиг.2).

Блок 19 управления и обработки информации выдаете выходов 1,2п последовательность тактирующих импульсов

длительностью Ti,T2Тп (фиг.3.6, 3.7, 3.8),

предназначенных для поочередного подключения выводов резисторов 5-1,5-25-п

к источнику б постоянного тока и одновременно к соответствующим входам много- входового сумматора-вычитателя 8, с первого выхода k - импульсы длительностью toi.tozton (фиг.3.11), предназначенные для управления работой ключа 15, с второго выхода m - импульсы для управления разрядным ключом 10. с третьего выхода -- импульсы сброса для установим

триггера 17 в исходное состояние, четвертого выхода р - информацию о параметрах и номерах опрашиваемых датчиков, а на вход d поступает информация с выхода триггера 17.

Запуск устройства может осуществляться вручную или автоматически. В автоматическом режиме переключатель 33 АВТ будет находиться в замкнутом состоянии.

0 Перед началом измерения осуществляется установка всех триггеров 17, 24 и 25, счетчика 36, распределителя 23 з нулевое состояние следующим образом.

Сигнал с выхода блока 31 сброса в тече5 ние интервала времени тз2 (фиг.3.2), вырабатываемого ждущим мультивибратором 27, проходя через элемент 34 сборки, осуществляет сброс состояний счетчика 36, распределителя 23. триггеров 17,24 и 25. По

0 заднему фронту импульса t32 осуществляется переброс триггера 17 в состояние 1 (фиг .З.З). При этом на вход элемента 22 совпадения с момента ti поступает сигнал 1. На другой вход этого элемента подается

5 сигнал с выхода делителя 21 (фиг.3.4).

С выхода элемента 22 совпадения поступают импульсы на вход распределителя 23, Распределитель 23 импульсов выдает сдвинутые во времени тактирующие им0 пульсы Т|,ТзТп (фиг.3.6, 3.7, 3.8), которые

поступают на тактирующие выходы блока 19 для последовательного управления ключами 1-1,1-2,.,.,1-п, 2-1,2-22-п, 3-1. 3-23-п.

Одновременно с выхода элемента 22 сов5 падения подается 1 на второй вход второго триггера 25. С приходом первого тактирующего импульса (фиг.3.6) на управляющий вход ключей 1-1,2-1 и 3-1 они обеспечивают подключение вывода первого

-0 резистора 4-1 к источнику 6 постоянного ;ока и к первому суммируюа ему входу а сумматора-вычитателл 8. Второй вывод ре- оистора. 4.1, объединенный с первым выводом опорного резистора 5-1, подключен к вычитающему входу b суммагорэ-вычитателя

5 8, на второй суммирующий вход с которого поступает напряжение, снимаемое с второго вывода резистора 5-1, который объединен с первым выводом образцового резистора 7. На управляющий эход дополнительного

0 ключа 15 в момент ti (фиг.3.10) поступав сигнал, который открывает его и подает напряжение 0Ro на вход инвертирующего сумматора 18, с выхода которого сигнал подается на один ад входов блока 11 срав5 нения (фиг.3.10), на вход блока интегрирования 9 подается напряжение loR0.

3 момент 12 (фиг.3.9) фиксируется равенство выходного напряжения блока 9 ;; напряжения -HoRoKb.

Для этого момента будет справедливо равенство

.1

г J

loRodt +U0 loRoKb -loRo, О)

где т- постоянная блока 9 интегрирования;

to время заряда блока 9 интегрирования до напряжения -loRoKt ;

Do - начальное выходное напряжение блока 9 интегрирования,

Кь - коэффициент передачи инвертирующего сумматора 18, .

В момент t2 на выходе блока 11 сравнения формируется сигнал 1, который перебрасывает триггер 17 в состояние 1 (фиг.3.12). Выходной сигнал триггера 17 поступает на вход блока 19 управления и обработки информации, формируя с выхода k сигнал (фиг.3.11) для управления работой ключа 15, а с выхода импульс. сброса, поступающий на другой раздельный вход триггера 17 для установки его в исходное состояние. Одновременно сигнал с выхода триггера 17 поступает на управляющий вход ключа 16, осуществляя подключение напряжения с выхода управляемого инвертора 13 (lo ARKcb) на вход блока 18, где Ксь - коэффициент передачи сумматора-вычитателя 8.

С помощью блоков 19 и 12 осуществляется изменение полярности напряжения с выхода многовходового сумматора-вычитателя 8 таким образом, что полярность напряжения с выхода управляемого инвертора 13 будет совпадать с полярностью напряжения с выхода резистора 7 (Ro). Так при положительном знаке девиации ARiKcb 1 .

На выходе многовходового сумматора- вычитателя 8, начиная с момента ti.ycra- навливается напряжение Ucb (фиг.3.10), которое равняется

UcbH0(Rxi+Ri+Ro)-2lo(Ro+Ri) + loRo о ARKcD, + ARi, где ARi - девиация в первом канале.

Можно показать, что начиная с момента t2 на выходе инвертирующего сумматора 18 появляется напряжение 0(Ro+ A RiKct)Kb. Теперь заряд блока 9 интегрирования продолжается до тех пор, пока не будет выполнено равенство

1 taj-txl

- Г loRodt + U0

tb ,

(2)

0

lo(Ro +ARiKCb)Kb

-lo(Ro +ARiKcb), где txi время заряда блока 9 интегрирования от значения flo-ln(Ro+ ARi), равное t2-ti (фиг.3.12).

В момент t3 происходит срабатывание блока 11 сравнения, который осуществляет переброс триггера 17 в состояние О, что вызывает закрывание ключей 15 и 16. Одновременно выходной сигнал триггера 17 поступает на вход блока 19 управления и обработки информации и позволяет сформировать с первого выхода k в момент ta импульс, обеспечивающий закрывание ключа 15.

Из выражений (1) и (2) следует, что

ARj г Ксь- Кь ARi r

Rc

Re

(3)

г.

25

30

5

5

0

5

где txi измеряемый интервал времени, пропорциональный девиации ARi в первом канале, .

В момент времени t2 осуществляется открывание ключа 35 и счетные импульсы поступают с выхода генератора 20 импульсов на вход счетчика 36 импульсов, который перед началом измерения при поступлении единичного сигнала на шину сброса был установлен в исходное состояние.

По заднему фронту сигнала триггера 17, поступающему «а управляющий вход блока 37 считывания информации, обеспечивается считывание кодовой информации с выхода счетчика 36 и тактирующих выходов блока 19 управления и обработки информации о номере опрашиваемого датчика на вход ЭВМ. После считывания информации через интервал т,сч1 (фиг.3.13), формируемый ждущим мультивибратором 28, осуществляется сброс состояний триггера 17,24 и 25, счетчика 36, распределителя 23. По заднему фронту импульса Тсч1 (фиг.3.13)блок31 сброса осуществляет формирование импульса сброса, который, проходя через элемент 34 сборки, осуществляет сброс состояний триггеров 17, 24 и 25, счетчика 36, распределителя 23. Дальнейшая работа устройства по измерению девиации сопротивления в остальных каналах происходит аналогичным образом.

Сигнал с выхода элемента 34 сборки осуществляет в блоке 26 формирование сигнала на выходе блока 19, который поступает на управляющий вход разрядного ключа 10 для осуществления разряда блока 9 интегрирования.

Таким образом, устройство позволяет осуществлять многоканальное лреобразование девиации сопротивлений в код. Значение кода (фиг.3.14), зафиксированное при опросе первого канала, будет равно

Mi

N1 RoTa

(4)

где Тэ - период генератора 14.

Для n-го канала соответственно будем иметь

Nn

ARn t

RTfg

(5)

где Nn - число импульсоп в счетчике 36, пропорциональное девиации резистора 5-п.

После опроса n-го датчика по заднему фронту сигнала Тп (фиг.3.8) с выхода распределителя 19 осуществляется возврат триггера 25 в исходное состояние. Через интервал времени tat, вырабатываемый ждущим мультивибратором 27 при замкнутом положении переключателя 33 АВТ, осуществляется подача разрешающего сигнала на блок 32 запуска, который через блок 31 сброса в течение интервала времени t32 выполняет сброс состояний триггеров 17, 24 и 25, счетчика 36, распределителя 23.

По заднему фронту сигнала с выхода триггера 17, поступающему на управляющий вход схемы 14 считывания, обеспечивается считывание информации о знаке девиации AR с выхода S схемы 14 считывания.

Таким образом, устройство обладает более широкими функциональными возможностями за счет многоканальных измерений девиации сопротивления и может быть широко использовано в автоматизированных информационно-измерительных системах контроля и измерения параметров объекта,

Формула изобретения

Многоканальный преобразователь девиации сопротивления в код, содержащий источник постоянного тока, основной блок сравнения, блок интегрирования, блок управления и обработки информации, разрядный ключ, образцовый резистор, триггер, п измерительных каналов, каждый из которых содержит клеммы для подключения измеряемого резистора и два ключа, выход первого из которых соединен с входом второго и первой клеммой для подключения измеряемого резистора в каждом канале, входы первых ключей подключены к одному выводу источника постоянного тока, а их управляющие входы соединены с тактирующими выходами блока управления и обработки информации, выходы вторых ключей в каждом из каналов объединены, два до полните л ьных ключа, управляющий вход первого дополнительного ключа соединен с первым выходом блока управления и обработки информации, второй выход которого соединен с управляющим входом разрядного ключа,

0 подключенного параллельно блоку интегрирования, вход которого соединен с первым выводом образцового резистора, соединенным с входом первого дополнительного ключа, второй вывод которого, подключен5 ный к другому выводу источника постоянного тока, подсоединен к общей шине, а выход блока интегрирования подключен к одному мз входов основного блока сравнения, выход которого соединен со счетным входом

0 триггера, другой вход КОТОРОГО подключен к третьему выходу блока управления и обработки информации, а выход триггера, соединенный с управляющим входом второго дополнительного ключа, объединен с вхо5 дом блока управления и обработки информации, четвертый выход которого соединен с выходом преобразователя, отличаю- щ и и с я тем. что, с целью расширения функциональных возможностей за счет из0 мерения девиации сопротивления, в него дополнительно введены многовходовой сумматор-вы читатель, до по л китель ный блок сравнения, схема считывания, управляемый инвертор, инвертирующий сумма5 тор. опорный резистор и третий ключ в каждом из каналов, причем первые выводы опорных резисторов соединены соответственно с вторыми клеммами для подключения измеряемых .резисторов в каждом

0 канале и подключены к входам третьих клю- , управляющие входы которых соединены с тактирующими выходами блока у (равнения и обработки информации, а их выходы объединены и подключены к вычи5 та ющему входу многовходового сумматора- вычитателя, первый суммирующий вход которого подключен к объединенным выходам первых ключей, второй суммирующий вход - к первому выводу образцового рези0 стора, а выход многовходового суммато- ра-вычитателя соединен с входами управляемого инвертора и дополнительного блока сравнений, выход которого соединен с управляющим входом управляемого

5 инвертора и информационным входом схемы считывания, а выход управляемого Hit- вер горэ соединен с входом второго дополнительного ключа, подключенного выходом к первому входу ;нБерг |рующе 0 сумматора, вторые яыводо опорных резисторов в каждом из каналов объединены и подключены к первому выводу образцового резистора, выход первого дополнительного ключа подключен к второму входу инвертирующего сумматора, соединенному выходом с другим входом основного блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь сопротивления в код | 1986 |

|

SU1411684A1 |

| Многоканальный преобразователь сопротивления тензорезисторов в код | 1983 |

|

SU1190297A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Преобразователь абсолютных приращений сопротивлений тензорезисторов в цифровой код | 1982 |

|

SU1132254A1 |

| Устройство считывания с временной задержкой и накоплением сигналов в цифровом виде с многоэлементных фотоприемников инфракрасного излучения | 2019 |

|

RU2739159C1 |

| Устройство для управления группой из @ объединенных по выходу тиристорных преобразователей | 1986 |

|

SU1394376A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Устройство для передачи телеметрической информации | 1986 |

|

SU1336077A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано в информационно-измерительных системах и измерительных приборах. Цель изобретения - расширение функциональных возможностей за счет изNUЈt №Ј1 3-2 П -Я: & с мерения девиации сопротивления Устройство содержит многовходовой сумматор-вы- читатель 8, дополнительный блок 12 сравнения, управляемый инвертор 13, схему 14 считывания, инвертирующий сумматор 18, опорные резисторы 5-1, 5-2...5-п и ключи 3-1, 3-2...З-n в 1,2.. п каналах Причем первые выводы опорных резисторов 5-1,5- 2...5-п соединены соответственно с вторыми клеммами для подключения измеряемых резисторов 4-1 4-2.,.4-п и подключены к входам третьих ключей 3-1,3- 2,.,3-п, управляющие входы которых соединены соответственно с тактирующими выходами блока 19 управления и обработки информации. Устройство обладает более широкими функциональными возможностями за счет многоканального измерения девиации сопротивления в код 3 ил сл с Ј1 -Я: l5-n j О 00 Ю 00 VJ Фиг 1

Фие.2

| Измеритель девиации сопротивления | 1982 |

|

SU1049826A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Многоканальный преобразователь сопротивления в код | 1986 |

|

SU1411684A1 |

Авторы

Даты

1991-11-07—Публикация

1988-01-04—Подача