Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств аналого-цифрового преобразования и дискретно-аналоговой обработки информации.

Цель изобретения - повышение точности и быстродействия устройства.

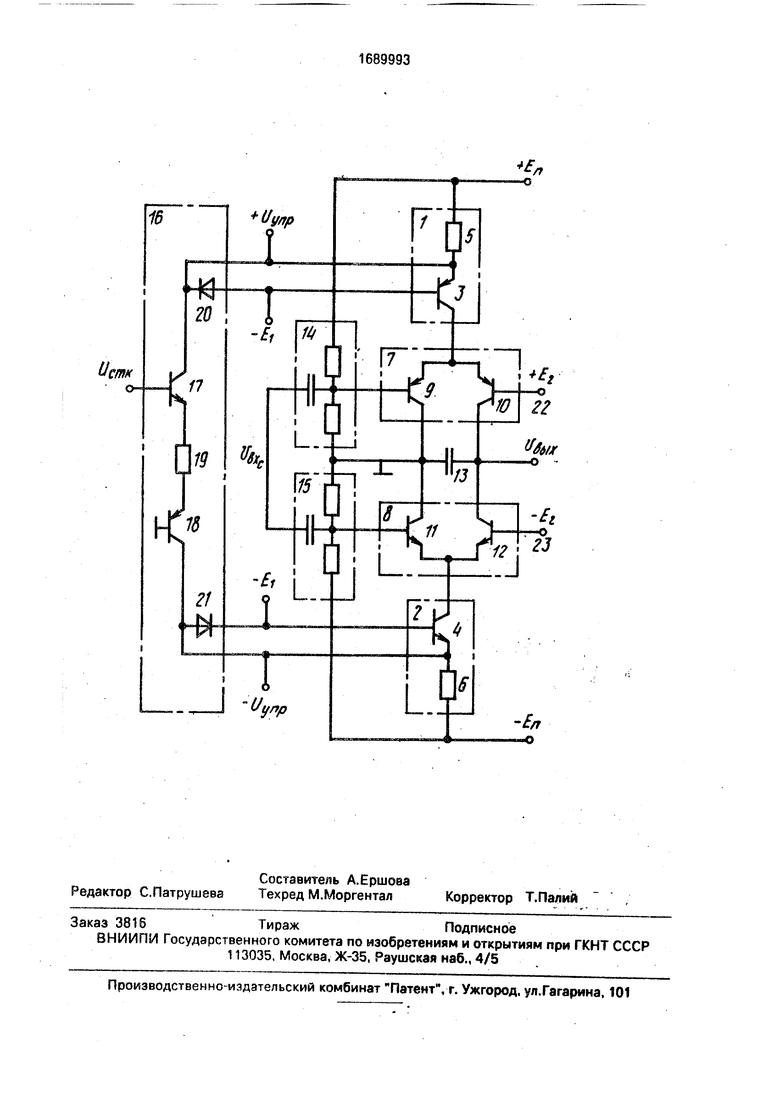

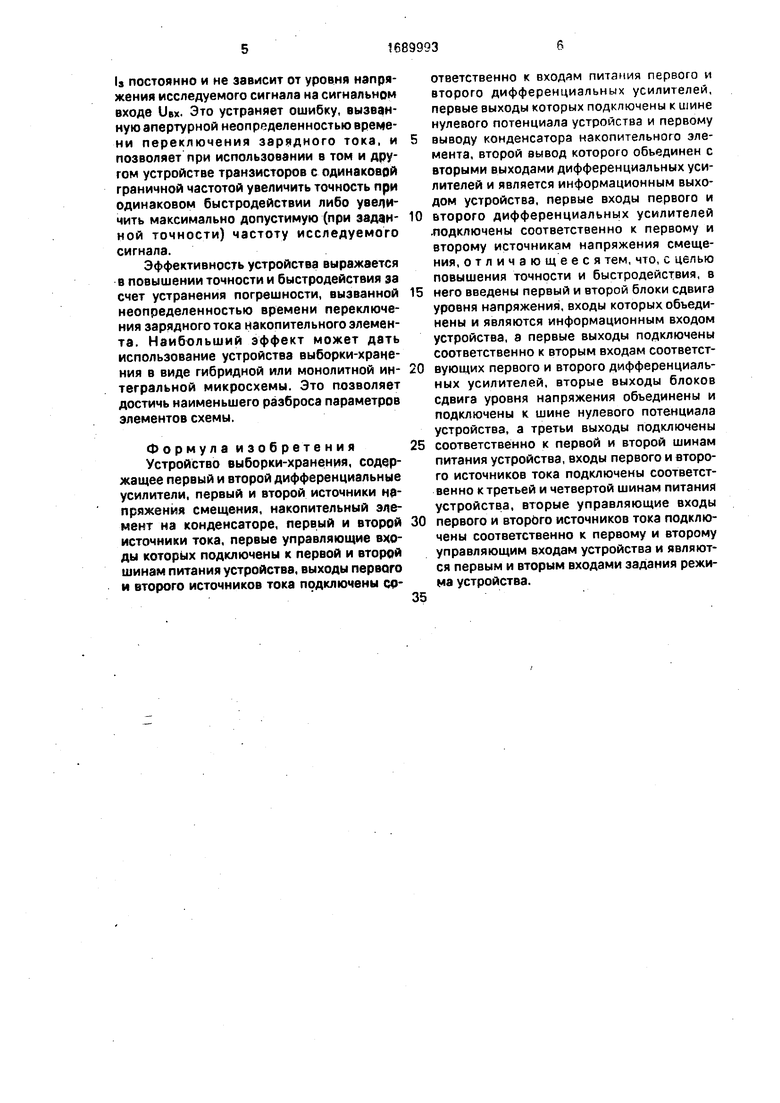

На чертеже представлено предлагаемое устройство.

Устройство содержит источники 1 и 2 тока на транзисторах 3 и 4 и резисторах 5 и 6, дифференциальные усилители 7 и 8, каждый из которых выполнен на транзисторах 9, 10 и 11, 12 соответственно; накопительный элемент 13 на конденсаторе, блоки 14 и 15 сдвига уровня напряжения, блок 16 формирования управляющих сигналов, выполненный на транзисторах 17 и 18, резисторе 19, диодах 20 и 21; источники 22 и 23 напряжения смещения.

Устройство работает следующим образом.

Цикл работы устройства выборки-хранения состоит из двух фаз - выборки и хранения. В режиме выборки на стробирующем входе Ucip - напряжение низкого логического уровня, транзисторы 17 и 18 закрыты и напряжение на шинах + Uynp и -Uynp определяется напряжением соответствующих источников +Ё1 и -Ei напряжения смещения и падением напряжения на открытых змит- терных переходах транзисторов 3 и 4 соответственно. При этом

Uynp Е + 11бэ,

l+Uy

|-UV

(1)

- абсолютгде Uynp I иупр i i - uynp

ная величина напряжений на шинах + Uynp

и -Uynp управления;

Ei |+ Ei I- 1-Ei |-абсолютная величина напряжений источников + Ei и -Ei;

Uea - абсолютная величина падений напряжения на открытых эмиттерных переходах транзисторов 3 и 4.

С 00

ч ю ю ы

Транзисторы 3 и 4 открыты и источники 1 и 2 тока вырабатывают равные по величине и противоположные по направлению токи И и h соответственно, причем I И | I- Ы . Ток И поступает в эмиттерные цепи транзисторов 9 и 10, а ток 12 - в эмиттерные цепи транзисторов 11 и 12. Блоки 14 и 15 обеспечивают равенство постоянной составляющей напряжения на выходах баз транзисторов 9 и 11 величинам напряжения источников +Е2 и -Е2 соответственно, Токи И и h разветвляются в эмиттерные цепи транзисторов 9,10 и 11,12 соответственно, причем пропорция которой делятся токи h и г задается напряжением исследуемого сигнала, поступающего с сигнального входа UBX через блоки 14 и 15 на выводы без транзисторов 9 и 11 соответственно. Известно, что в режиме малого сигнала изменение коллекторного тока транзисторов дифференциального усилителя прямо пропорционально изменению дифференциального напряжения, приложенного между базами транзисторов дифференциального усилителя. В отсутствие исследуемого сигнала дифференциальное напряжение равно нулю и коллекторные токи g, ho и In, 112 транзисторов 9, 10, и 11, 12 равны по абсолютной величине и противоположны по направлению

I l9

hMiil-l-h2l. (2)

При отличном от нуля напряжении исследуемого сигнала токов g, ho, In. ha получают приращения д, Но, In, h2, пропорциональные напряжению исследуемого сигнала U ах.1

19 -111 112 К U

вх,

(3)

гдб К - коэффициент пропорциональности, имеющий смысл крутизны (А/В).

В результате возникает зарядный ток (3 элемента 13 равный сумме с учетом знака коллекторных токов транзисторов .10 и 12

1з Ho + ltt.

(4)

Подставляя (3) в (4) получаем

1а К UBX + Кох 2К UBX. (5)

ТРКИМ образом а предлагаемом устройстве усилители 7 & 8 осуществляют преобразование напряжения UBX в пропорциональное значение зарядного тока 3. По отношению к. исследуемому сигналу каждый дифференциальный каскад представляет собой каскадную схему: общий коллектор - общая база, что обеспечивает широкую полосу пропускания и высокую линейность преобразования UBX в 1Э.

На элементе 13 происходит-интегрирование зарядного тока Is в соответствии с формулой

ДЦ / b,dt

(6)

где Дис - напряжение на элементе 13; С - емкость накопительного конденсатора 13;

&t- интервал интегрирования.

Подставляя (5) в (6), получаем

АЦ / UBX dt.

С А

(7)

20

Таким образом, напряжение Лис на злементе 13 пропорционально интегралу напряжения UBX исследуемого сигнала за

Переход от фазы выборки к фазе хранения происходит следующим образом. На вход Остр, подается напряжение высокого логического уровня, транзисторы 17 и 18 открываются и напряжение на шинах +Uynp и -Uynp определяется напряжением источников +Ei и -Ei напряжения смещения соответственно и падением напряжения на открытых p-n-переходах диодов 20 и 21 соответственно. При этом

Uynp - EI ид.

(8)

0

где Уд - абсолютная величина падений напряжения на открытых p-n-переходах диодов 20,и 21.

Таким образом, диоды 20 и 21 предотвращают насыщение транзисторов 17 и 18 соответственно, фиксируя напряжения на выводах их коллекторов. Транзисторы 3 и 4 закрываются, так как их эмиттерные переходы оказываются обратно смещенными. В результате первый вывод элемента 13 оказывается подключенным к точке высокого импеданса и на нем сохраняется напряжение AUc, установившееся к моменту окончания фазы выборки.

При близких параметрах транзисторов 17 и 18 нарастание их коллекторных токов при переходе от фазы выборки к фазе хранения происходит строго одновременно. Также одновременно происходит процесс выключения источников 1 и 2 тока при близких параметрах транзисторов 3 и 4.

Таким образом, время с момента прихода фронта стробирующего импульса на вход Ucrp до полного выключения зарядного тока

Is постоянно и не зависит от уровня напряжения исследуемого сигнала на сигнальном входе UBX. Это устраняет ошибку, вызванную апертурной неопределенностью време- ни переключения зарядного тока, и позволяет при использовании в том и другом устройстве транзисторов с одинаковой граничной частотой увеличить точность при одинаковом быстродействии либо увеличить максимально допустимую (при заданной точности) частоту исследуемого сигнала.

Эффективность устройства выражается в повышении точности и быстродействия за счет устранения погрешности, вызванной неопределенностью времени переключения зарядного тока накопительного элемента. Наибольший эффект может дать использование устройства выборки-хранения в виде гибридной или монолитной интегральной микросхемы. Это позволяет достичь наименьшего разброса параметров элементов схемы.

Формула изобретения Устройство выборки-хранения, содержащее первый и второй дифференциальные усилители, первый и второй источники напряжения смещения, накопительный элемент на конденсаторе, первый и второй источники тока, первые управляющие входы которых подключены к первой и второй шинам питания устройства, выходы первого и второго источников тока подключены соответственно к входам питания первого и второго дифференциальных усилителей, первые выходы которых подключены к шине нулевого потенциала устройства и первому

выводу конденсатора накопительного элемента, второй вывод которого обьединен с вторыми выходами дифференциальных усилителей и является информационным выходом устройства, первые входы первого и

второго дифференциальных усилителей .подключены соответственно к первому и второму источникам напряжения смещения, отличающееся тем, что, с целью повышения точности и быстродействия, в

него введены первый и второй блоки сдвига уровня напряжения, входы которых объединены и являются информационным входом устройства, а первые выходы подключены соответственно к вторым входам соответствующих первого и второго дифференциальных усилителей, вторые выходы блоков сдвига уровня напряжения объединены и подключены к шине нулевого потенциала устройства, а третьи выходы подключены

соответственно к первой и второй шинам питания устройства, входы первого и второго источников тока подключены соответственно к третьей и четвертой шинам питания устройства, вторые управляющие входы

первого и второго источников тока подключены соответственно к первому и второму управляющим входам устройства и являются первым и вторым входами задания режима устройства.

19

%

L.,

hH

0 //

HI

/J

&/ -о //

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки и хранения | 1980 |

|

SU921087A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

| Электронное реле | 1981 |

|

SU993474A1 |

| Устройство для хранения и выборки информации | 1975 |

|

SU553685A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU903988A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Дифференциальный усилитель | 1982 |

|

SU1107279A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств аналого-цифрового преобразования и дискретно-аналоговой обработки информации. Цель изобретения - повышение точности и быстродействия устройства. Цель достигается за счет уменьшения апертур- ной неопределенности и минимально допустимого времени выборки, снижения величины переноса заряда, а также благодаря появлению шумов и помех. Время выборки и апертурной задержки определяется быстродействием ключевых устройств, в частности временем включения (и выключения) источников тока. Величина апертурной неопределенности устраняется за счет того, что сигналы шин управления подаются в точки схемы, напряжение и ток которых не зависят от напряжения входного сигнала. 1 ил.

| Бахтиаров Г.Д | |||

| и др | |||

| Аналого-цифровые преобразователи | |||

| М.: Сов | |||

| радио, 1980, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

| ПНЕВМАТИЧЕСКИЙ ДВИГАТЕЛЬ | 1923 |

|

SU627A1 |

| Патент США № 3839679, кл | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1991-11-07—Публикация

1989-12-05—Подача