(5) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU826341A1 |

| Устройство для умножения | 1981 |

|

SU974370A1 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Одноразрядный сумматор | 1977 |

|

SU734681A1 |

I

Изобретение относится к вычислительной технике, предназначено в основном для использования в следящерегулируемых электроприводах переменного и постоянного тока с цифровым упр влением, а также в вычислительных системах управления этими приводами и осуществляет умножение двух чисел в многофазном коде.

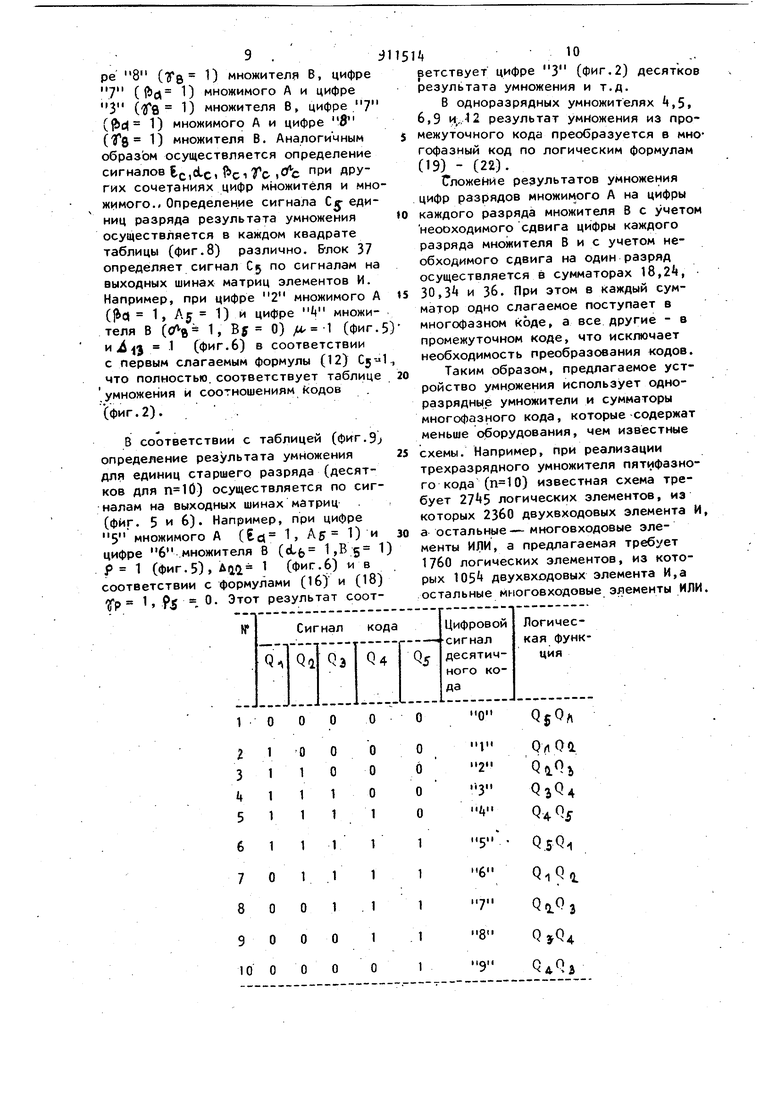

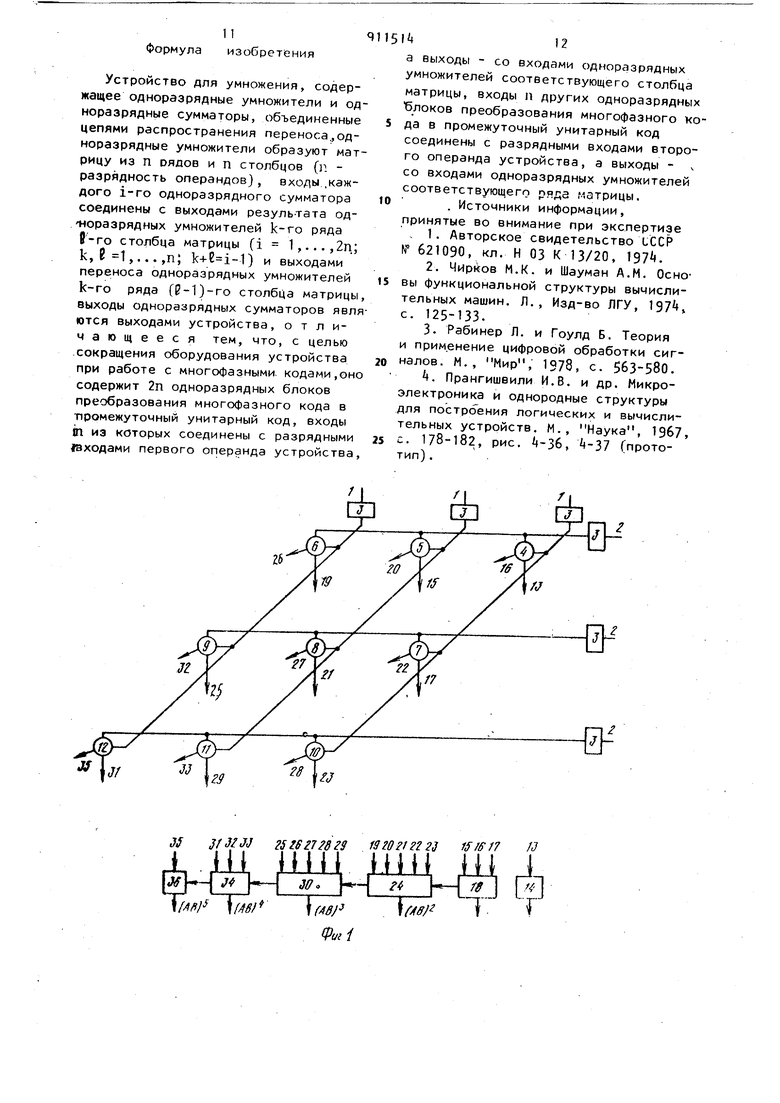

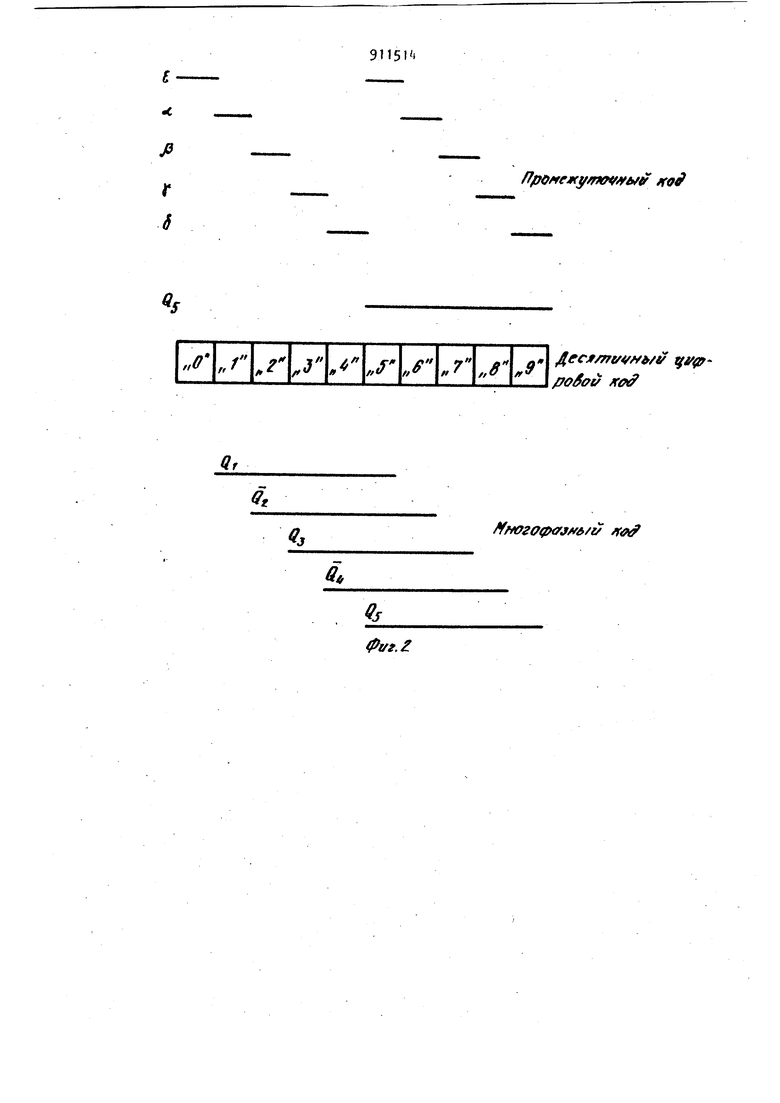

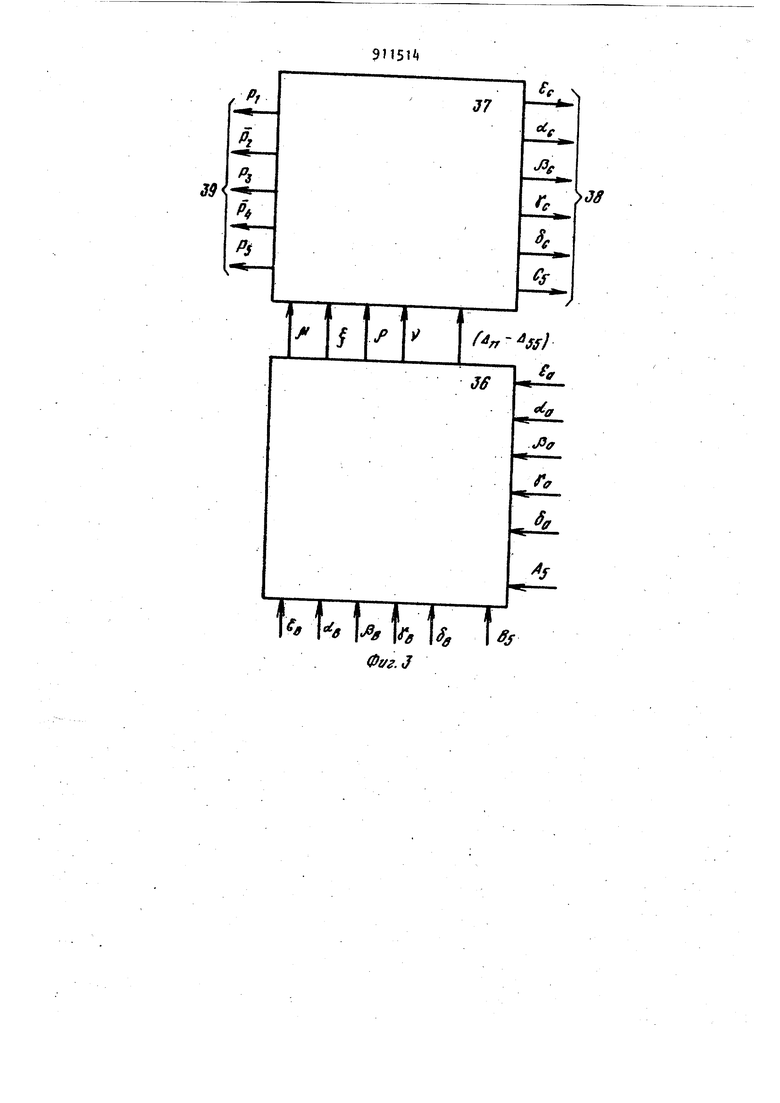

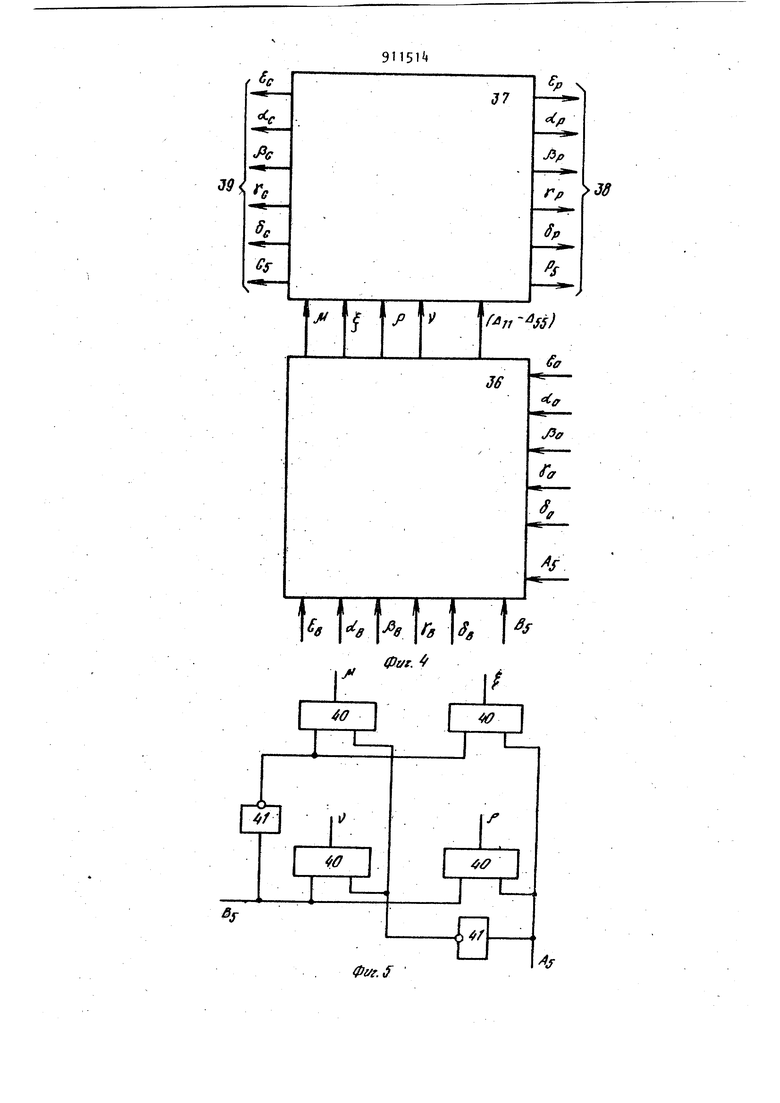

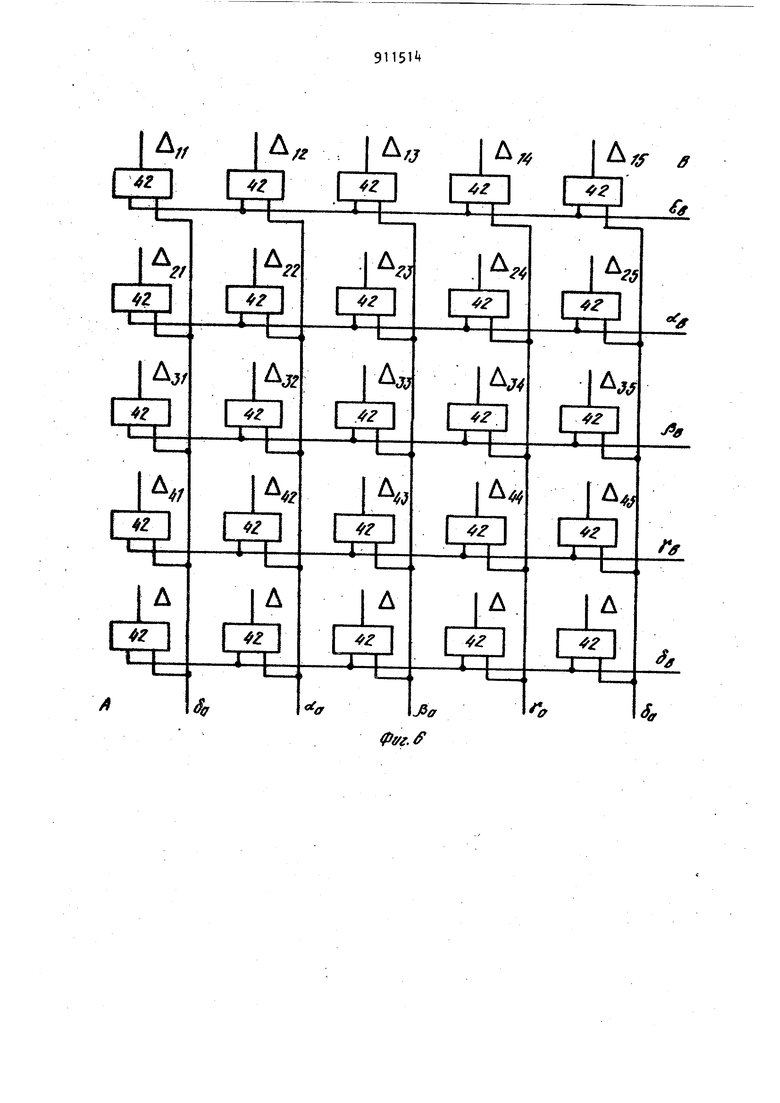

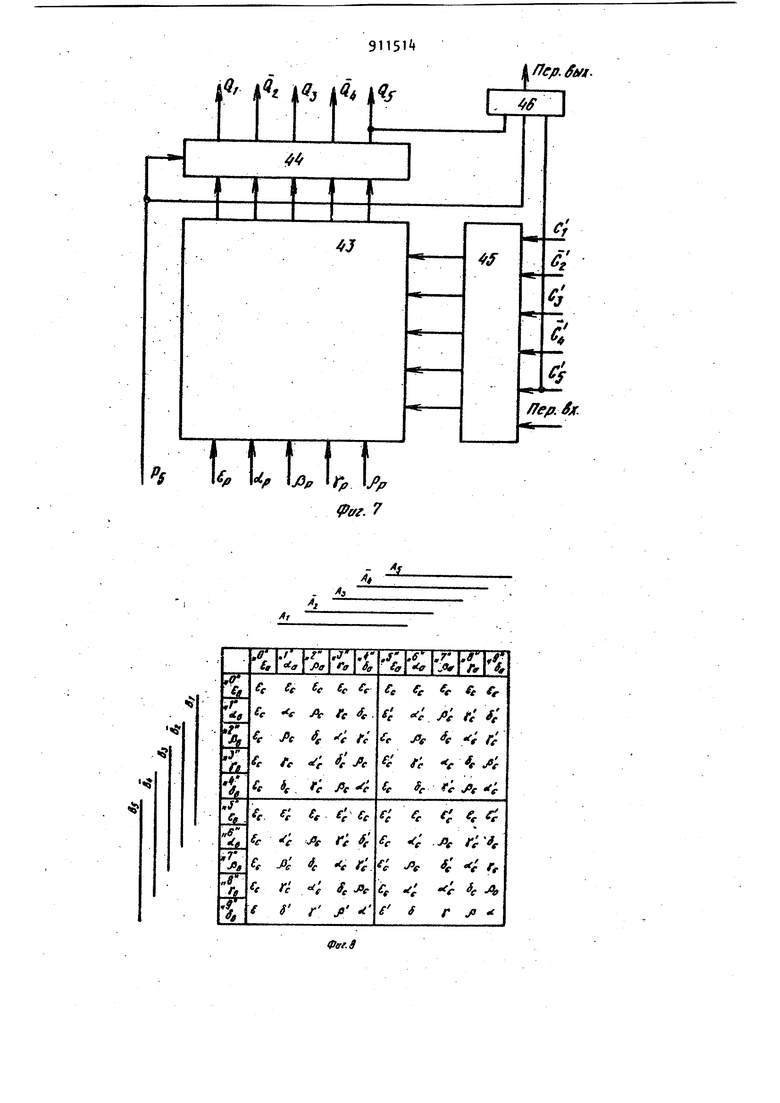

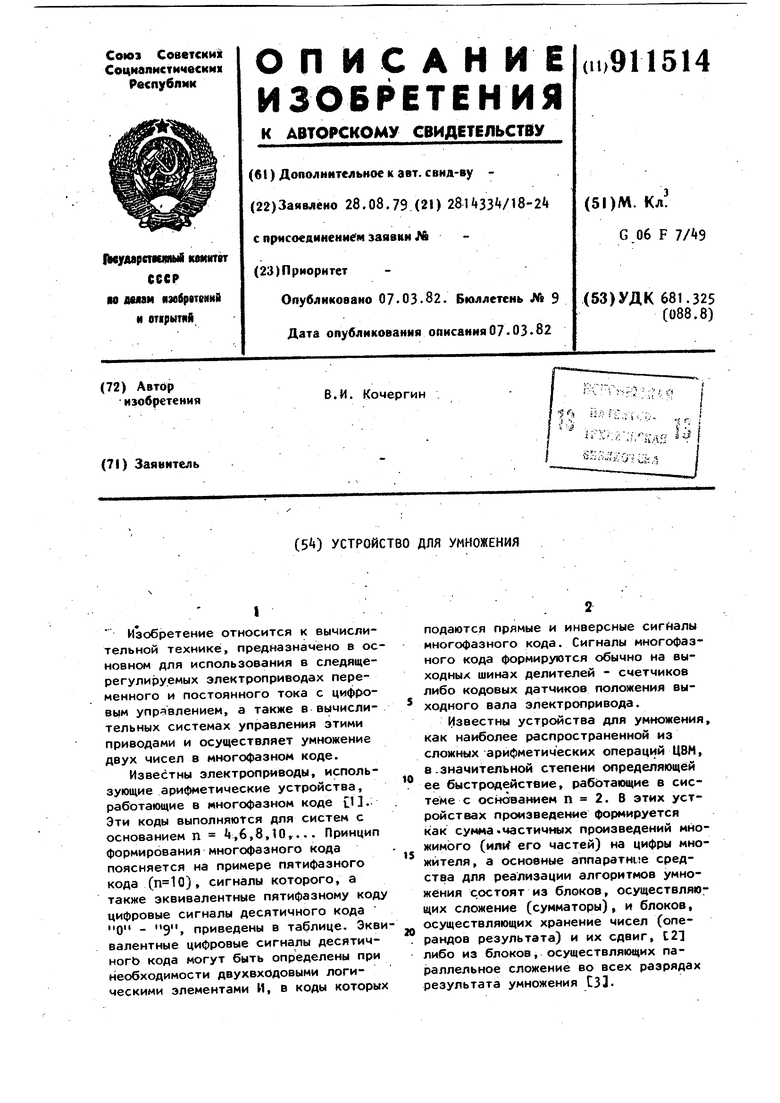

Известны электроприводы, использующие арифметические устройства, работающие в многофазном коде П.. . Эти коды выполняются для систем с основанием п 1,6,8,10,... Принцип формирования многофазного кода поясняется на примере пятифазного кода (), сигналы которого, а также эквивалентные пятифазному коду цифровые сигналы десятичного кода О - 9, приведены в таблице. Эквивалентные цифровые сигналы десятичногЬ кода могут быть определены при необходимости двухвходовыми логическими элементами И, в коды которых

подаются прямые и инверсные сигналы многофазного кода. Сигналы многофазного кода формируются обычно на выходных шинах делителей - счетчиков либо кодовых датчиков положения выходного вала электропривода.

Известны устройства для умножения, как наиболее распространенной из сложных арифметических операций ЦВМ, в.значительной степени определяющей

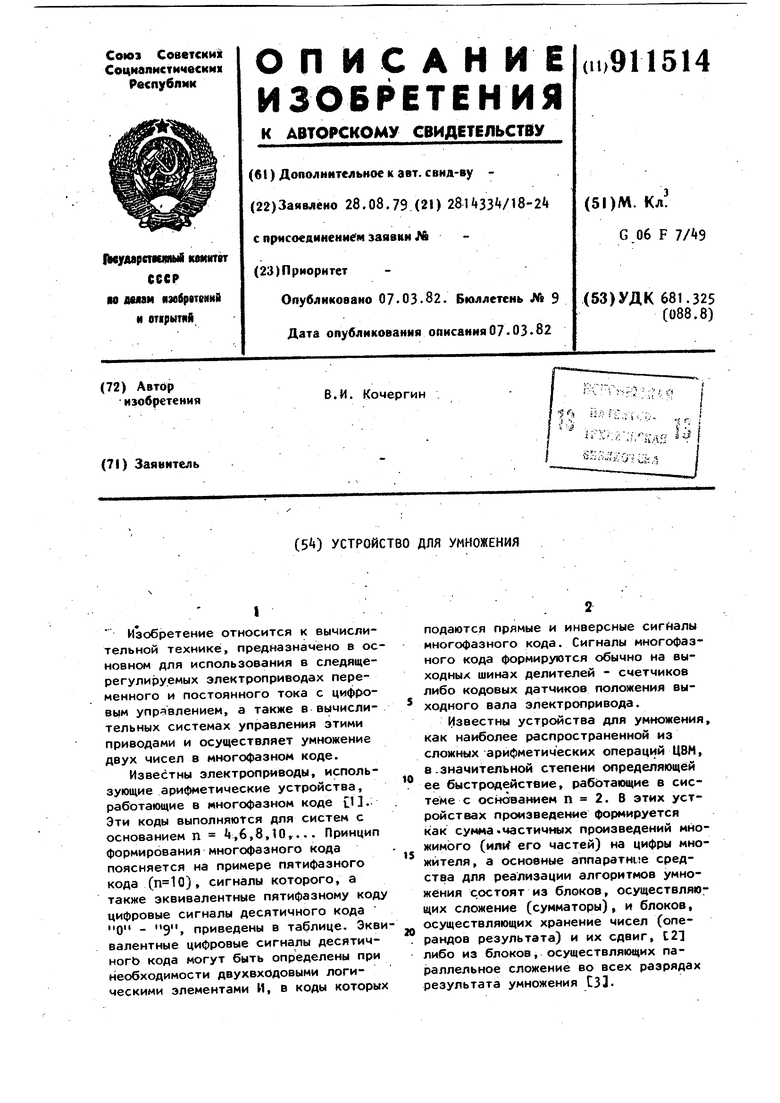

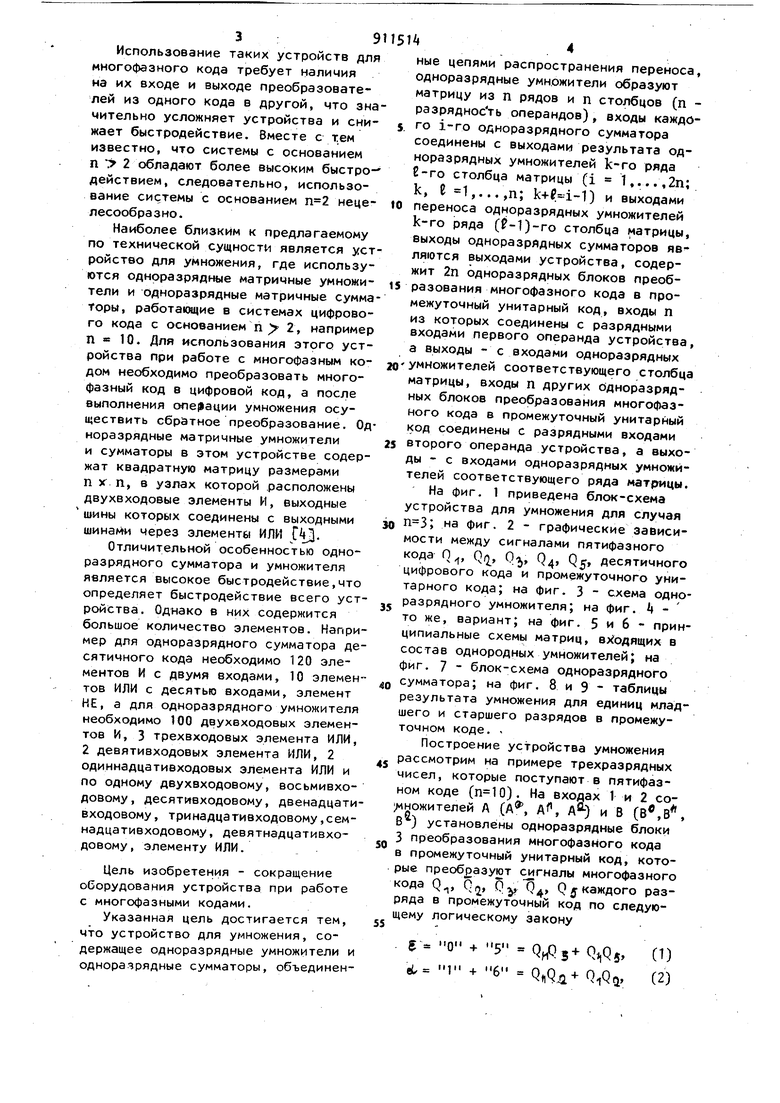

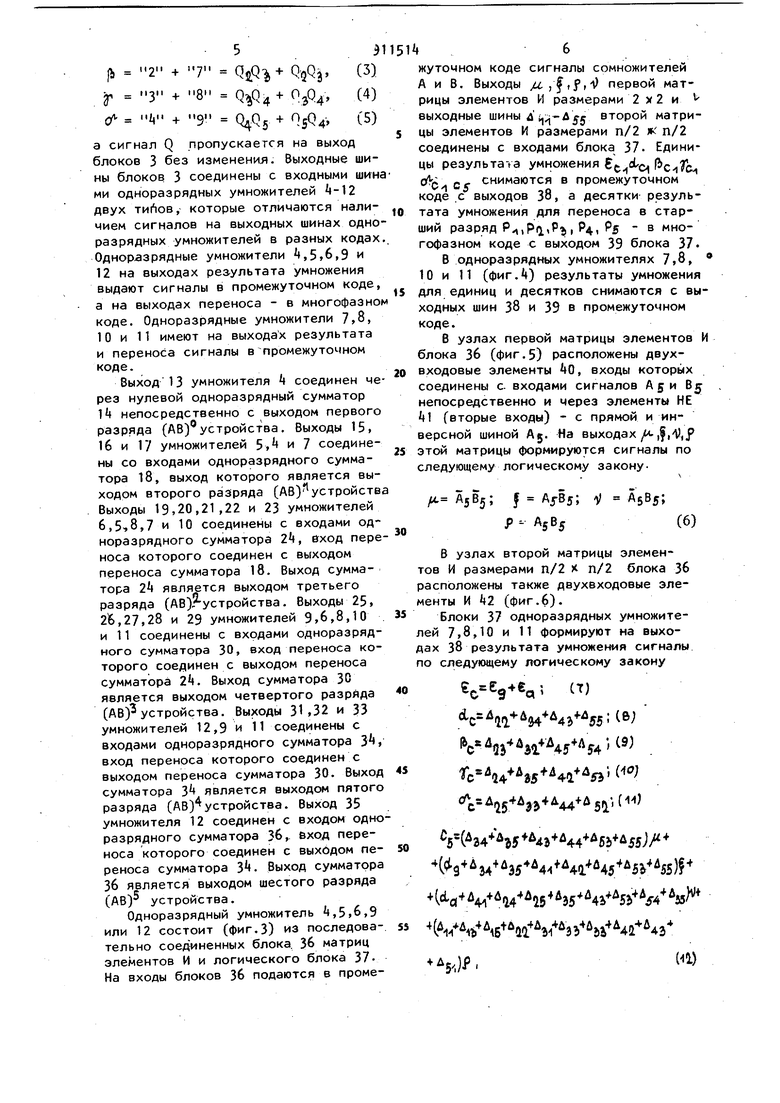

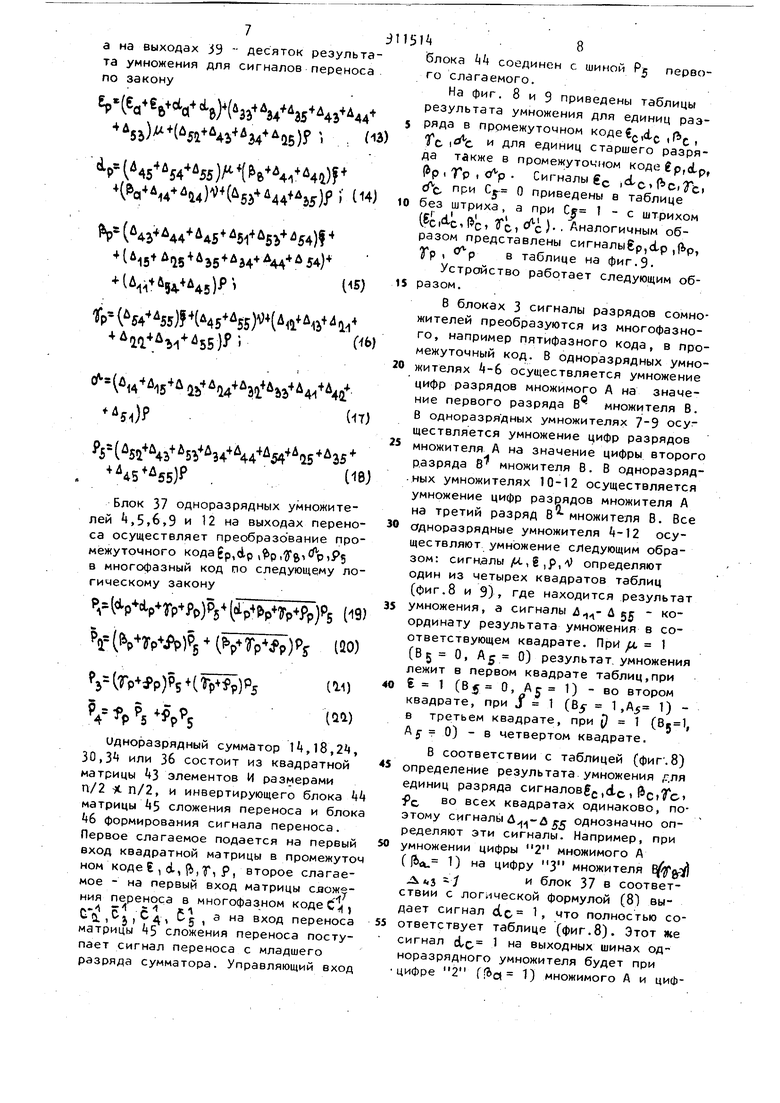

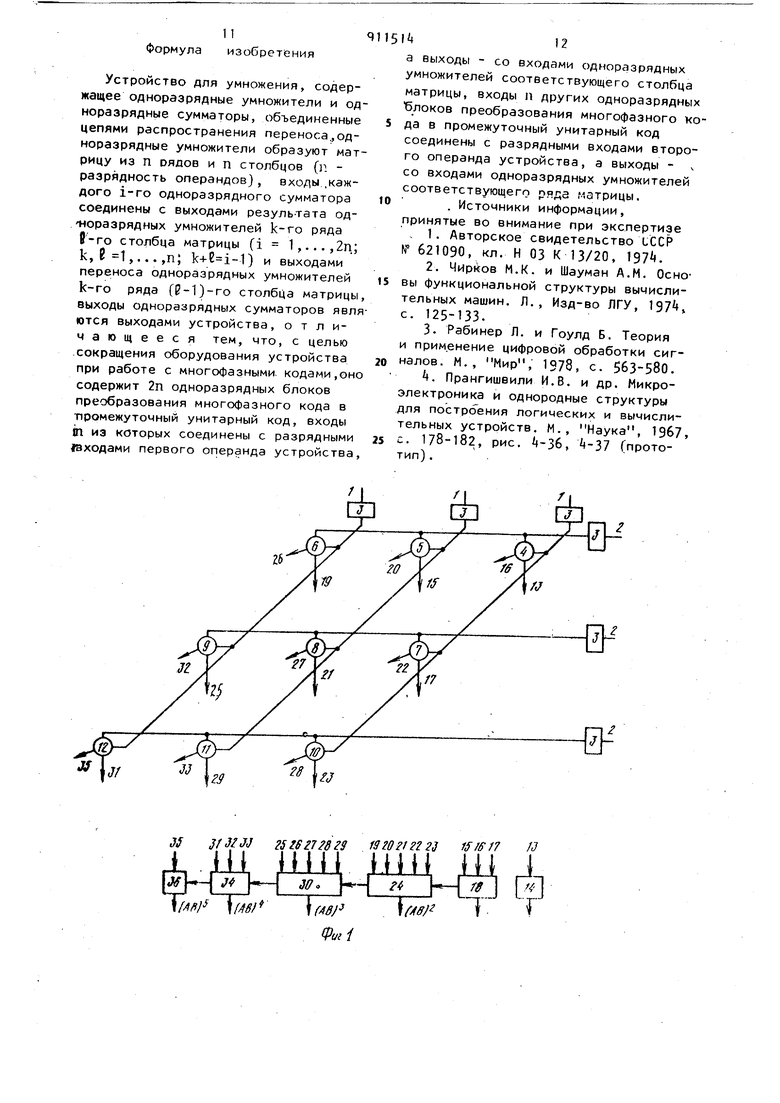

to ее быстродействие, работающие в системе с основанием п 2. В этих устройствах произведение формируется как сумма«частичных произведений множимого (ип его частей) на цифры мно15жителя, а основные аппаратные средства для реализации алгоритмов умножения состоят из блоков, осуществляющих сложение (сумматоры), и блоков, осуществляющих хранение чисел (опе20рандов результата) и их сдвиг, С21 либо из блоков, осуществляющих параллельное сложение во всех разрядах результата умножения СЗЗ39Использование таких устройств для многофазного кода требует наличия на их входе и выходе преобразователей из одного кода в другой, что зна чительно усложняет устройства и снижает быстродействие. Вместе с тем известно, что системы с основанием п 2 обладают более высоким быстродействием, следовательно, использование системы с основанием нецелесообразно. Наиболее близким к предлагаемому по технической сущности является уст ройство для умножения, где используются одноразрядные матричные умножители и одноразрядные матричные сумма торы, работакяцие в системах цифрового кода с основанием п 2, например П « 10. Для использования этого устройства при работе с многофазным кодом необходимо преобразовать многофазный код в цифровой код, а после выполнения операции умножения осуществить сбрЭтное преобразование. Од норазрядные матричные умножители и сумматоры в этом устройстве содержат квадратную матрицу размерами п х п, в узлах которой расположены двухвходовые элементы И, выходные шины которых соединены с выходными шинакН1 через элемента ИЛИ tjj. Отличительной особенностью одноразрядного сумматора и умножителя является высокое быстродействие,что определяет быстродействие всего устройства. Однако в них содержится большое количество элементов. Нагфимер для одноразрядного сумматора десятичного кода необходимо 120 элементов И с двумя входами, 10 элементов ИЛИ с десятью входами, элемент НЕ, а для одноразрядного умножителя необходимо 100 двухвходовых элементов И, 3 трехвходовых элемента ИЛИ, 2 девятивходовых элемента ИЛИ, 2 одиннадцативходовых элемента ИЛИ и по одному двухвходовому, восьмивходовому, десятивходовому, двенадцативходовому, тринадцативходовому,семнадцативходовому, девятнадцативходовому, элементу ИЛИ. Цель изобретения - сокращение оборудования устройства при работе с многофазными кодами. Указанная цель достигается тем, что устройство для умножения, содержащее одноразрядные умножители и одноразрядные сумматоры, объединен4ные цепями распространения переноса, одноразрядные умножители образуют матрицу из п рядов и п столбцов (п разрядность операндов), входы каждого i-ro одноразрядного сумматора соединены с выходами результата одноразрядных умножителей k-ro ряда е-го столбца матрицы (i 1,...,2п; k, С 1,,..,п; ) и выходами переноса одноразрядных умножителей k-ro ряда (-1)-го столбца матрицы, выходы одноразрядных сумматоров являются выходами устройства, содержит 2п одноразрядных блоков преобразования многофазного кода в промежуточный унитарный код, входы п из которых соединены с разрядными входами первого операнда устройства, а выходы - с входами одноразрядных умножителей соответствующего столбца матрицы, входы п других одноразрядных блоков преобразования многофазного кода в промежуточный унитарный код соединены с разрядными входами второго операнда устройства, а выходы - с входами одноразрядных умножителей соответствующего ряда матрицы. На фиг. 1 приведена блок-схема устройства для умножения для случая на фиг. 2 - графические зависимости между сигналами пятифазного кода П, QQ, 0, Q, Q, десятичного цифрового кода и промежуточного унитарного кода; на фиг. 3 - схема одноразрядного умножителя; на фиг. то же, вариант; на фиг. 5 и 6 - принципиальные схемы матриц, вводящих в состав однородных умножителей; на фиг. 7 - блок-схема одноразрядного сумматора; на фиг. 8 и 9 - таблицы результата умножения для единиц младшего и старшего разрядов в промежуточном коде. Построение устройства умножения рассмотрим на примере трехразрядных чисел, которые поступают в пятифазном коде (. На входах 1 и 2 со:множителей А (А, А, А ) и В (В,В, В) установлены одноразрядные блоки 3 преобразования многофазного кода в промежуточный унитарный код, которые преобразуют сигналы многофазного кода Q, 0,j, Ру Q, Qj каждого разряда в промежуточный код по следуюПЯЛА R nnDMPW VTOUUi.tiH nrt г ПАП«УШ щему логическому закону g- -Оп ..5.. , (1) е 1 ч- 6 QflQ.ri+ Q.Qfi, (2) (b 2 + 7 QQQa + 8 .4, Т 3 0 V + 9 + OjQ. a сигнал Q пропускается на выход блоков 3 без изменения. Выходные шины блоков 3 соединены с входными шин ми одноразрядных умножителей -12 двух , которые отличаются наличием сигналов на выходных шинах одно разрядных умножителей в разных кодах Одноразрядные умножители ,5.6,9 и 12 на выходах результата умножения выдают сигналы в промежуточном коде, а на выходах переноса - в многофазно коде. Одноразрядные умножители 7.8, 10 и 11 имеют на выходах результата и переноса сигналы в промежуточном коде. Выход 13 умножителя k соединен че рез нулевой одноразрядный сумматор 1 непосредственно с выходом первого разряда (АВ)устройства. Выходы 15, 16 и 17 умножителей 5, и 7 соединены со входами одноразрядного сумматора 18, выход которого является выходом второго разряда (АВ)устройств Выходы 19,20,21,22 и 23 умножителей 6,5-,8,7 и 10 соединены с входами од норазрядного сумматора 2, вход пере носа которого соединен с выходом переноса сумматора 18. Выход сумматора 2 является выходом третьего разряда (АВ)-устройства. Выходы 25, 26,27,28 и 29 умножителей 9,6,8,10 и 11 соединены с входами одноразрядного сумматора 30, вход переноса которого соединен с выходом переноса сумматора 2. Выход сумматора 30 является выходом четвертого разряда (АВ) устройства. Выходы 31,32 и 33 умножителей 12,9 и 11 соединены с входами одноразрядного сумматора З вход переноса которого соединен с выходом переноса сумматора 30. Выход сумматора З является выходом пятого разряда (АВ)устройства. Выход 35 умножителя 12 соединен с входом одно разрядного сумматора Зб, вход переноса которого соединен с выходом переноса сумматора 3. Выход сумматора Зб является выходом шестого разряда (АВ) устройства. Одноразрядный умножитель ,5,6,9 или 12 состоит (фиг.З) из последовательно соединенных блока. 36 матриц элементов И и логического блока 37. На входы блоков 36 подаются в промеЗ6 жуточном коде сигналы сомножителей А и В. Выходы /. первой матрицы элементов И размерами 2 х2 и выходные шины А i, второй матрицы элементов И размерами п/2 ) п/2 соединены с входами блока 37. Единицы результата умножения 6 .otcj l c-iTc-. OV с с снимаются в промежуточном коде с выходов 38, а десятки результата умножения для переноса в старший разряд Р,Р(,Р, Р4, Р - в многофазном коде с выходом 39 блока 37. В одноразрядных умножителях 7,8, 10 и 11 (фиг.) результаты умножения для единиц и десятков снимаются с выходных шин 38 и 39 в промежуточном коде. В узлах первой матрицы элементов И блока 36 (фиг.5) расположены двухвходовые элементы tO, входы которых соединены с. входами сигналов А5и Bj непосредственно и через элементы НЕ k (вторые входы) - с прямой и инерсной шиной Aj. На выходах/ ifiAlip той матрицы формируются сигналы по ледующему логическому закону AjBj; f AJ-B5; V А5В5; я- А5В5(6) в узлах второй матрицы элеменов И размерами п/2 п/2 блока 36 асположены также двухвходовые элеенты И 42 (фиг.6). Блоки 37 одноразрядных умножитеей 7,8,10 и 11 формируют на выхоах 38 результата умножения сигналы о следующему логическому закону .с (° (34 Лг5 Э 4 5Ь Д55;/ ) sOi. 1 а на выходах 39 десяток результата умножения для сигналов переноса по закону )()i ),)Г )()Я V()f- (5 АН 54) ) fp-- () )( ll аа.)) )P( 54 ) . Блок 37 одноразрядных умножителей ,5,6,9 и 12 на выходах переноса осуществляет преобразование промежуточного кода gp,dp . в многофазный код по следующему логическому закону Pr(Wrp Pp}P54V VPp)P5 И9 V(W)V()J 20) V()Ps4rp p)P5 V Р 5 Одноразрядный сумматор 1,18,, 30,3 или 36 состоит из квадратной матрицы элементов И размерами П/2 X П/2, и инвертирующего блока 4 матрицы 45 сложения переноса и блок 46 формирования сигнала переноса. Первое слагаемое подается на первый вход квадратной матрицы в промежуто ном коде Е , d, (%,Ti Я) второе слагаемое - на первый вход матрицы свожения переноса в многофазном коде I. 5 переноса матрицы 45 сложения переноса поступает сигнал переноса с младшего разряда сумматора. Управляющий вход 48 блока 44 соединен с шиной Р первого слагаемого. На фиг. 8 и 9 приведены таблицы результата умножения для единиц раэряда в пррмежутомном кодев Д ,fb Те и для единиц старшего разряда также в промежуточном коде6р,р, (JptTpiO p- Сигналы €с .fc.Jbi сЛс, при С О приведены в таблице без штриха, а при Сд 1 - с штрихом (cAcil c t ) Аналогичным образом представлены cигнaлы8p,dp ,(Ьр, В таблице на фиг.9. Устройство работает следующим образом. В блоках 3 сигналы разрядов сомножителей преобразуются из многофазного, например пятифазного кода, в промежуточный код. В одноразрядных умножителях 4-6 осуществляется умножение цифр разрядов множимого А на значение первого разряда В множителя В. 6 одноразрядных умножителях 7-9 осуг ществляется умножение цифр разрядов множителя А на значение цифры второго разряда 8 множителя В. В одноразрядных умножителях 10-12 осуществляется умножение цифр разрядов множителя А на третий разряд множителя В. Все одноразрядные умножителя 4-12 осуществляют умножение следующим образом: сигналы/W, ,§ ,р, л) определяют один из четырех квадратов таблиц (фиг.8 и 9). где находится результат умножения, а сигналы Д 55 ординату результата умножения в соответствующем квадрате. При (л 1 (В к О, А 0) результат, умножения лежит в первом квадрате таблиц,при 6 1 (В5 О, AJ 1) - во втором квадрате, при S 1 (В 1,А5 1) в третьем квадрате, при ( 1 (Вд 1, Ау 0) - в четвертом квадрате. В соответствии с таблицей (фиг . 8) определение результата умножения для единиц разряда сигналов,dc i 0ciTc с, во всех квадратах одинаково, поэтому сигналы ГС однозначно определяют эти сигналы. Например, при умножении цифры 2 множимого А f . 1) на цифру 3 множителя gд 3 i у и блок 37 в соответствии с логической формулой (8) выдает сигнал cLc то полностью соответствует таблице (фиг.8). Этот же сигнал , 1 на выходных шинах одноразрядного умножителя будет при цифре 2 ffbci 1) множимого А и цифре 8 (TTg 1) множителя В, цифре 7 (|Ьй 1) множимого А и цифре 3 (fe 1) множителя В, цифре 7 (ibc| 1) множимого А и цифре 8 (Тв 1) множителя В. Аналогичным образом осуществляется определение сигналов Ь.,dieil ci То , при других сочетаниях цифр множителя и мно жимого.. Определение сигнала С г единиц разряда результата умножения осуществляется в каждом квадрате таблицы (фиг,8) различно. &лок 37 определяет сигнал Cj по сигналам на выходных шинах матриц элементов И. Например, при цифре 2 множимого А (jiq 1 , Aj 1) И цифре МНОЖИтеля в (сЛв 1, Bf 0) /u. -1 (фиг. и 5 .1 (фиг.6) в соответствии с первым слагаемым формулы (12) Cj-- что полностью, соответствует таблице умножения и соотношениям кодов (фиг.2). . В соответствии с таблицей (фиг.9 определение результата умножения для единиц старшего разряда (десятков для ) осуществляется по сигналам на выходных шинах матриц (фиг. 5 и 6). Например, при цифре 5 множимого А (с 1 А5 1) и цифре 6 множителя В (dlfc 1,85 1 Р 1 (ФИГ.5) , AICL (фиг. 6) MB соответствии с формулами (16) и (18) р 1 , Р - - Этот результат соответствует цифре 3 (фиг.2) десятков результата умножения и т.д. В одноразрядных умножителях i,5, 6,9 n,,J2 результат умножения из промежуточного кода преобразуется в многофазный код по логическим формулам (19) - (22). Сложение результатов умножения цифр разрядов множимого А на цифры каждого разряда множителя В с учетом неооходимого сдвига цифры каждого разряда множителя Вис учетом необходимого сдвига на один разряд осуществляется в сумматорах 18,2, 30,3 и Зб. При этом в каждый сумматор одно слагаемое поступает в многофазном коде, а все другие - в промежуточном коде, что исключает необходимость преобразования кодов. Таким образом, предлагаемое устройство умножения использует одноразрядные умножители и сумматоры многофазного кода, которые содержат меньше оборудования, чем известные схемы. Например, при реализации трехразрядного умножителя пятифазного кода () известная схема треует логических элементов, из которых 2360 двухвходовых элемента И, остальные-многовходовые элеенты ИЛИ, а предлагаемая требует 1760 логических элементов, из которых 105 двухвходовых элемента И,а стальные Многовходовые элементы ИЛИ. 1 1 изобрет ения Формула Устройство для умножения, содержащее одноразрядные умножители и од норазрядные сумматоры, объединенные цепями распространения переноса,,одноразрядные умножители образуют мат рицу из п рядов и п столбцов (г. разрядность операндов), входы .каждого i-ro одноразрядного сумматора соединены с выходами резуль-тата одноразрядных умножителей k-ro ряда fl-ro столбца матрицы (i 1,...,2п; k,1,...,п; ) и выходами переноса одноразрядных умножителей k-ro ряда (5-1)-го столбца матрицы выходы одноразрядных сумматоров явл ются выходами устройства, отличающееся тем, что, с целью .сокращения оборудования устройства при работе с многофазными, кодами,он содержит 2п одноразрядных блоков преобразования многофазного кода в промежуточный унитарный код, входы in из которых соединены с разрядными |аходами первого операнда устройства 412 а выходы - со входами одноразрядных умножителей соответствующего столбца матрицы, входы и других одноразрядных блоков преобразования многофазного кода в промежуточный унитарный код соединены с разрядными входами второго операнда устройства, а выходы - . со входами одноразрядных умножителей соответствующего ряда матрицы. . Источники информации, принятые во внимание при экспертизе , 1. Авторское свидетельство LCCP N 621090, кл, Н 03 К 13/20, 197. 2.Чирков М.К. и Шауман А.М, Основы функциональной структуры вычислительных машин. Л., Изд-во ЛГУ, с. 125-133. 3.Рабинер Л. и Гоулд Б. Теория и применение цифровой обработки сигналов. М., Мир, 1978, с. 563-580. . Прангишвили И.В. и др. Микроэлектроника и однородные структуры для построения логических и вычислительных устройств. М., Наука, 19б7, с. 178-182, рис. -36, 4-37 (прототип) .

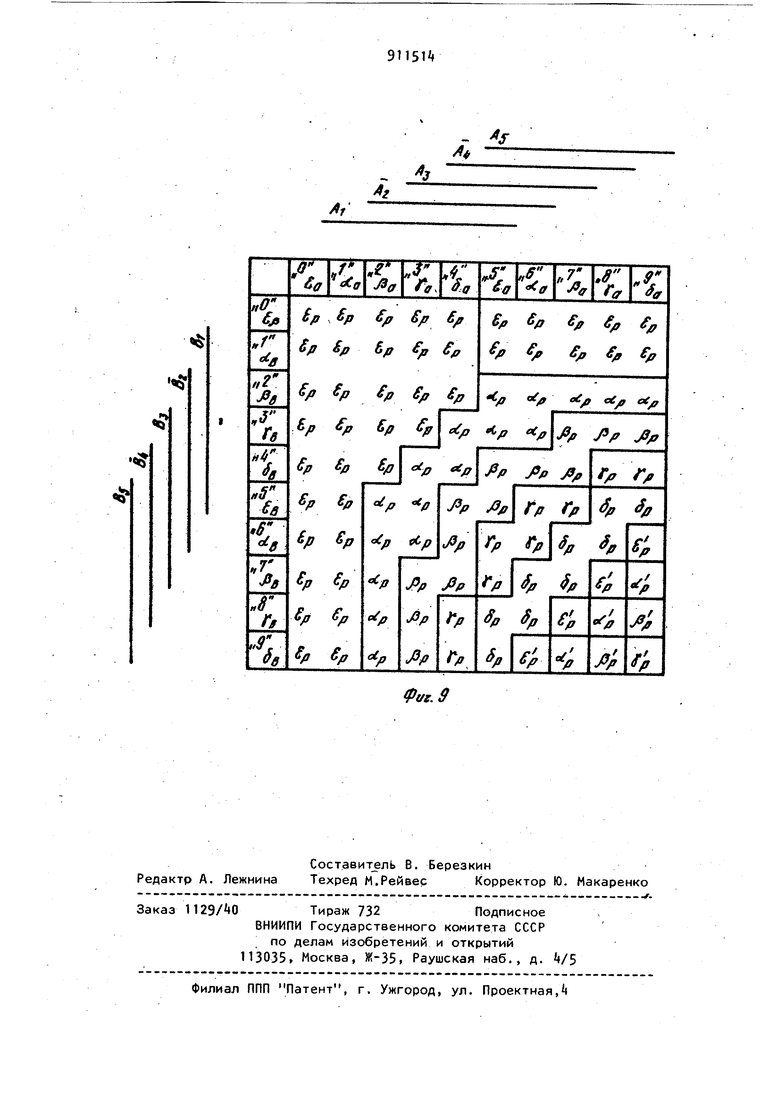

25 ZS17 2829

HHI

is/e)7 /J

1920 12223

f

r

3

ff ftejKy/rftfV tf/ ffof

ecjtmu4/ /v

fCffiff

ffO2O J 6/i/ ffff

Vf.l

14 ь U t U 1

0y.J

J

б , §, f

38

Ф1/Г.

к

J

Фг/f.f Д,/ |Л, , I А, IfI I г I 4гг 4г j:: :::1

fpfff.ff I А;« I А ;5Г ff Д П-ЕГ л f k Ц. U In I

5

ZV/. У

..

- f

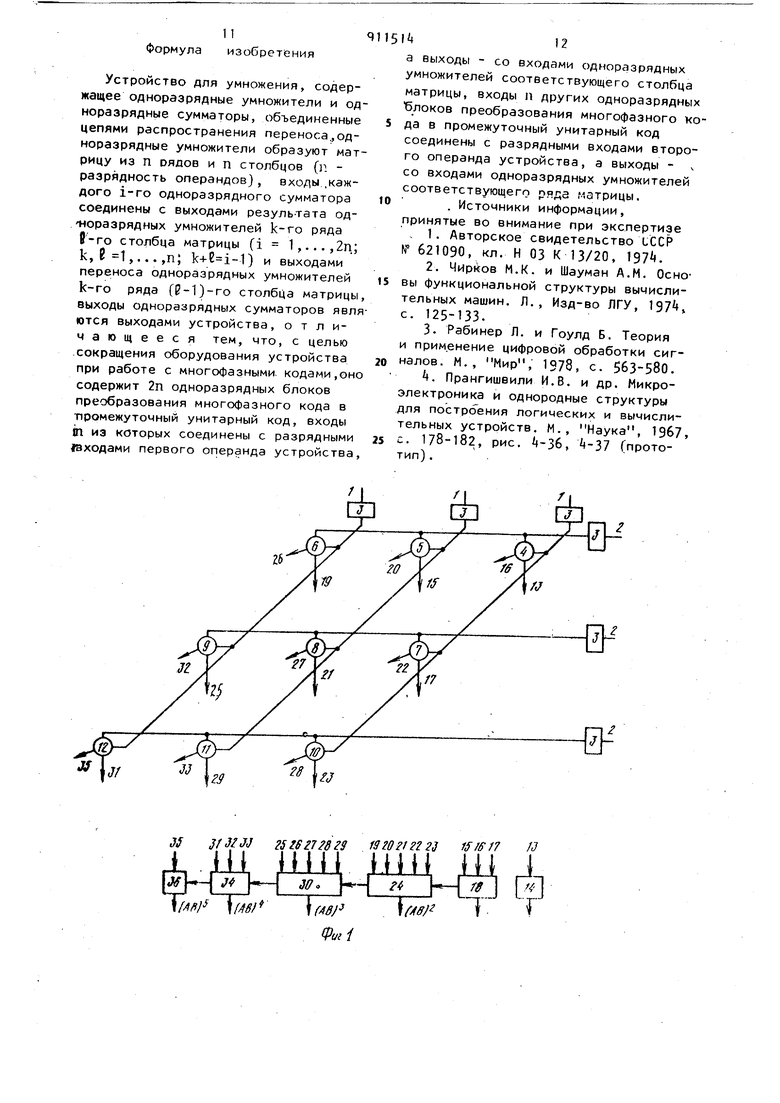

, fpt/f.9

Авторы

Даты

1982-03-07—Публикация

1979-08-28—Подача