Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля и управления для ввода информации от импульсных датчиков.

Целью изобретения является расширение области применения устройства за счет организации автономного циклического сбора информации и повышение надежности устройства.

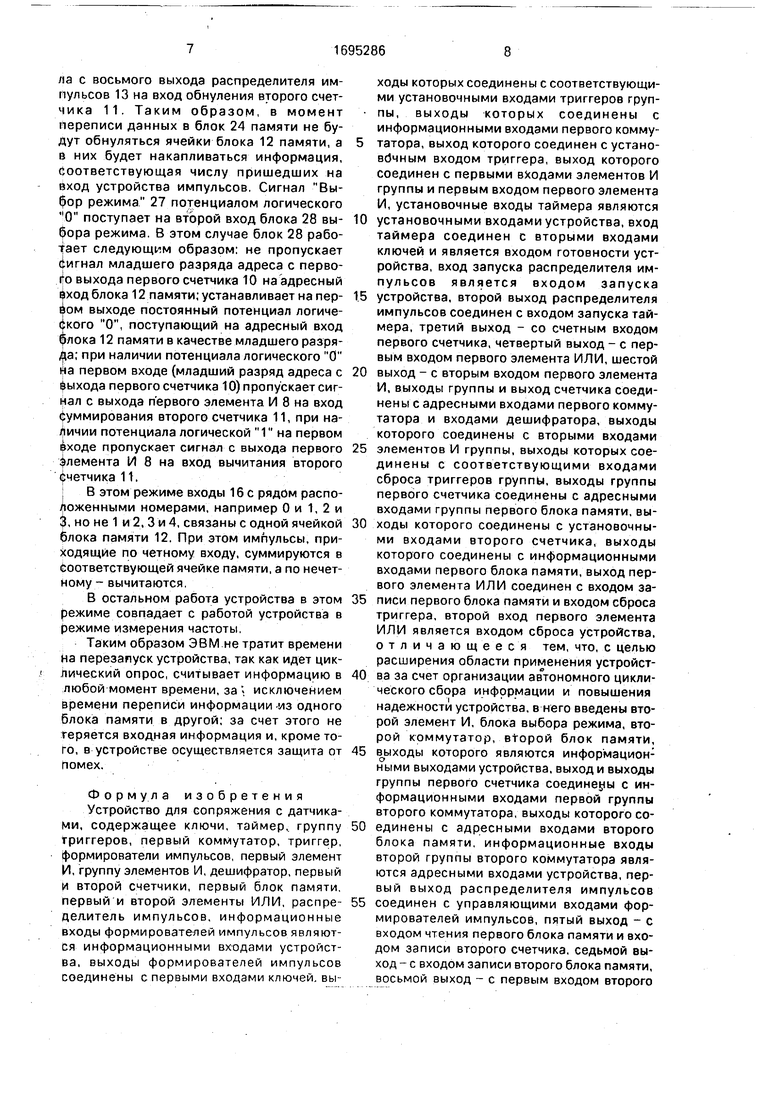

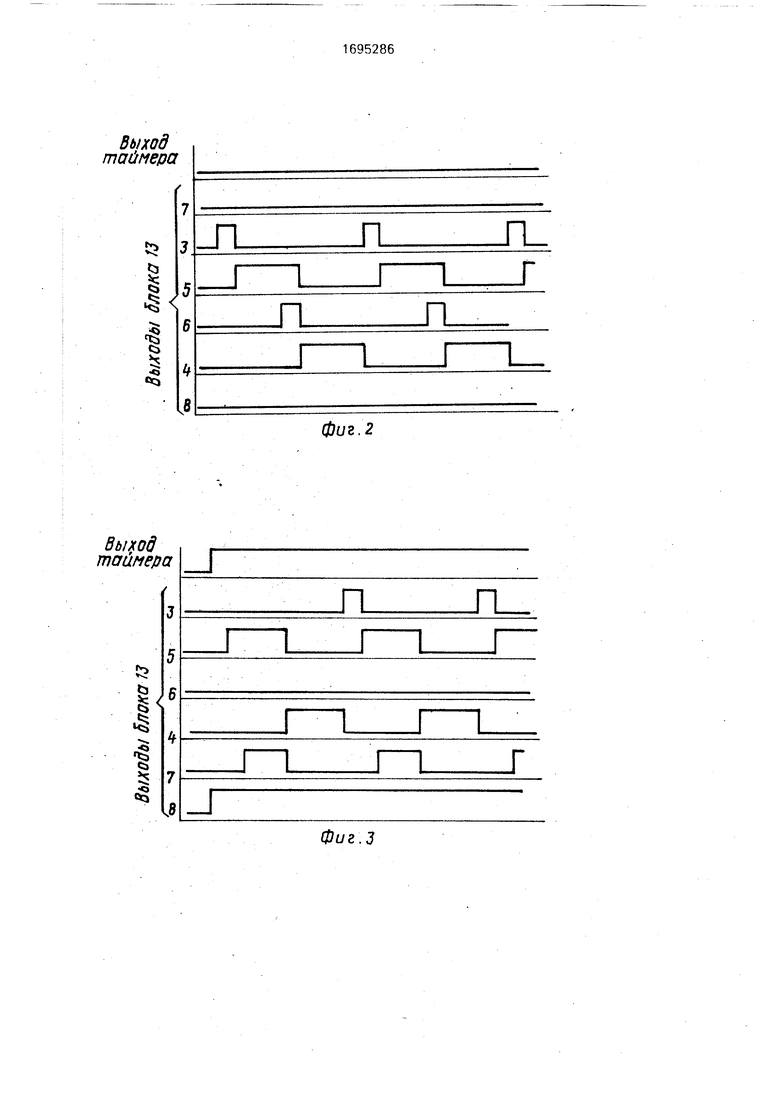

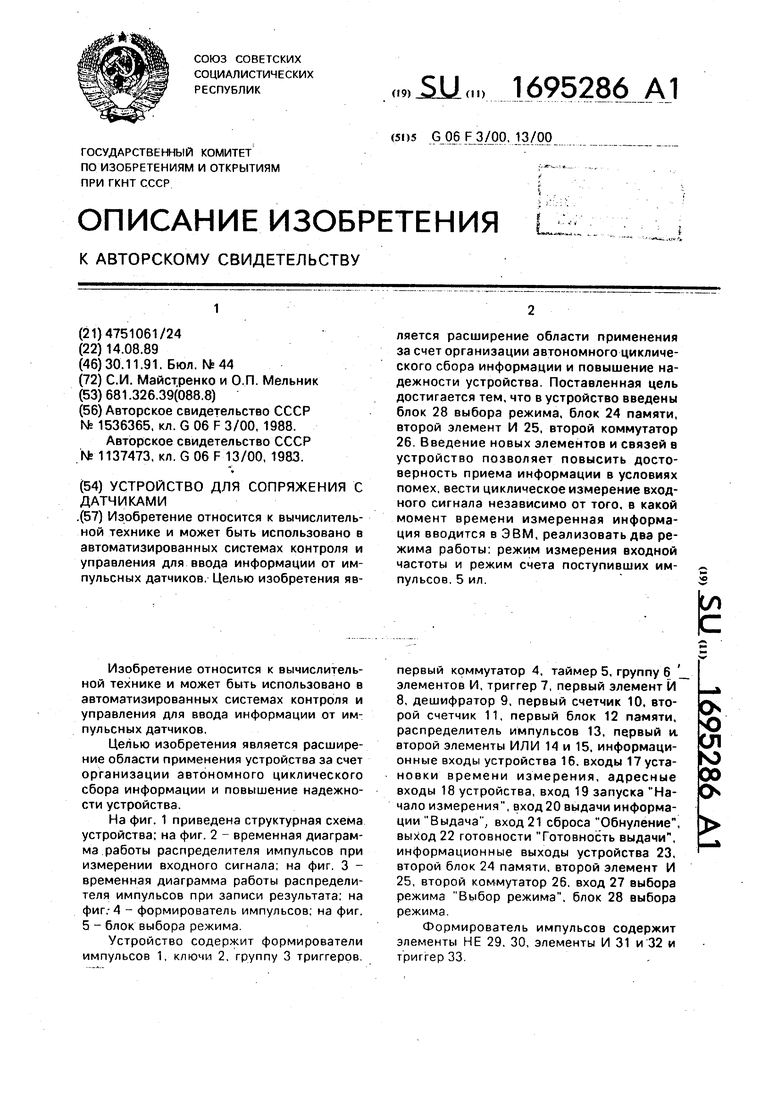

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временная диаграмма работы распределителя импульсов при измерении входного сигнала, на фиг. 3 - временная диаграмма работы распределителя импульсов при записи результата: на фиг.-4 - формирователь импульсов, на фиг. 5 - блок выбора режима

Устройство содержит формирователи импульсов 1, ключи 2, группу 3 триггеров

первый коммутатор 4, таймер 5, группу 6 элементов И, триггер 7, первый элемент И 8, дешифратор 9, первый счетчик 10. второй счетчик 11, первый блок 12 памяти, распределитель импульсов 13, первый и. второй элементы ИЛИ 14 и 15. информационные входы устройства 16, входы установки времени измерения, адресные входы 18 устройства, вход 19 запуска Начало измерения, вход 20 выдачи информации Выдача, вход 21 сброса Обнуление, выход 22 готовности Готовность выдачи, информационные выходы устройства 23, второй блок 24 памяти, второй элемент И 25, второй коммутатор 26. вход 27 выбора режима Выбор режима, блок 28 выбора режима

Формирователь импульсов содержит элементы НЕ 29. 30, элементы И 31 и 32 и триггер 33

С

ю ел

hO 00

О

Блок выбора режима содержит элементы И 34-38 и элемент ИЛИ 39.

Устройство работает следующим образом.

Устройство может работать в двух режимах: режим измерения частоты и режим подсчета числа входных импульсов,

В режиме измерения частоты на вход 27 подается сигнал логической 1, который поступает на вход запуска блока 28 выбора режима. В этом случае блок 28 выбора режима работает следующим образом: пропускает сигнал младшего разряда адреса с выхода первого счетчика 10 на адресный вход первого блока памяти 12, пропускает сигнал с выхода первого элемента И 8 на вход суммирования второго счетчика 11, выдает на вход вычитания второго счетчика 11 постоянный уровень, не изменяющий состояния этого счетчика.

В режиме измерения частоты на входах 17 устройства 6т ЭВМ устанавливается код, пропорциональный интервалу измерения. После этого на вход 19 Начало измерения подается сигнал логической 1, разрешающий работу распределителя 13, и потенциал логической 1 со второго выхода последнего поступает на управляющий вход таймера 5, запуская его. В результате этого на выходе таймера 5 появляется отрицательный импульс длительностью интервала измерения. Этот потенциал логического О коммутирует ключи 2 так, что выходы формирователей импульсов 1 оказываются подключенными к установочным входам триггеров группы 3.

Каждый формирователь импульсов обрабатывает парафазные входные сигналы, поступающие от датчиков. Передача информации отдатчиков в виде парафазных сигналов позволяет выделить полезный сигнал на фоне помех. Это свойство основано на том, что помеха наводится синфаз- но на оба входа, а формирователи импульсов 1 реагируют только на парафаз- ное измерение сигнала Входная логика каждого формирователя анализирует наличие логической 1 на прямом входе и логического О на инверсном входе. Первая же такая комбинация входных символов заставляет установиться выход триггера 33 рассматриваемого формирователя в состояние логической 1. В случае помехи по прямому входу сигнал логической 1 может измениться до логического О На инверсный вход наводится помеха той же полярности, следовательно, сигнал останется на уровне логического О. Такая комбинация не приводит к изменениям состояния триггера рассматриваемого формирователя импульсов. В определенный момент времени на прямом входе устанавливается сигнал логического О, а на инверсном - логической 1. Это приведет к

установке на выходе триггера 33 сигнала логического О. Если наводится помеха на установившиеся сигналы, то она, как в предыдущем случае, не влечет за собой измене- ния выходного состояния триггера

0 рассматриваемого канала. Все триггеры 33 стробируются сигналом Такт с первого выхода распределителя импульсов 13. Переход выхода триггера 33 из состояния логического О в логическую 1 устанавли5 вает на соответствующих выходах триггеров группы 3 потенциал логической 1.

Управление в режиме измерения осуществляется распределителем 13. Импульсом с третьего выхода распределителя 13

0 устанавливается на выходах первого счетчика 10 код, соответствующий двоичной записи номера измерительного канала. Этот код поступает на адресные входы первого коммутатора 4, второго коммута5 тора 26, дешифратора 9 и, с учетом логики работы блока выбора режима 28, на адресные входы блока оперативной памяти, В ре- зультате этого на выходе первого коммутатора 4 устанавливается потенци0 ал логического О, если в триггер группы 3 соответствующего канала прошел импульс, или логической 1, если импульса не было. Потенциалом логического О устанавливается уровень логической 1 на

5 выходе триггера 7. Этот уровень поступает на первый вход элемента И 8 и на вход элементов И группы 6, на втором входе элемента И группы 6. соответствующего ко мму- тируемого измерительному каналу,

0 установлен потенциал логической 1 с выхода дешифратора 9. При появлении двух логических 1 на входе элемента И блока 6 на выходе последнего устанавливается уровень логической 1, которым сбрасы5 вается соответствующий триггер группы 3. После установки в первом счетчике 10 кода номера измеряемого канала на пятом выходе распределителя 13 вырабатывается импульс, который поступает на вход Чте0 ние блока 12 и вход управления предустановкой второго счетчика 11. При этом содержимое ячейки блока 12, соответствующей измерительному каналу, номер которого установлен в первом счетчика 10,

5 заносится во второй счетчик 11. Затем на шестом выходе распределителя 13 вырабатывается импульс, который поступает на второй вход элемента И 8, и при наличии на первом его входе уровня логической 1 (если в измерительном канале зарегистрирован импульс) импульс с выхода элемента И 8 проходит через блок выбора режима 28 и увеличивает на 1 содержимое второго счетчика 11. Это новое значение заносится в ячейку блока 12 после того, как на его вход Запись с четвертого выхода распределителя 13 через элемент ИЛИ 14 поступит импульс, который одновременно сбросит триггер 7, после чего импульсом с третьего выхода распределителя 13 установится номер следующего канала, и цикл повторится. Таким образом, в интервале измерения происходит последовательный опрос измерительных каналов. Временная диаграмма работы распределителя импульсов 13 при измерении входного сигнала приведена на фиг. 2.

По окончании интервала измерения на выходе таймера 5 устанавливается уровень логической 1, сигнализирующий о том, что производится перепись полученной информации из блока памяти 12 в блок 24 памяти. Этот же сигнал переключает второй коммутатор 26 таким образом, что на адресный вход блока 24 памяти поступит информация с выхода первого счетчика 10. Распределитель импульсов 13 начинает формировать временную диаграмму импульсов, необходимую для переписи информации, накопленной в блоке 12 памяти, в блок 24 памяти. Временная диаграмма представлена на фиг. 3.

Первым вырабатывается сигнал Чтение на пятом выходе распределителя импульсов 13. В результате этого на выходе блока 12 памяти появится накопленная ин-, формация, соответствующая входному сигналу первого канала, которая поступает на вход данных блока 24 памяти. Через второй коммутатор 26 на адресные входы блока 24 памяти поступает адрес с первого счетчика 10. Затем вырабатывается импульс на седьмом выходе распределителя импульсов 13, во время которого производится перепись информации по установленному адресу из блока 12 памяти в блок 24 памяти. После прихода на первый вход распределителя импульсов 13 логической 1 на его восьмом выходе вырабатывается сигнал Обнуление счетчика, который проходит через второй элемент И 25 и второй элемент ИЛИ 15 и поступает на вход сброса второго счетчика 11. В результате, на выходе второго счетчика 11 будет присутствовать уровень логического О, который поступает на вход блока 12 памяти. После того, как произведена перепись информации в блок 24 памяти, снимаются сигналы с пятого и седьмого выходов распределителя импульсов 13, а на его четвертом выходе формируется импульс. Под действием этого импульса производится запись нулевой информации с выхода второго счетчика 11 в блок 12 памяти. Та- 5 ким образом производится подготовка ячейки памяти для следующего цикла измерения. Затем формируется импульс на третьем выходе распределителя импульсов 13, который поступает на счетный вход 0 первого счетчика 10, заставляя его перейти в новое состояние. Новый адрес с выхода первого счетчика 10 поступает на вход блока 12 памяти и через коммутатор 26 на вход блока 24 памяти. Далее все повторя5 ется сначала. Так происходит до тех пор, пока не будет переписана вся информация из блока 12 памяти в блок 24 памяти. При этом все ячейки блока 12 будут обнулены. По окончании этого процесса на втором выходе

0 распределителя импульсов 13 появляется импульс, запускающий таймер 5. Распределитель импульсов 13 начинает формировать последовательность импульсов измерительного интервала (фиг. 2), рассмотренного

5 выше.

Информация, хранимая в блоке 24 памяти, может быть прочитана ЭВМ в любое время, за исключением момента, когда производится перепись новой информации из

0 блока 12 памяти в блок 24. Поэтому перед началом чтения информации ЭВМ должна проанализировать состояние на выходе устройства Готовность выдачи 22 на наличие логического О. Если на указанном выходе

5 присутствует логическая 1, то следует дождаться окончания переписи новой информации в блок 24 памяти.

При чтении информации ЭВМ на входах 18 устанавливается код-номер измери-.

0 тельного канала, а на входе 20 - потенциал логической 1. При этом на выходе второго коммутатора 26 устанавливается код- номер канала,который поступает на вход блока 24. В результате этого на выходах

5 23 устанавливается выводимая информация.

При обнулении блока 12 оперативной памяти ЭВМ выставляет потенциал логической 1 на вход 21 Обнуление. Этот по0 тенциал сбрасывает второй счетчик 11 и через первый элемент ИЛИ 14 поступает на вход Запись блока 12, в результате чего в последний записывается О.

Признаком работы устройства в режиме

5 подсчета входных импульсов является наличие потенциала логического О на входе Выбор режима 27, который поступает на второй вход второго элемента И 25.

Наличие потенциала логического О на этом входе запрещает прохождение сигнапа с восьмого выхода распределителя импульсов 13 на вход обнуления второго счетчика 11. Таким образом, в момент переписи данных в блок 24 памяти не будут обнуляться ячейки блока 12 памяти, а в них будет накапливаться информация, соответствующая числу пришедших на вход устройства импульсов. Сигнал Вы- фор режима 27 потенциалом логического О поступает на второй вход блока 28 выбора режима. В этом случае блок 28 работает следующим образом: не пропускает Сигнал младшего разряда адреса с первого выхода первого счетчика 10 на адресный $ход блока 12 памяти; устанавливает на первом выходе постоянный потенциал логического О, поступающий на адресный вход рлока 12 памяти в качестве младшего разряда; при наличии потенциала логического О на первом входе (младший разряд адреса с фыхода первого счетчика 10) пропускает сигнал с выхода первого элемента И 8 на вход Суммирования второго счетчика 11, при наличии потенциала логической 1 на первом $ходе пропускает сигнал с выхода первого флемента И 8 на вход вычитания второго фчетчика 11.

В этом режиме входы 16 с рядом расположенными номерами, например 0 и 1, 2 и 3, но не 1 и 2, 3 и 4, связаны с одной ячейкой блока памяти 12. При этом импульсы, приходящие по четному входу, суммируются в соответствующей ячейке памяти, а по нечетному - вычитаются.

В остальном работа устройства в этом режиме совпадает с работой устройства в режиме измерения частоты.

Таким образом ЭВМ не тратит времени На перезапуск устройства, так как идет циклический опрос, считывает информацию в любой момент времени, за исключением Времени переписи информации-из одного блока памяти в другой; за счет этого не теряется входная информация и, кроме того, в устройстве осуществляется защита от Помех.

Формула изобретения Устройство для сопряжения с датчика- Ми, содержащее ключи, таймер, группу триггеров, первый коммутатор, триггер, формирователи импульсов, первый элемент И, группу элементов И, дешифратор, первый и второй счетчики, первый блок памяти, первый и второй элементы ИЛИ, распре- деяитель импульсов, информационные входы формирователей импульсов являются информационными входами устройства, выходы формирователей импульсов соединены с первыми входами ключей, выходы которых соединены с соответствующими установочными входами триггеров груп- пы, выходы которых соединены с информационными входами первого коммутатора, выход которого соединен с устано- вбчным входом триггера, выход которого соединен с первыми входами элементов И группы и первым входом первого элемента И, установочные входы таймера являются

0 установочными входами устройства, вход таймера соединен с вторыми входами ключей и является входом готовности устройства, вход запуска распределителя импульсов является входом запуска

5 устройства, второй выход распределителя импульсов соединен с входом запуска таймера, третий выход - со счетным входом первого счетчика, четвертый выход - с первым входом первого элемента ИЛИ, шестой

0 выход - с вторым входом первого элемента И, выходы группы и выход счетчика соединены с адресными входами первого коммутатора и входами дешифратора, выходы которого соединены с вторыми входами

5 элементов И группы, выходы которых соединены с соответствующими входами сброса триггеров группы, выходы группы первого счетчика соединены с адресными входами группы первого блока памяти, вы0 ходы которого соединены с установочными входами второго счетчика, выходы которого соединены с информационными входами первого блока памяти, выход первого элемента ИЛИ соединен с входом за5 писи первого блока памяти и входом сброса триггера, второй вход первого элемента ИЛИ является входом сброса устройства, отличающееся тем, что, с целью расширения области применения устройст0 ва за счет организации автономного циклического сбора информации и повышения надежности устройства, в него введены второй элемент И, блока выбора режима, второй коммутатор, Btopou блок памяти,

5 выходы которого являются информационными выходами устройства, выход и выходы группы первого счетчика соединены с информационными входами первой группы второго коммутатора, выходы которого со0 единены с адресными входами второго блока памяти, информационные входы второй группы второго коммутатора являются адресными входами устройства, первый выход распределителя импульсов

5 соединен с управляющими входами формирователей импульсов, пятый выход - с входом чтения первого блока памяти и входом записи второго счетчика, седьмой выход - с входом записи второго блока памяти, восьмой выход - с первым входом второго

элемента И, второй вход первого элемента ИЛИ объединен с первым входом второго элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, выход первого элемента И соединен с информационным входом блока выбора режима, первый выход которого соединен с адресным входом первого блока памяти, второй выход - с суммирующим входом второго счетчика, а третий выход - с бычитающим входом второго счетчика, выход первого счетчика соединен со стробирующим входом блока

0

выбора режима, выходы первого блока памяти соединены с информационными входами второго блока памяти, вход чтения которого является входом выдачи информации устройства, управляющий вход блока выбора режима и второй вход второго элемента И являются входом выбора режима устройства, выход второго элемента И подключен к второму входу второго элемента ИЛИ, выход таймера соединен с управляющим входом распределителя импульсов и адресным входом второго коммутатора.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СПОСОБ АНДРЕЕВА О.А. УПРАВЛЕНИЯ ФОРМИРОВАНИЕМ ПОДСВЕТКИ УЧЕБНЫХ ТЕКСТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2020874C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ФОРМИРОВАНИЕМ ПОДСВЕТКИ УЧЕБНЫХ ТЕКСТОВ ПО ТАБЛИЦАМ АНДРЕЕВА ПРИ РАЗВИТИИ НАВЫКОВ СВЕРХБЫСТРОГО ВОСПРИЯТИЯ ИНФОРМАЦИИ | 1993 |

|

RU2042214C1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

фиг. 2

Фиг.З

Прямой

29

Инверсный

Ш

Тактовый импульс с первого выхода блока /3

ФигЛ

Вход 27

К

С выхода блокад

35

С первого выходалл блока 10

Фиг. 5

3/

К 5л оку 2

зз

32

К

На вход суммирования 11

На выход

вычитания блока 11

На вход младшего разряда адреса

бУгока оператив- ной памяти

| Устройство для ввода информации | 1988 |

|

SU1536365A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения с датчиками | 1983 |

|

SU1137473A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-08-14—Подача