разования, каждый из которых включает в себя инвертор 8, элементы 9, 10 НЕ, триггеры 11-14, формирователи 15-17 импульсов, элементы 18-23 ИЛИ, элементы 24-27 И, счетчики 28, 29, буферный регистр 30 и блок 31 оперативной памяти. Введение в каждом канале 7 блока 31 оперативной памяти, в который постоянно записывается заранее заданное от контроллера 6 через буферный регистр 30 и счетчик 29 число N слов, преобразованных из

1

Изобретение относится к вычислительной технике и может быть использовано в системах сбора, обработки и передачи информации.

Цель изобретения - расширение об- ласти применения путем обеспечения биполярного кода в двоичный и повышение информативности.

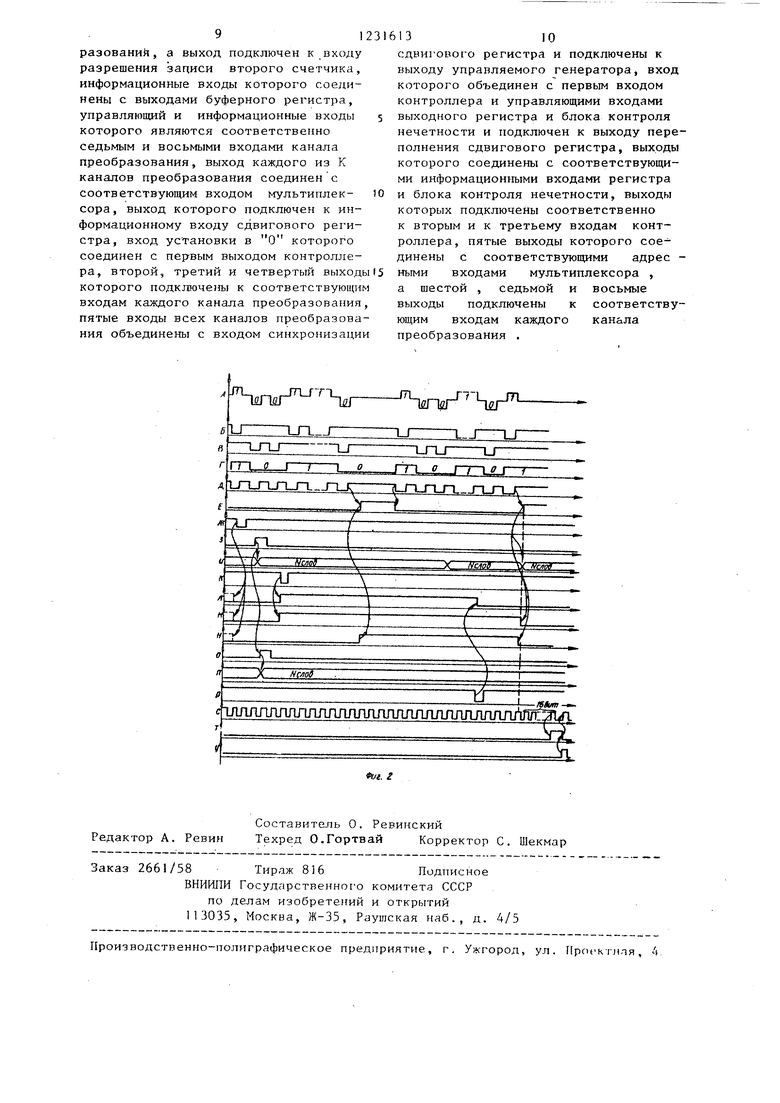

На фиг. 1 изображена функциональная схема предлагаемого преобразова- теля; на фиг. 2 - диаграммы, иллюстрирующие его работу.

Преобразователь последовательного кода в параллельный содержит управляемый генератор 1, мультиплексор 2, сдвиговый регистр 3, блок 4 контроля Иечетности, регистр 5, контроллер 6 и К каналов 7 преобразования, каждый из которых содержит инвертор 8, пер- вьй 9 и второй 10 элементы НЕ, пер- вый 11, второй 12, третий 13 и четвертый 14 триггеры, первый 15, второ 16 и третий 17 формирователя импульсов, первый 18, второй 19, третий 20 четвертый 21, пятый 22 и шестой 23 элементы ИЛИ, первый 24, второй 25, третий 26 и четвертый 27 элементы И, первый 28 и второй 29 счетчики, буферный регистр 30 и блок 31 оперативной памяти.

Информационный (первый) вход 32 каждого канала 7 преобразования сое- динен через первый элемент НЕ 9 с пербыми входами первых триггера 11 и элемента ИЛИ 18, а через соединен- ные последовательно инвертор 8 и второй элемент НЕ 10 - с вторыми входами первых триггера 11 и элемента

биполярного кода триггером 12, и объединение выходов блоков 31 всех каналов 7 с помощью мультиплексора 2, управляемого контроллером 6 (например, в стандарте КАМАК), позволило организовать преобразование последовательного биполярного кода в последовательный двоичный код сразу в нескольких каналах 7 и выводить результат такого преобразования из любого канала 7 в параллельном виде. 2 ил.

ИЛИ 18. Выход первого триггера 11 подключен к информационному входу блока .31 оперативной памяти, выход которого является выходом канала 7. Выход первого элемента ИЛИ 18-соединен с первым входом третьего элемента И 26 и входом первого формирователя 15 импульсов, выход которого подключен к первым входам первого 24 и второго 25 элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами второго триггера 12. Его первый вход установки в О является вторым входом канала 7, вход установки в 1 объединен с таким же входом четвертого триггера 14 и подключен к выходу второго элемента ИЛИ 19, первый вход которого является третьим входом канала 7. Второй вход установки в О второго триггера 12 объединен с первым входом установки в О четвертого триггера 14, первыми входами четвертого 21 и пятого 22 элементов ИЛИ и подключен к четвертому входу канала 7, выход первого элемента И 24 соединен с входом установки в 1 третьего триггера 13, прямой выход которого подключен к второму входу третьего элемента И 26, выход второго элемента И 25 соединен с первым входом второго формирователя I6 импульсов и первым входом установки в О четверто го триггера 14,.второй вход установки в О которого соединен с выходом четвертого элемента ИЛИ 21. Прямой выход четвертого триггера 14 подключен к третьему входу третьего элемента И 26,а инверсный выход соединен с управляющим входом блока оперативной памяти и первым входом четвертого элемента И 27, второй вход которого является пятым входом канала 7, Вьгхо- ды элементов И 26 и 27 соединены с входами третьего элемента ИЛИ 20, выход которого подключен к счетному входу первого счетчика 28, вход установки в О которого соединен с выходом пятого элемента ИЛИ 22. Выходы первого счетчика 28 подключены к адресным входам блока 31 оперативной ламяти, при этом выход счетчика 28 под номером r logjn, где п - разрядность преобразуемых слов, соединен со счетным входом второго счетчика 29. Выход последнего соединен с входом третьего формирователя 17 импульсов, выход которого подключен к вто- рому входу установки в О третьего триггера 13, вторым входом второго 19 и четвертого 21 элементов ИЛИ и второму входу второго формирователя 16 импульсов, выход которого соединен с вторым входом пятого 22 и первым входом шестого 23 элементов ИЛИ. Второй вход шестого элемента ИЛИ 23 является шестым входом канала 7, а выход подключен к входу раэрешения записи второго счетчика 29. Информационные входы счетчика 29 соединены с выходами буферного регистра 30, управляющий и информационные входы которого являются седьмым и восьмыми входами канала 7. Выходы всех каналов 7 преобразования соединены с со- ответствуюп1ими входами мультиплексора 2, выход которого подключен к информационному входу сдвигового реги- стра 3, вход установки в О которого соединен с первым выходом контроллера 6, пятые выходы которого подключены к адресным входам мультиплексора 2, а остальные выходы контроллера 6 соединены с соответствующими входами всех каналов 7. Пятые входы всех каналов 7 объединены с входом .синхронизации сдвигового регистра 3 и подключены к выходу управляемого renepaтора 1, вход которого объединен с первым входом контроллера 6 и управляющими входами блока 4 контрол я нечетности и выходного регистра 5 и подключен к выходу переполнения сдвигающего регистра 3, Выходы разрядов последнего соединены с информационными входами выходного регистра 5 и

5 О 5 0 5 О 0 g з

5

блока 4 контроля нечетности, выходы которых являются вторыми и третьим входами контроллера 6.

Преобразователь последовательного кода в параллельный работает следующим образом.

Входной информацией для преобразования является последовательный биполярный код, который поступает на вход 32 канала 7 (фиг. 2А). Первый элемент НЕ 9 выделяет единичную информацию из биполярного сигнала (фиг. 2Б). Входной сигнал, проинвер- тированный в инверторе 8, поступает на второй элемент НЕ 10, который выделяет нулевую информацию из биполярного сигнала (фиг. 2В). На выходе первого триггера 1I происходит образование последовательного двоичного кода, несущего ту же информацию (фиг. 2Г), что и биполярный код. Первый элемент ИЛИ 18 выделяет синхроимпульсы (фиг. 2Д). Так как входной код представляет .из себя последовательность п-разрядных слов, разделенных между собой паузами длительностью m тактов, то для однозначного преобразования входного кода в двоичный необходимо формировать сигнал, определяющий паузы между словами (например, код, имеет и ). Для этого из синхроимпульсов (фиг. 2Д) первый формирователь 15 выделяет паузу (фиг. 2Е).

Процесс преобразования- происходит в два этапа. На первом этапе происходит запись параллельно по всем каналам 7 в блоки 31 информации по управляющим сигналам, полученным через интерфейс (например, интерфейс КАМА.К) ,от контроллера 6. Чтение информации с преобразованием ее в параллельный (например, шестнадцатиразрядный) код осуществляется на втором этапе.

Перед началом работы соответствующим сигналом с четвертого выхода контроллера 6 (фиг. 2Ж) устанавливают в исходное положение триггеры 12-14 (через элемент ИЛИ 21) и первый счетчик 28 (через элемент ИЛИ 22). Затем преобразователь настраивается на число N принимаемых слов по каждому каналу 7. По сигналу с седьмого выхода контроллера 6 (фиг. 23) соответст- вукицая этому числу N информация с восьмых выходов контроллера 6 по шине данных записывается в буферный регистр 30 (фиг, 2И), затем по сигналу

с шестого выхода контроллера 6 (фиг. 20) данные из буферного регистра 30 переписываются во второй счетчик 29 (фиг. 2П). Таким образом, на счетчике 29 будет информация о количестве N слов преобразования в каждом канале 7 По сигналу с третьего выхода от контроллера 6, являющемуся пусковой командой (фиг. 2К), тригге- ры 12 и 14 устанавливаются в I (фиг. 2Л и 2М) через второй элемент ИЛИ 19. С приходом паузы сигнал с первого формирователя 15 (фиг. 2Е) поступает на первый злемент И 24. Благодаря этому, учитывая разрешение от триггера 12, устанавливается в 1 триггер 13. Таким образом, триггер I4 запрещает импульсы от управ- ляемого генератора 1 на четвертом элементе И 27 и разрешает вместе с триггером 13 синхроимпульсы С первог элемента ИЛИ 18 на третьем элементе И 26. Синхроимпульсы (фиг. 2Д) через третий элемент ИЛИ 20 отсчитывают ад реса ячеек памяти блока 31 с помощью счетчика 28. Выход пятого разряда (в случае ) счетчика 28 заводится на синхровход счетчика 28, работающего на вычитание. Таким образом, когда в блок 31 запишется заранее заданное (занесенное в регистр 30) число N слов, счетчик 29 вырабатывае сигнал переполнения. По этому сигнал импульс с третьего формирователя I7 сбрасывает триггер 13 (через элемент ИЛИ 19), подтверждает установку триггера 12 и формирует одиночный импуль на втором формирователе 16, который в свою очередь через элемент ИЛИ 22 сбрасывает счетчик 28 в исходное состояние и через элемент ИЛИ 23 вновь настраивает счетчик на число N слов. Пауза с первого формирователя 15 вновь устанавливает триггер 13 в 1 Весь цикл записи повторяется для сло по тем же адресам ячеек памяти блока 31. Режим записи устанавливается сигналом с инверсного выхода триггера 14. ,

Когда необходимо считать информацию с какого-то канала 7, с второго выхода контроллера 6 вырабатывается сигнал, поступающий только в данный канал 7 (фиг. 2Р), По этому сигналу триггер 12 сбрасывается, но з.апись слова в память продолжается до его окончания. По командной части этого

сигнала вырабатывается сигнал на первом выходе контроллера 6, который устанавливает сдвиговый регистр 3 в исходное состояние.

С приходом паузы импульс с формирователя 15 через элемент И 25 сбрасывает триггер 14, тем самым подключая управляемый генератор 1 к синхро- входу счетчика 28 вместо синхроимпульсов с элемента ИЛИ 18. Этим же сигналом с выхода элемента И 25 запускается формирователь 16 импульсов который через элемент ИЛИ 22 сбрасывает счетчик 28 в исходное состояние а через элемент ИЛИ 23 устанавливает на счетчике 29 число N считываемых из блока 31 слов, триггер 14 единичным сигналом на своем инверсном выходе устанавливает режим считывания для блока 31 .- При обращении к данному каналу 7 для чтения из сигнала контроллера 6 вьщеляется ее адресная часть-(в структуре интерфейса КАМАК) и с пятых выходов контроллера 6 подается на мультиплексор 2 для выбора канала 7. Импульсы с генератора 1 перебирают с помощью счетчика 28 адреса ячеек памяти в блоке 31. Параллельно эти импульсы подаются на синхровход сдвигового регистра 3, на выходе данных которого появляется синхронно информация из ячеек памяти блока 31 через мультиплексор 2. Таким образом, информация последовательно сдвигается в регистре 3. Когда шестнадцать тактовых импульсов устанавливают Hd шестнадцати выходах регистра 3 параллельный выходной код (фиг. 2с), на выходе переполнения регистра 3 появляется сигнал, индицирующий з авершение преобразования .шестнадцати разрядов. Этот сигнал блокирует управляемый генератор 1 и, поступая на первый вход контроллера 6, сигнализирует (например, через интерфейс КАМАК) либо о готовности к считыванию, либо о прерывании основной пpoгpaм ftl для считывания этог кода (фиг. 2Т). На первом выходе контроллера 6 появляется команда Чтение (фиг. 2У), которая сбрасывает сдвиговый регистр 3 в исходное состояние и считывает шестнадцатиразрядное слово из выходного регистра 5. Индицирующий импульс с выхода переполнения регистра 3 фиксирует информацию в выходном регистре 5 и

блоке 4 контроля нечетности. Если произошел c6ofi по нечетности, то блок i контроля вырабатывает сигнал прерывания и подает его на третий вход контроллера 6, Как только сдви- говый регистр 3 устанавливается в исходное состояние, снимается блокировка с управляемого генератора 1, следующие шестнадцать бит преобразуются и считываются на вторые входы контроллера 6. Когда считается последнее слово, фомирователь 17 импульсов своим выходным сигналом чере элементы ИЛИ 9 и 21 и формирователь 16 импульсов устанавливает канал 7 для продолжения записи в блок 31.

Форму л-а изобретения

Преобразователь последовательного кода в параллельный, содержащий управляемый генератор, сдвиговый регистр, блок контроля нечетности и первый канал преобразования, состоящий из первого и второго триггеров, первого и второго элементов И и первого счетчика, отличающий- с я тем, что, с целью расширения области применения путем обеспечения преобразования биполярного кода в двоичньй и повьшения информативности в него введены мультиплексор, регист и контроллер, в первый канал преобразования - третий и четвертый триггеры, второй счетчик, блок оперативной памяти, буферный регистр, первый, второй и третий формирователи импульсов, третий и четвертый элементы И, элементы ИЛИ с первого по шестой, первый и второй элементы НЕ и инвер- тор, и К-1 аналогично первому вьтол- ненных каналов преобразования, в каждом из которых вход инвертора объединен с входом первого элемента НЕ и подключен к первому входу канала преобразования, выход первого элемента НЕ соединен с первыми входами первых триггера и элемента ИЛИ, выход инвертора через второй элемент НЕ подключен к вторым входам первых триггера и элемента ИЛИ, выход первого триггера соединен с информационным входом блока с)перативной памяти, выход которого является выходом первого канала преобразования, выход первого элемента ИЛИ подключен к первому входу третьего элемента И и входу первого формирователя импуль0

0 0 5 5

сов, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам второго триггера, первый вход установки в О которого является вторым входом канала преобразования, входы установки в 1 второго и четвертого триггеров объединены и подключены к выходу второго элемента ИЛИ, первый вход которого является третьим входом канала преобразования, второй вход установки в О второго и первый вход установки в О третьего триггеров объединены с первыми входами четвертого и пятого элементов ИЛИ и подключены к четвертому входу канала преобразования, выход первого элемента И соединен с входом установки в 1 третьего триггера, прямой выход которого подключен к второму входу третьего элемента И,выход второго элемента И соединен с первым входом второго формирователя импульсов и первым входом установки в О четвертого триггера, второй вход установки в О которого подключен к выходу четвертого элемента ИЛИ, прямой выход соединен с третьим входом третьего элемента И, а инверсный - с управляющим входом блока оперативной памяти и первым входом четвертого элемента И, второй вход которого является пятым входом канала преобразования, выходы третьего и четвертого элементов И подключены к входам третьего элемента ИЛИ, выход которого соединен с счетным входом первого счетчика, вход установки в О которого подключен к выходу пятого элемента ИЛИ, выходы первого счетчика соединены с адресными входами блока оперативной памяти, выход первого счетчика с номером г , где п - разрядность преобразуемого слова, соединен с счетньгм входом второго счетчика, выход которого подключен ко входу третьего формирователя импульсов, выход которого соединен с вторым входом установки в О третьего триггера, вторыми входами второго и четвертого элементов ИЛИ и вторым входом второго формирователя импульсов, выход которого подключен к второму входу пятого элемента ИЛИ и первому входу шестого элемента ИЛИ, второй вход которого является щеетым входом канала преоб912

разований, а выход подключен к входу разрешения записи второго счетчика, информационные входы которого соединены с выходами буферного регистра, управляющий и информационные входы которого являются соответственно седьмым и восьмыми входами канала преобразования, выход каждого из К каналов преобразования соединен с соответствующим входом мультиплек- сора, выход которого подключен к информационному входу сдвигового регистра, вход установки в О которого соединен с первым выходом контроллера, второй, третий и четвертый выходы которого подключены к соответствующим входам каждого канала преобразования, пятые входы всех каналов преобразования объединены с входом синхронизации

Редактор А. Ревин

Составитель О. Ревинский

Техред О.Гортвай Корректор С. Шекмар

Заказ 2661/58 Тираж 816Подписное

ВНИИ1ТИ Государственног о комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Прси кт лля, А

1310

сдвигового регистра и подключены к выходу управляемого генератора, вход которого объединен с первым входом контроллера и управляющими входами выходного регистра и блока контроля нечетности и подключен к выходу переполнения сдвигового регистра, выходы которого соединены с соответствующими информационными входами регистра и блока контроля нечетности, выходы которых подключены соответственно к вторым и к третьему входам контроллера, пятые выходы которого соединены с соответствующими адрес - ньгми входами мультиплексора , а шестой , седьмой и восьмые выходы подключены к соответствующим входам каждого канала преобразования .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1438007A2 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1510099A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1453598A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к вычислительной технике и может быть использовано В системах сбора, обработки и передачи информации. Изобретение ПОЗВОЛИТ расширить область применения путем обеспечения преобразвования биполярного кода в двоичный и повысить информативность. Преобразователь содержит управляемый генератор 1 мультиплексор 2, сдвиговый регистр 3,, блок 4 контроля нечетности, регистр 5, контроллер 6 и К каналов 7 преоб(Л

| Патент США № 4274085, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-06-28—Подача