«

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство адресации памяти | 1988 |

|

SU1575188A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Кодер | 1987 |

|

SU1474855A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство контроля линейных цифровых систем | 1987 |

|

SU1425681A1 |

Изобретение относится к электросвязи и может использоваться для кодирования цифровой информации избыточным кодом Хемминга. Устройство формирует корректирующий код для двоичного цифрового сигнала параллельно-последовательным кодом, что повышает быстродействие устройства. Формирователь содержит счетчик 1 (импульсов), сумматоры 2, 3 по модулю два, элементы 4,11 задержки, группу 5 элементов И, группы 6, 7 триггеров, элемент ИЛИ 8, триггер 9 и блок 10 постоянной памяти. 2 ил. 1 табл.

Os

О

ел ел

ел

Изобретение относится к электросвязи и может использоваться в кодерах и декодерах цифровых систем передачи информации.

Цель изобретения - повышение быстродействия формирователя.

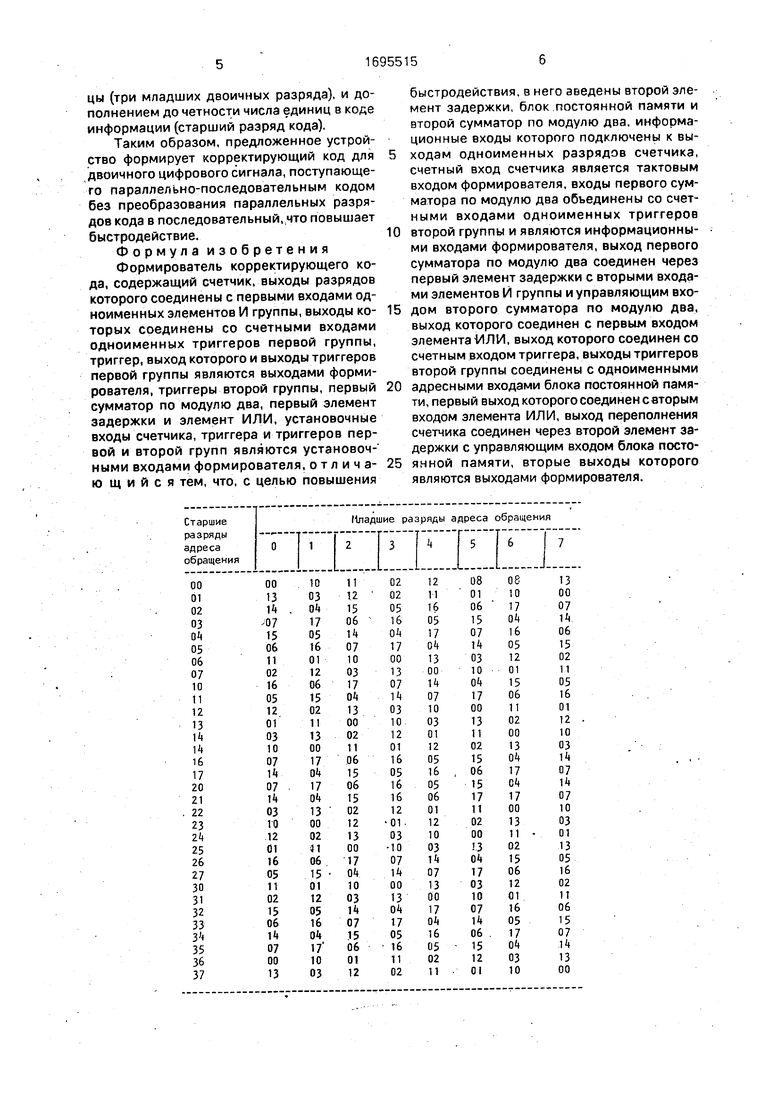

На фиг. 1 и 2 приведены функциональная схема формирователя и временные диаграммы сигналов, поясняющие его работу. Формирователь содержит (фиг. 1) счетчик 1 импульсов, первый и второй сумматоры 2, 3 по модулю два, первый элемент А задержки, группу 5 элементов И, первую, вторую группы 6, 7 триггеров, элемент ИЛИ 8, триггер 9, блок 10 постоянной памяти и второй элемент 11 задержки.

На фиг. 2 приведены диаграммы сигнала ввода информации (байта) в устройство (фиг. 2а), последовательность состояний двоичного счетчика 1 (фиг. 26), моменты возможного появления сигнала на выходе элемента 4 задержки (фиг. 2 в), сигнал на выходе элемента 11 задержки (фиг. 2 г), последовательность изменений состояний триггеров первой группы 6 (фиг. 2 д), послег- довательность изменений состояний триггеров второй группы 7 (фиг. 2 е) и момент появления сигналов на выходах блока 10 постоянной памяти.

Устройство (фиг. 1) обеспечивает формирование корректирующего кода Хеммин- га с кодовым расстоянием d А при побайтно-последовательном поступлении информации.

Устройство работает циклами, перед началом каждого цикла счетчик 1 и триггеры первой и второй групп 6 и 7 устанавливаются в нулевое состояние. При поступлении первого байта информации значение этого байта записывается на триггерах группы 7, а в сумматоре 2 производится суммирование значений всех разрядов байта по mod 2. Одновременно тактовый импульс, поступающий на вход счетчика 1, переводит счетчик 1 в очередное (первое) состояние. В соответствии с состоянием счетчика 1 происходит коммутация группы 5 элементов .И, а в сумматоре 3 образуется сумма по mod 2 значений разрядов счетчика 1.

Если сумма значений разрядов байта информации, сформированная в сумматоре 2, нечетна, то по сигналу с выхода сумматора 2, задержанному на элементе 4, код счетчика 1 через группу 5 элементов И и с выхода сумматора 3 переносится соответственно на триггеры группы 6 и триггер 9. Время задержки на элементе 4 обеспечивает завершение переходных процессов в счетчике 1 и-сумматоре 3. С приходом каж- ного следующего байта информации работа

, формирователя повторяется. При этом на триггерах групп б и 7 происходит поразрядное суммирование по mod 2 поступающих сигналов с накопленными на них результатами.

После прохождения последнего байта информации на выходе переполнения счетчика 1 формируется сигнал, который поступает после задержки в элементе 11 на время

0 завершения переходных процессов в устройстве, на управляющий вход блока 10 постоянной памяти. На выходах блока 10 появляется кодовый сигнал, выбираемый по адресу, определяемому текущим состояни5 ем триггеров группы 7.

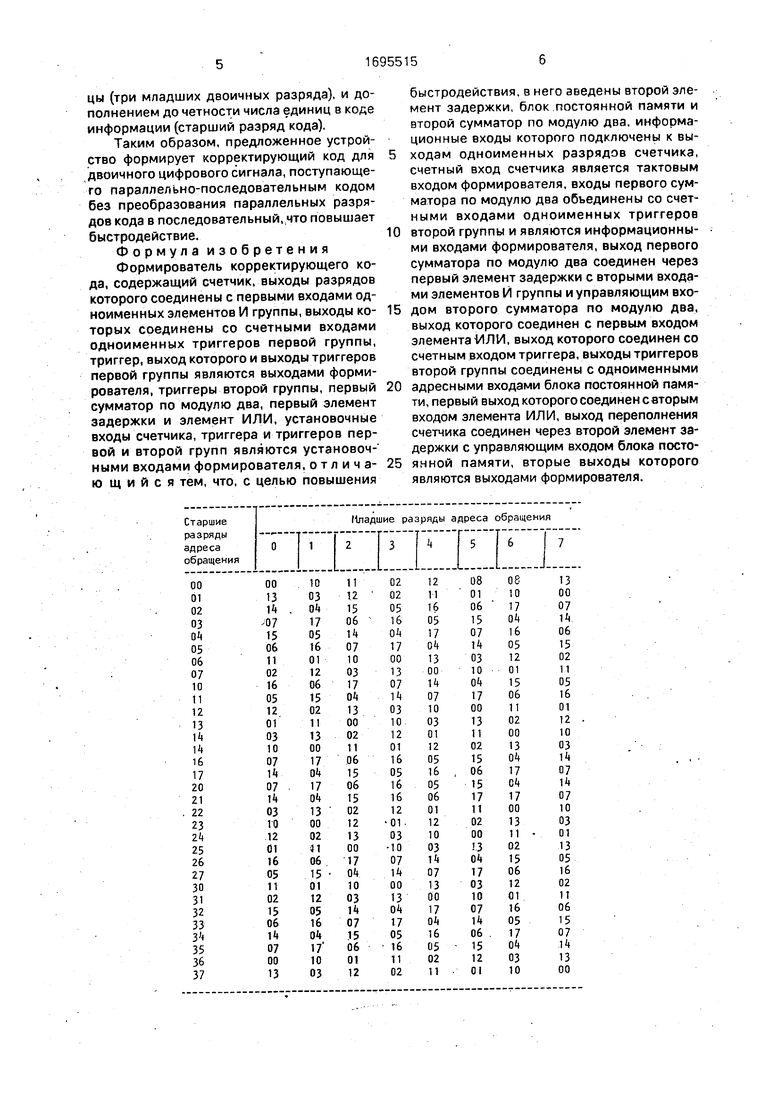

Коды, хранимые в блоке 10 постоянной памяти, приведены в таблице.

Кодовый сигнал, соответствующий значению старшего разряда кода, поступивший

0 на выход блока 10, проходит через элемент ИЛИ 8 на счетный вход триггера 9, где происходит его суммирование с ранее накопленным результатом. В итоге на выходах группы 6 триггеров и триггера 9, являющих5 ся выходами устройства, будет сформирована первая часть корректирующего кода.

Кодовый сигнал, соответствующий значениям младших разрядов кода, и поступивший на выходы блока 10 постоянной

0 памяти, образует вторую часть корректирующего кода, завершая цикл работы устройства,

Восьмиразрядный двоичный код (байт), получаемый на триггерах групп 7, является

5 адресом обращения к блоку 10, Восьмиричное представление двоичного кода осуществляется путем представления каждых трех разрядов, начиная с младших, их десятичным (восьмиричным) эквивалентом: 000 0;

0 001 1; 010 2; 011 3;... Поэтому двоичный восьмиразрядный адрес обращения к блоку 10 в восьмиричной форме будет иметь три разряда, например: 10101010 251.

В таблице указано содержание ячейки

5 блока 10, соответствующее каждому из возможных адресов обращения, например (см. таблицу):

Двоичный код адреса обращения01110010

0 Восьмиричный код

адреса обращения162

Код, записанный в ячейке

блока 10 (восьмиричный), 06

Код .записанный в ячейке

5 блока 10 (двоичный),0110

Таблица составлена путем вычисления корректирующего кода для восьмиразрядного байта поразрядным суммированием по mod 2 кодов номеров разрядов кодируемой информации, содержащих кодовые единицы (три младших двоичных разряда), и дополнением до четности числа единиц в коде информации (старший разряд кода).

Таким образом, предложенное устройство формирует корректирующий код для двоичного цифрового сигнала, поступающего параллельно-последовательным кодом без преобразования параллельных разрядов кода в последовательный, что повышает быстродействие.

Формула изобретения Формирователь корректирующего кода, содержащий счетчик, выходы разрядов которого соединены с первыми входами одноименных элементов И группы, выходы которых соединены со счетными входами одноименных триггеров первой группы, триггер, выход которого и выходы триггеров первой группы являются выходами формирователя, триггеры второй группы, первый сумматор по модулю два, первый элемент задержки и элемент ИЛИ, установочные входы счетчика, триггера и триггеров первой и второй групп являются установочными входами формирователя, отличающийся тем, что, с целью повышения

быстродействия, в него введены второй элемент задержки, блок постоянной памяти и второй сумматор по модулю два, информационные входы которого подключены к выходам одноименных разрядов счетчика, счетный вход счетчика является тактовым входом формирователя, входы первого сумматора по модулю два объединены со счетными входами одноименных триггеров

второй группы и являются информационными входами формирователя, выход первого сумматора по модулю два соединен через первый элемент задержки с вторыми входами элементов И группы и управляющим входом второго сумматора по модулю два, выход которого соединен с первым входом элемента МЛ И, выход которого соединен со счетным входом триггера, выходы триггеров второй группы соединены с одноименными

адресными входами блока постоянной памяти, первый выход которого соединен с вторым входом элемента ИЛИ, выход переполнения счетчика соединен через второй элемент задержки с управляющим входом блока постоянной памяти, вторые выходы которого являются выходами формирователя.

J

czr

л ч

(O

X

л

tf

Qo

3

S

1

| Устройство для декодирования двоичных кодов Хэмминга | 1985 |

|

SU1307593A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кодер | 1987 |

|

SU1474855A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-30—Публикация

1989-05-15—Подача