(21)4298744/24-24

(22)21.08.87

(46) 23.04.89. Бнш. № 15 (72) Ю.И.Горохов (53) 621.394.14 (088.8) (56) Хетагуров А.А. и др. Повышение надежности цифровых устройств методами избыточного кодирования. - М.: Энергия, 1974, с. 35-40, 51-53. Авторское свидетельство СССР № 892714, кл. Н 03 М 13/00, 1980.

(54) КОДЕР

(57) Изобретение относится к электросвязи и может использоваться в системах передачи информации. Изобретение позволяет повысить быстродействие кодера. Кодер осуществляет кодирование информации кодом Хеммин- га с кодовым расстоянием, равным четырем. Кодер содержит мультиплексор 1, элементы ИЛИ 2 и 3, блок 4 задержки, счетчик 5, элементы И 6, 7, триггеры 8 и 9, группы 10 и 11 элементов И, сумматор 12 по модулю два и группы 13 и 14 триггеров. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь корректирующего кода | 1989 |

|

SU1695515A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ИМПУЛЬСНО-ВРЕМЕННЫХ СИГНАЛОВ | 1990 |

|

RU2028732C1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Кодер | 1990 |

|

SU1783623A1 |

Изобретение относится к электросвязи и может использоваться в системах передачи информации. Изобретение позволяет повысить быстродействие кодера. Кодер осуществляет кодирование информации кодом Хемминга с кодовым расстоянием, равным четырем. Кодер содержит мультиплексор 1, элементы 2,3 ИЛИ, блок 4 задержки, элементы 6,7 И, триггеры 8,9, группы 10,11 элементов И, сумматор 12 по модулю два, группы 13,14 триггеров и счетчик 5. 2 ил.

Јъ Ч

42

00

сл ел

Фие.1

1

Изобретение относится к электросвязи и может использоваться для кодирования двоичной информации кодом Хемминга с кодовым расстоянием, равным четырем.

Цель изобретения - повышение быстродействия кодера.

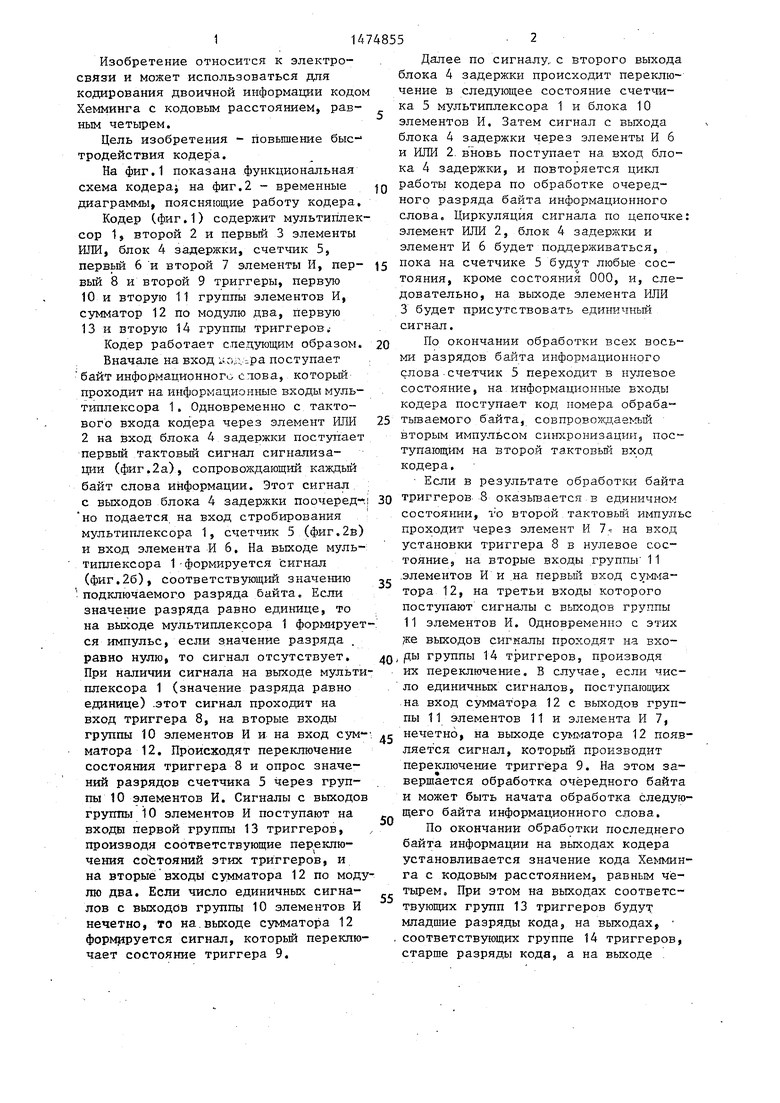

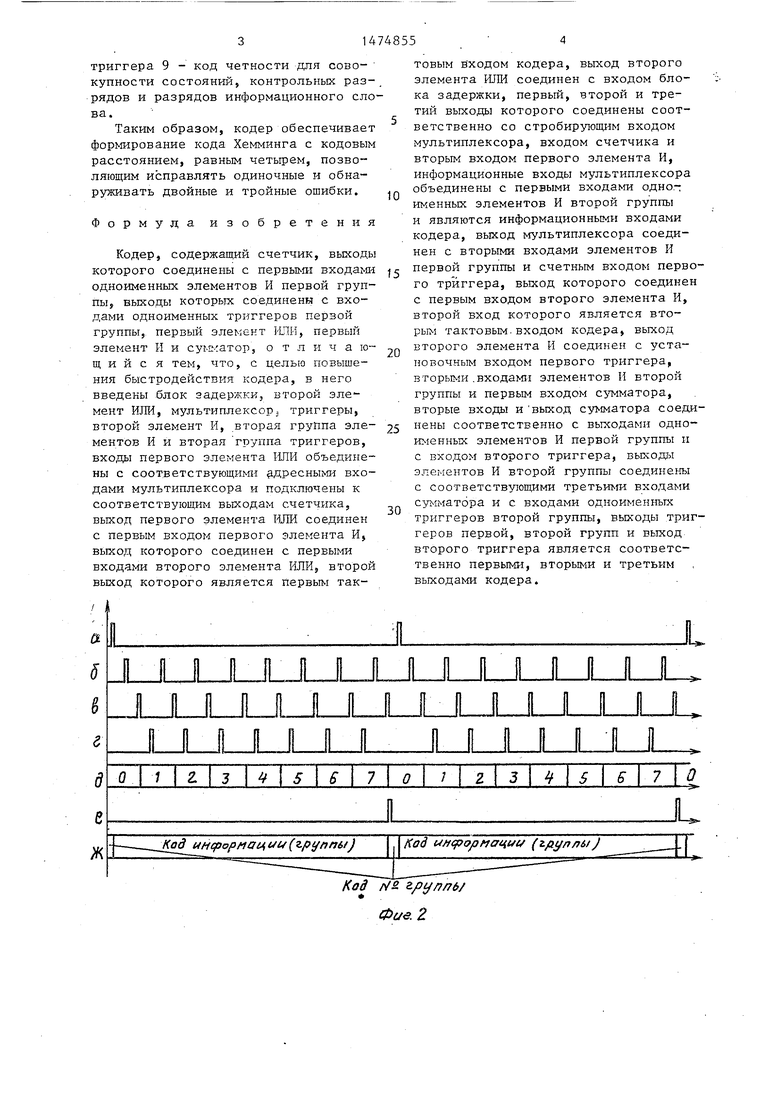

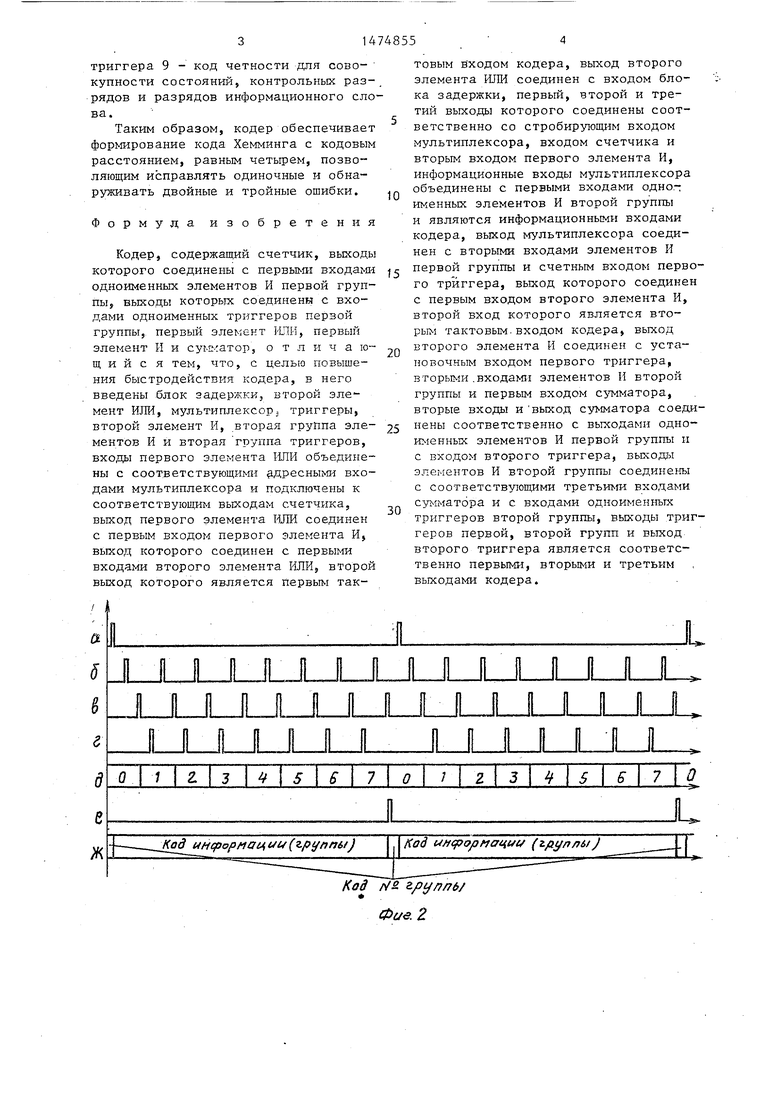

На фиг.1 показана функциональная схема кодера на фиг.2 - временные диаграммы, поясняющие работу кодера,

Кодер (фиг.1) содержит мультиплексор 1, второй 2 и первый 3 элементы ИЛИ, блок 4 задержки, счетчик 5, первый 6 и второй 7 элементы И, первый 8 и второй 9 триггеры, первую 10 и вторую 11 группы элементов И, сумматор 12 по модулю два, первую 13 и вторую 14 группы триггеров.

Кодер работает следующим образом. Вначале на вход ,..:. ра поступает байт информационного ст:ова, который проходит на информационные входы мультиплексора 1. Одновременно с тактового входа кодера через элемент ИЛИ 2 на вход блока 4 задержки поступает первый тактовый сигнал сигнализации (фиг.2а), сопровождающий каждый байт слова информации. Этот сигнал с выходов блока 4 задержки поочеред но подается на вход стробирования мультиплексора 1, счетчик 5 (фиг.2в) и вход элемента И 6, На выходе мультиплексора 1 формируется сигнал (фиг.26), соответствующий значению подключаемого разряда байта. Если значение разряда равно единице, то на выходе мультиплексора 1 формируется импульс, если значение разряда . равно нулю, то сигнал отсутствует. При наличии сигнала на выходе мультиплексора 1 (значение разряда равно единице) .этот сигнал проходит на вход триггера 8, на вторые входы группы 10 элементов И и на вход сумматора 12. Происходят переключение состояния триггера 8 и опрос значений разрядов счетчика 5 через группы 10 элементов И. Сигналы с выходов группы 10 элементов И поступают на входы первой группы 13 триггеров, производя соответствующие переключения состояний этих триггеров, и на вторые входы сумматора 12 по модулю два. Если число единичных сигналов с выходов группы 10 элементов И нечетно, то на выходе сумматора 12 формируется сигнал, который переключает состояние триггера 9.

48552

Далее по сигналу, с второго выхода блока 4 задержки происходит переключение в следующее состояние счетчика 5 мультиплексора 1 и блока 10 элементов И. Затем сигнал с выхода блока 4 задержки через элементы И б и ИЛИ 2 вновь поступает на вход блока 4 задержки, и повторяется цикл .JQ работы кодера по обработке очередного разряда байта информационного слова. Циркуляция сигнала по цепочке: элемент ИЛИ 2, блок 4 задержки и элемент И 6 будет поддерживаться, пока на счетчике 5 будут любые сос15

20

25

30

35

40

45

50

55

тояния, кроме состояния 000, и, следовательно, на выходе элемента ИЛИ 3 будет присутствовать единичный сигнал.

По окончании обработки всех восьми разрядов байта информационного слова счетчик 5 переходит в нулевое состояние, на информационные входы кодера поступает код номера обрабатываемого байта, совпровождаемый вторым импульсом синхронизации, поступающим на второй тактовый вход кодера.

Если в результате обработки байта триггеров 8 оказывается в единичном состоянии, то второй тактовьй импульс проходит через элемент И 7- на вход установки триггера 8 в нулевое состояние, на вторые входы группы 11 элементов И и на первый вход сумматора 12, на третьи входы которого поступают сигналы с выходов группы 11 элементов И. Одновременно с этих же выходов сигналы проходят на вхо- , ды группы 14 триггеров, производя их переключение. В случае, если число единичных сигналов, поступающих на вход сумматора 12 с выходов группы 11 элементов 11 и элемента И 7, нечетно, на выходе сумматора 12 появляется сигнал, который производит переключение триггера 9. На этом завершается обработка очередного байта и может быть начата обработка следующего байта информационного слова.

По окончании обработки последнего байта информации на выходах кодера установливается значение кода Хемминга с кодовым расстоянием, равным четырем. При этом на выходах соответствующих групп 13 триггеров будут младшие разряды кода, на выходах, соответствующих группе 14 триггеров, старше разряды кода, а на выходе

триггера 9 - код четности для совокупности состояний, контрольных разрядов и разрядов информационного слова.

Таким образом, кодер обеспечивает формирование кода Хемминга с кодовым расстоянием, равным четырем, позволяющим исправлять одиночные и обнаруживать двойные и тройные ошибки.

Формула изобретения

Кодер, содержащий счетчик, выходы которого соединены с первыми входами одноименных элементов И первой группы, выходы которых соединены с входами одноименных триггеров первой группы, первый элемент ИЛИ, первый элемент И и сумматор, о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия кодера, в него введены блок задержки, второй элемент ИЛИ, мультиплексорj триггеры, второй элемент И, вторая группа эле- ментов И и вторая группа триггеров, входы первого элемента ИЛИ объединены с соответствующими адресными входами мультиплексора и подключены к соответствующим выходам счетчика, выход первого элемента ИЛИ соединен с первым входом первого элемента И, выход которого соединен с первыми входами второго элемента ИЛИ, второй выход которого является первым так

а 5

JUULJULJULJUL ULJLJULJ

I I I Д I I I Я I I I I I I

о

В 7

Ж

Код информации (группы) ° UMeP°/3naW (-&уплы}

-I ,. ни II и I 11--«i I I j I . - - - . TI .m- илг . - --ЦЩ-

Код tz zpynnb/

0

5

0

5

0

товым в ходом кодера, выход второго элемента ИЛИ соединен с входом блока задержки, первый, второй и третий выходы которого соединены соответственно со стробирующим входом мультиплексора, входом счетчика и вторым входом первого элемента И, информационные входы мультиплексора объединены с первыми входами одноименных элементов И второй группы и являются информационными входами кодера, выход мультиплексора соединен с вторыми входами элементов И первой группы и счетным входом первого триггера, выход которого соединен с первым входом второго элемента И, второй вход которого является вторым тактовым.входом кодера, выход второго элемента И соединен с установочным входом первого триггера, вторыми .входами элементов И второй группы и первым входом сумматора, вторые входы и выход сумматора соединены соответственно с выходами одноименных элементов И первой группы и с входом второго триггера, выходы элементов И второй группы соединены с соответствующими третьими входами сумматора и с входами одноименных триггеров второй группы, выходы триггеров первой, второй групп и выход второго триггера является соответственно первыми, вторыми и третьим выходами кодера.

L

Ч 5

О

Фие.2

Авторы

Даты

1989-04-23—Публикация

1987-08-21—Подача