Изобретение относится к вычисли- , тельной технике и может быть использовано при построении высокопроизводительных систем в качестве средства сопряжения центрального процессора (ЦП) с арифметическими процессорами (АП).

Цель изобретения - повышение производительности устройства.

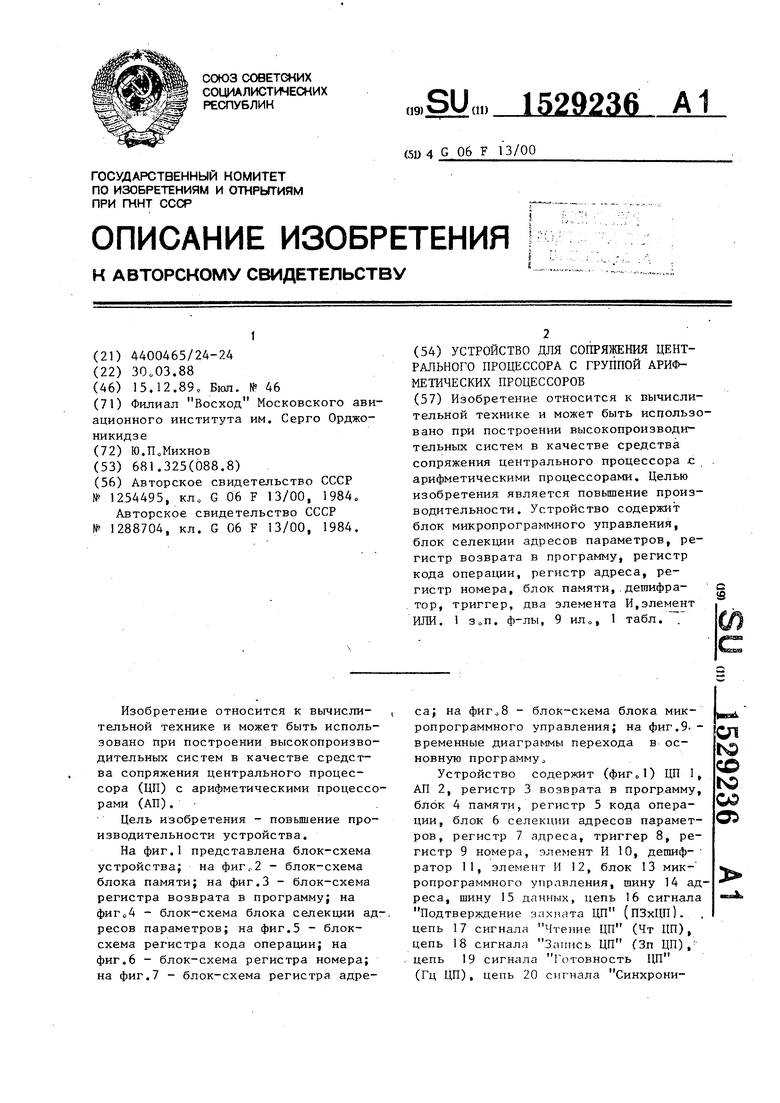

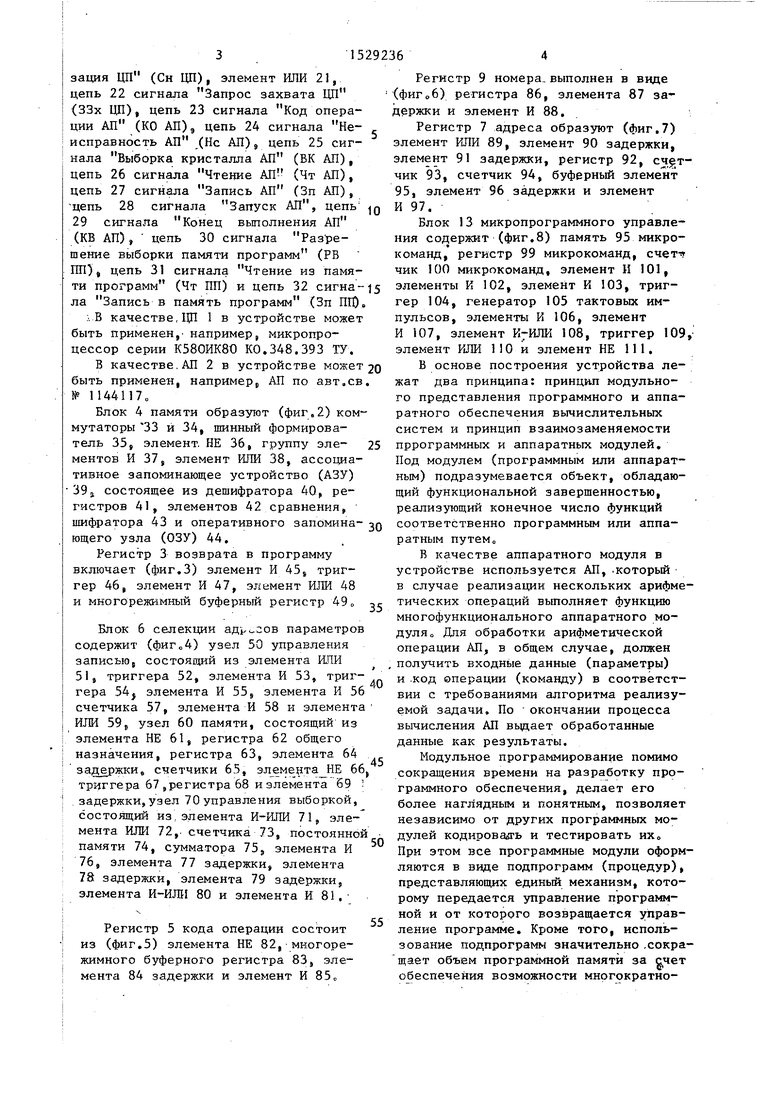

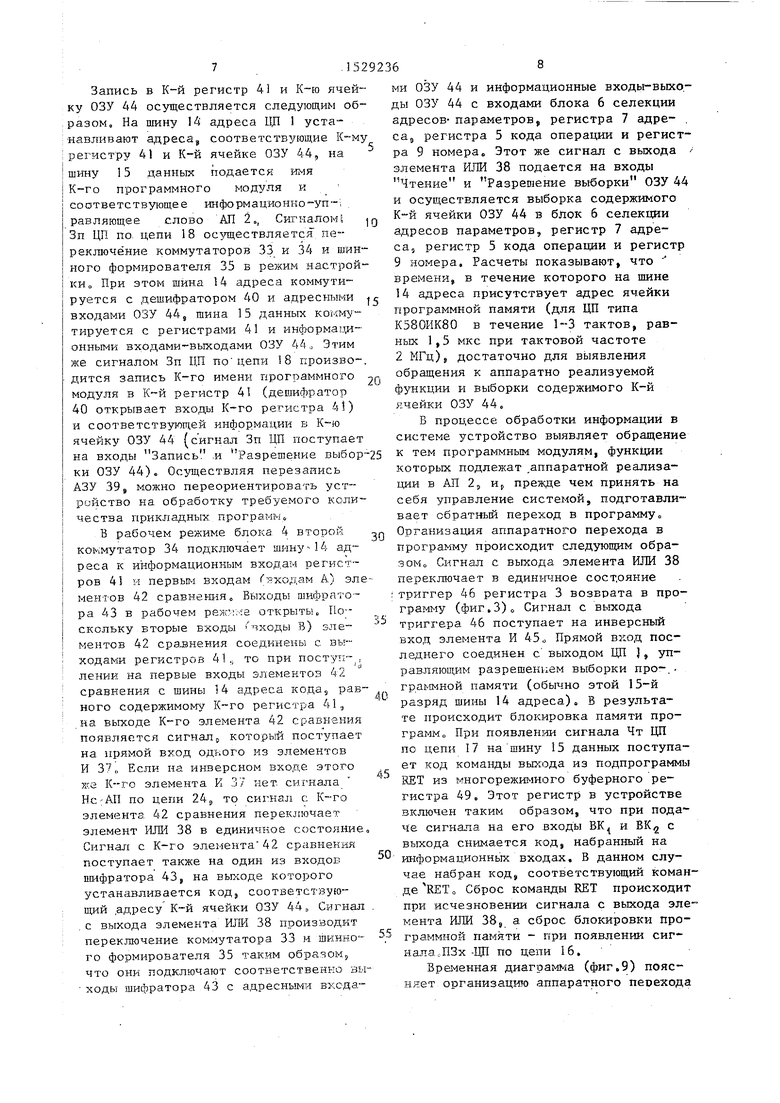

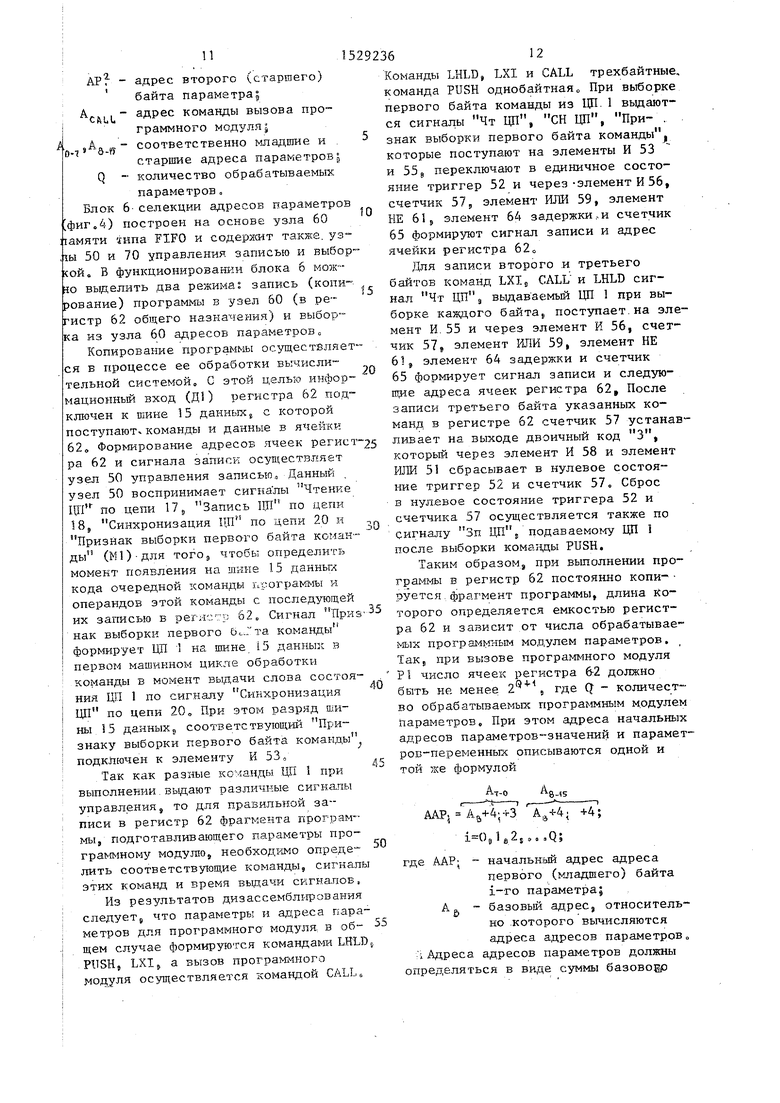

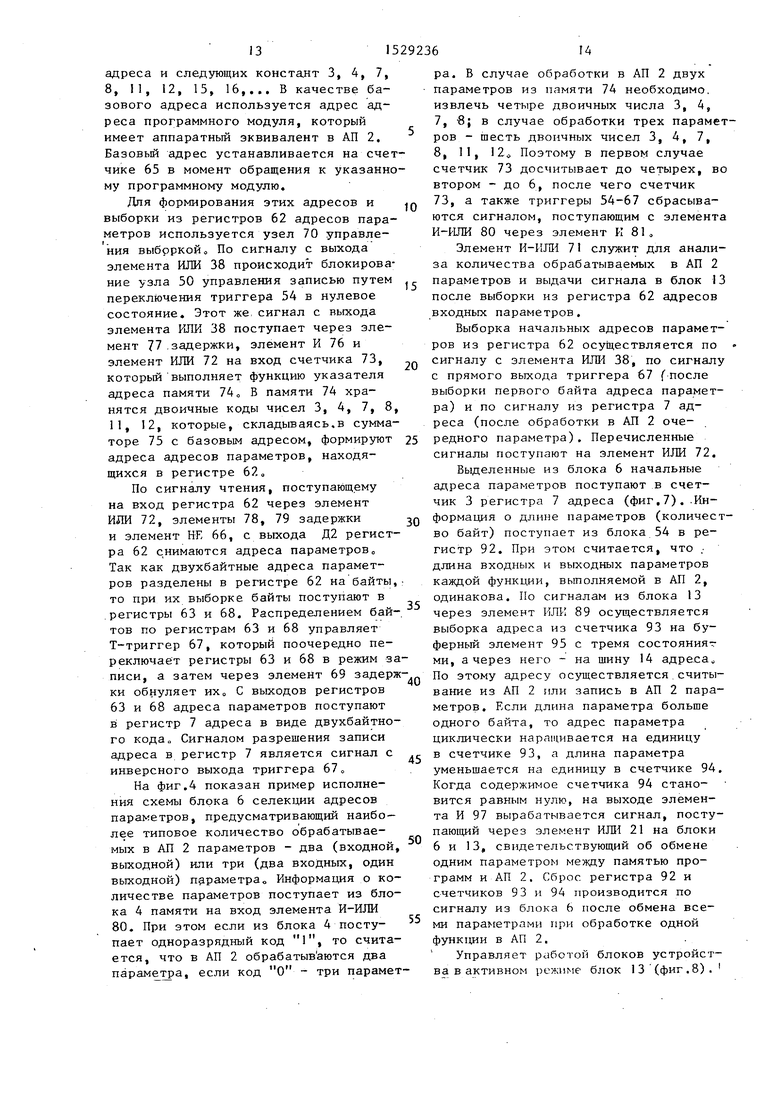

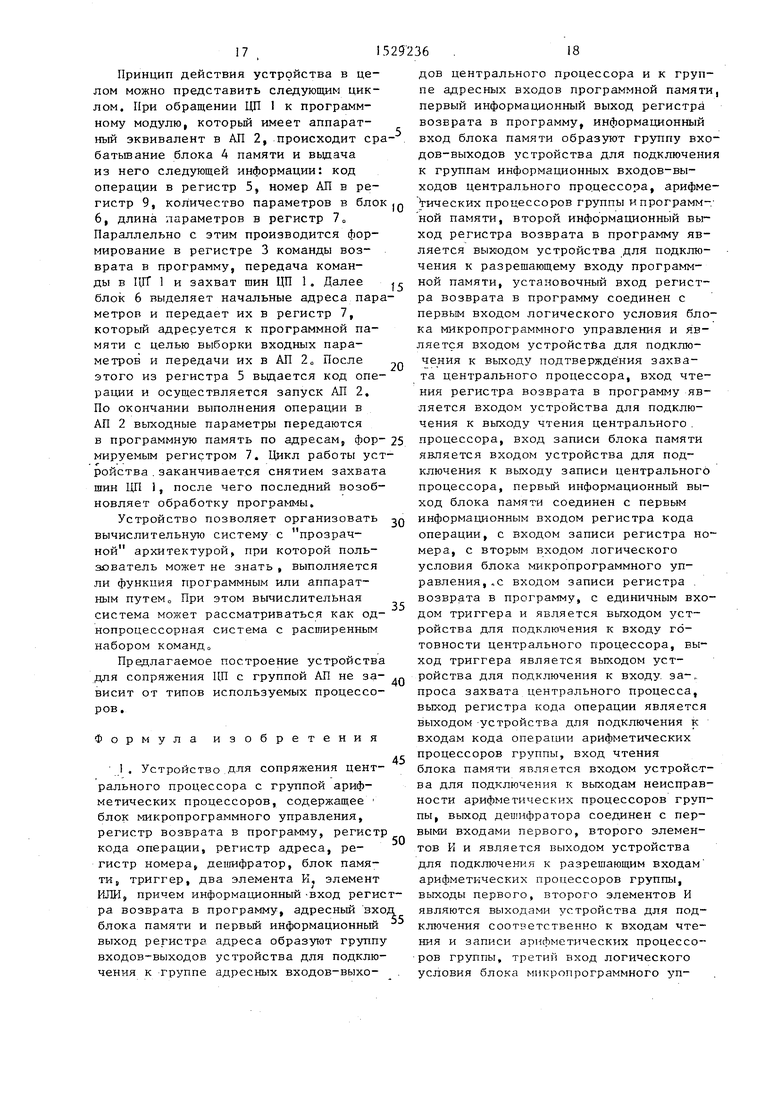

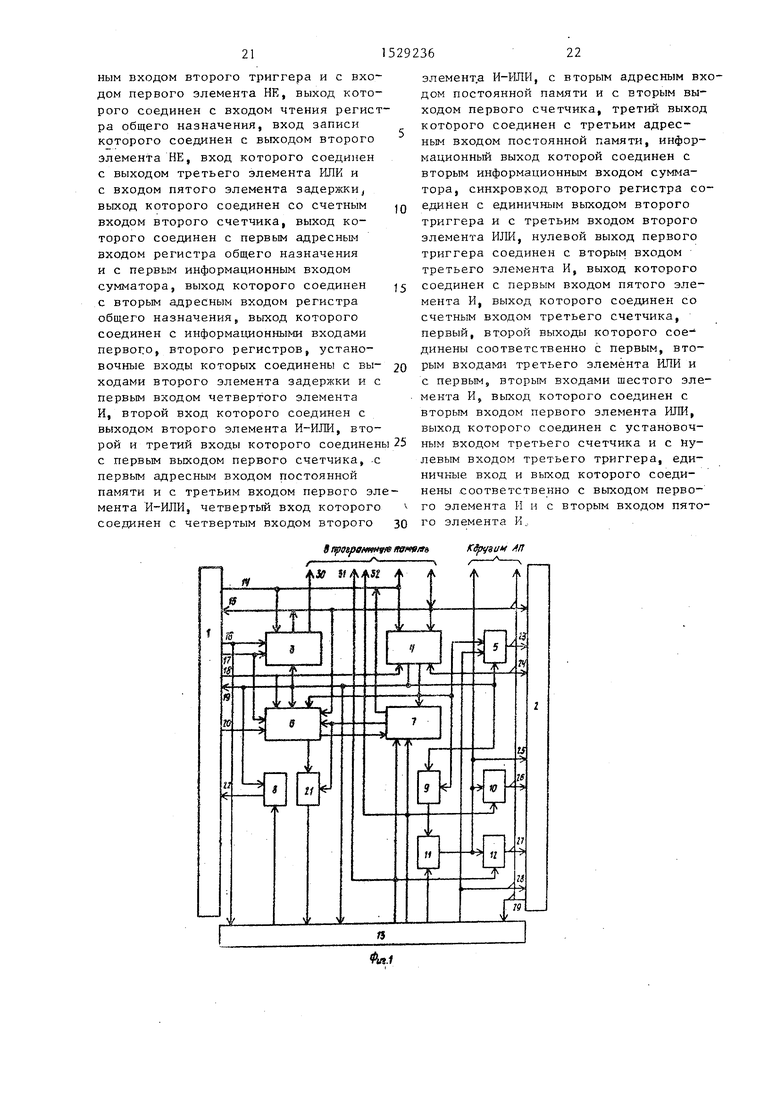

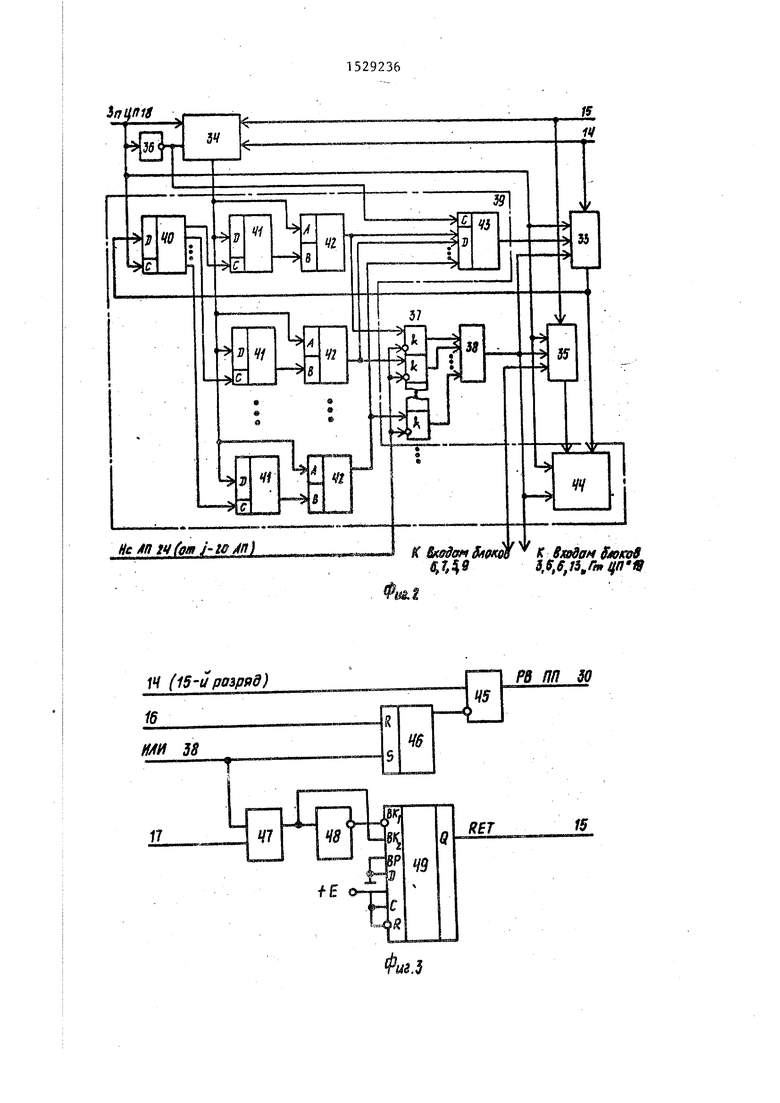

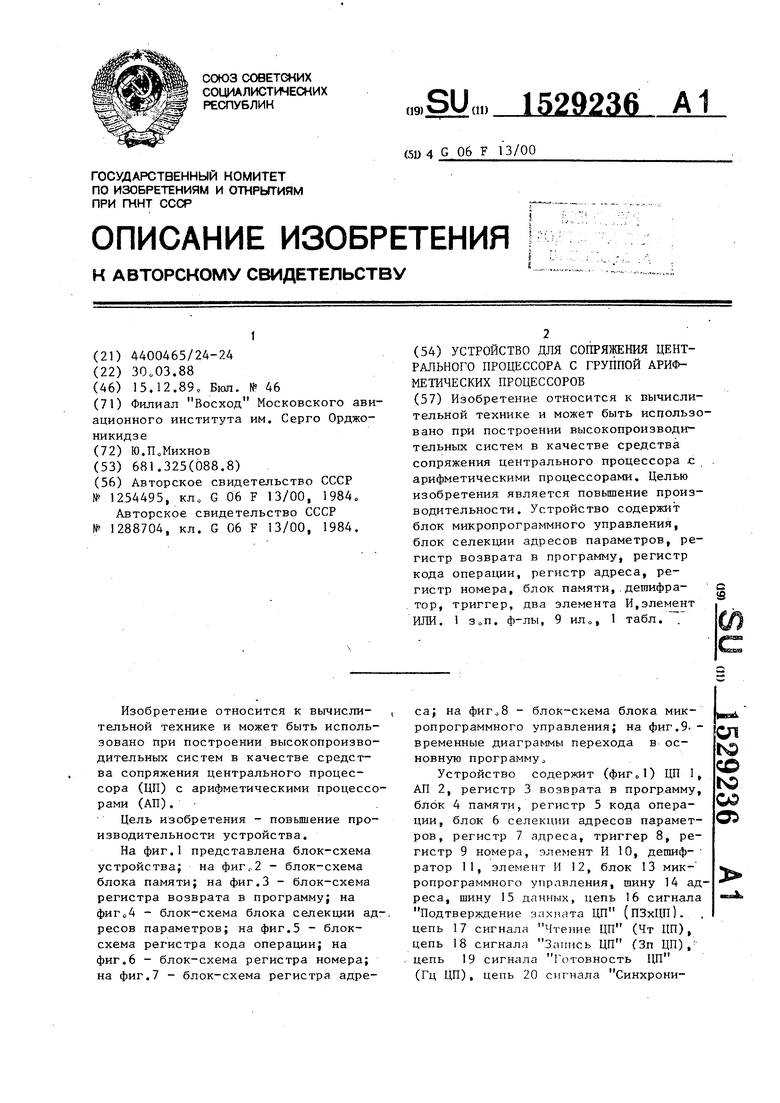

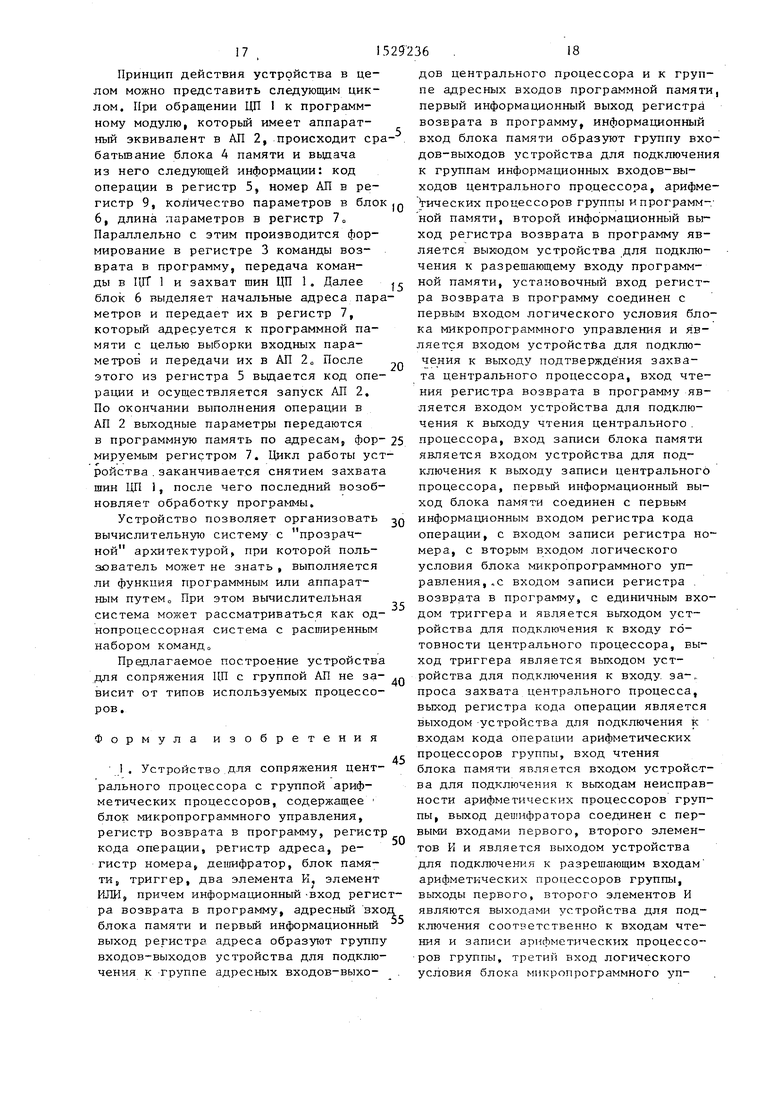

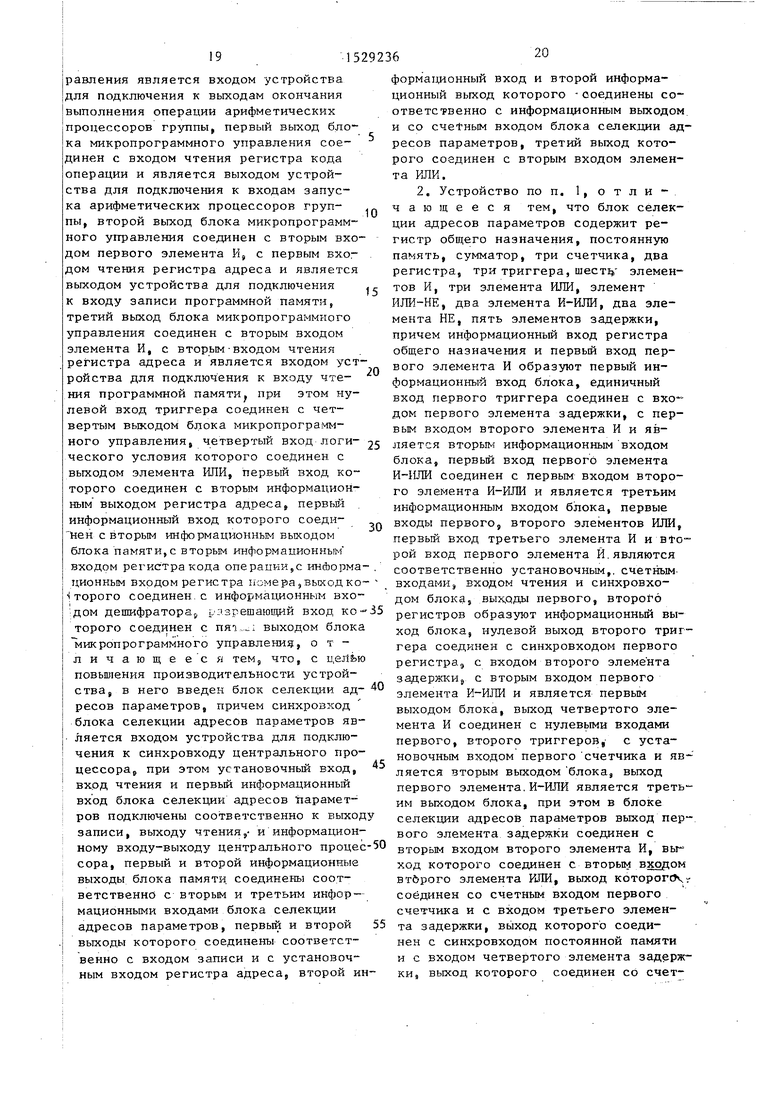

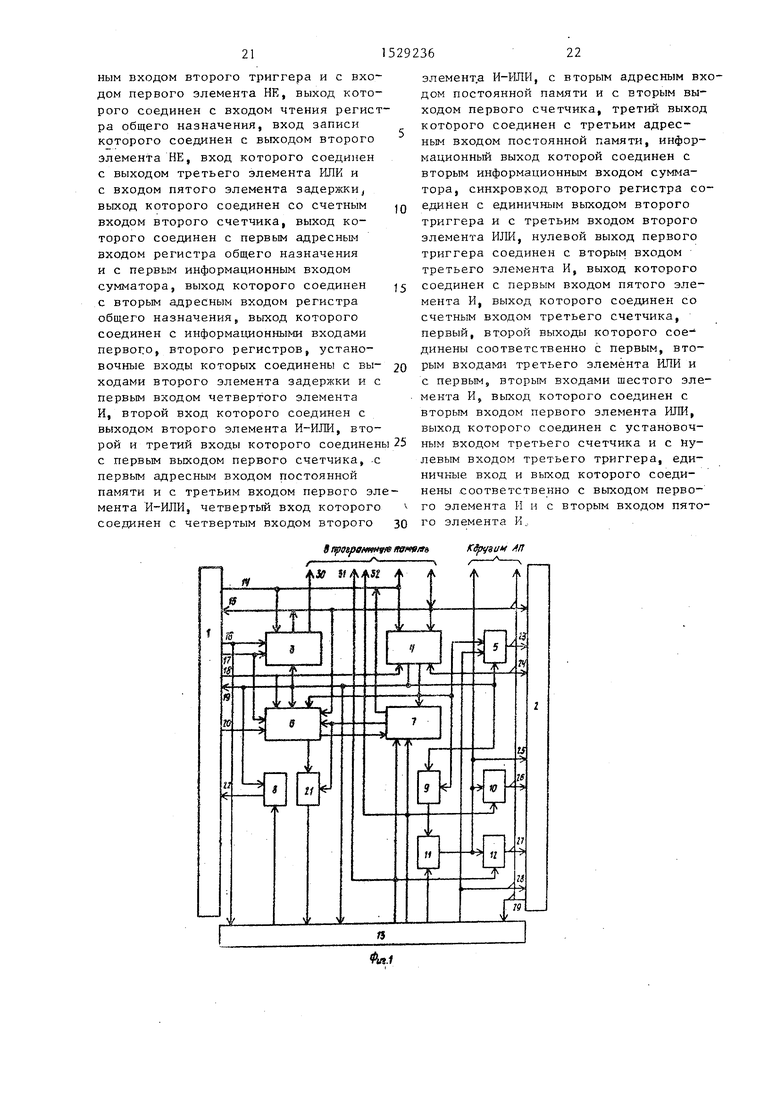

На фиг.1 представлена блок-схема устройства; на фиГо2 - блок-схема блока памяти; на фиг.З - блок-схема регистра возврата в программу; на фиГо4 - блок-схема блока селекции ад-. ресов параметров; на фиг.5 - блок- схема регистра кода операции; на фиг.6 - блок-схема регистра номера; на фиг.7 - блок-схема регистра адреса; на фиг о 8 - блок-скема блока микропрограммного управления; на фиг.9- - временные диаграммы перехода в основную программу о

Устройство содержит (фиг) ЦП 1, АП 2, регистр 3 возврата в программу, блок 4 памяти, регистр 5 кода операции, блок 6 селекции адресов параметров, регистр 7 адреса, триггер 8, регистр 9 номера, элемент И 10, дешиф- ратор 11, элемент И 12, блок 13 мик- ропрограммного управления, шину 14 адреса, шину 15 данных, цепь 16 сигнала Подтверждение аахната ЦП (пЗхЦП). . цепь 17 сигнала Чтение ЦП (Чт ЦП), цепь 18 сигнала Зптгись ЦП (Зп ЦП) , цепь 19 сигнала Готовность ЦП (Гц ЦП), цепь 20 сигнала Синхронисд

ГчЭ СО IsS

СО а

зация ЦП (Сн ЦП), элемент ИЛИ 21, цепь 22 сигнала Запрос захвата ЦП {ЗЗх Щ1), цепь 23 сигнала Код операции АЛ (КО АЛ), цепь 24 сигнала Неисправность АП (Не АИ), цепь 25 сигнала Выборка кристалла АП (ВК АИ), цепь 26 сигнала Чтение АИ (Чт АП), цепь 27 сигнала Запись АП (Зп АП), -цепь 28 сигнала Запуск АП, цепь 29 сигнала Конец выполнения АП (KB АП), цепь 30 сигнала Разрешение выборки памяти программ (РВ ПП), цепь 31 сигнала Чтение из памя10

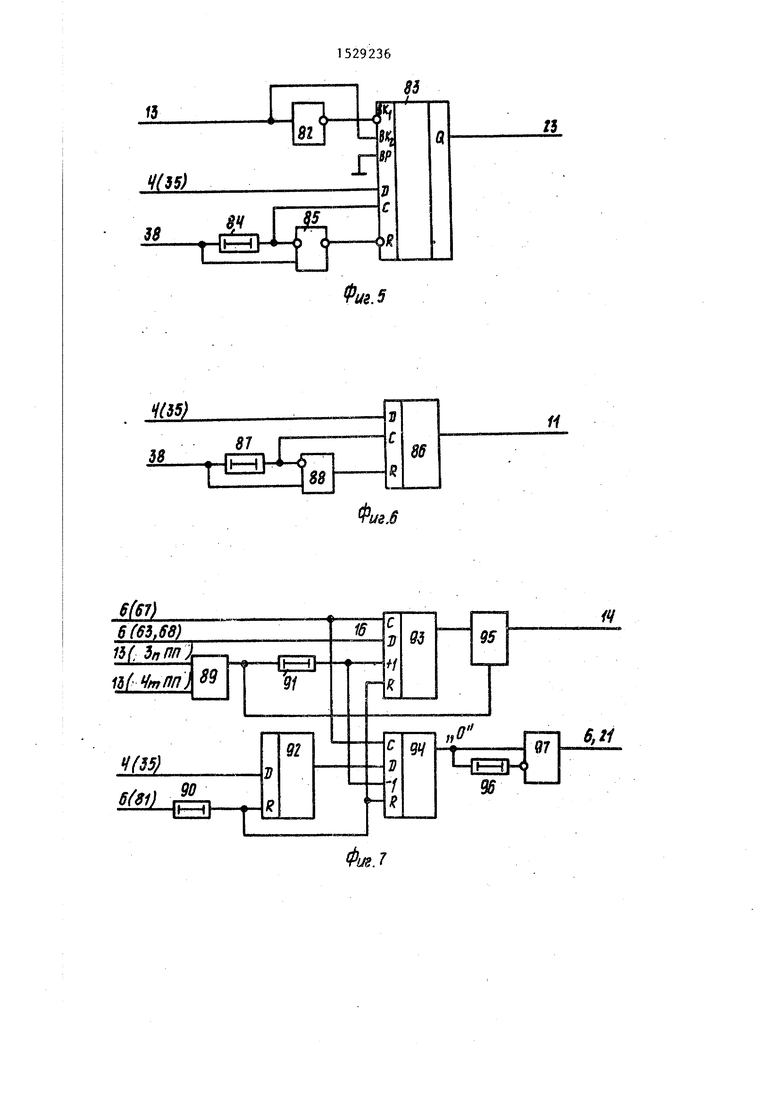

Регистр 9 номера, выполнен в виде (фиг о6) регистра 86, элемента 87 за- дрржки и элемент И 88.

Регистр 7 адреса образуют (фиг,7) элемент ИПИ 89, элемент 90 задержки, элемент 91 задержки, регистр 92, сч§т чик 93, счетчик 9А, буферный элемент 95, элемент 96 задержки и элемент И 97.

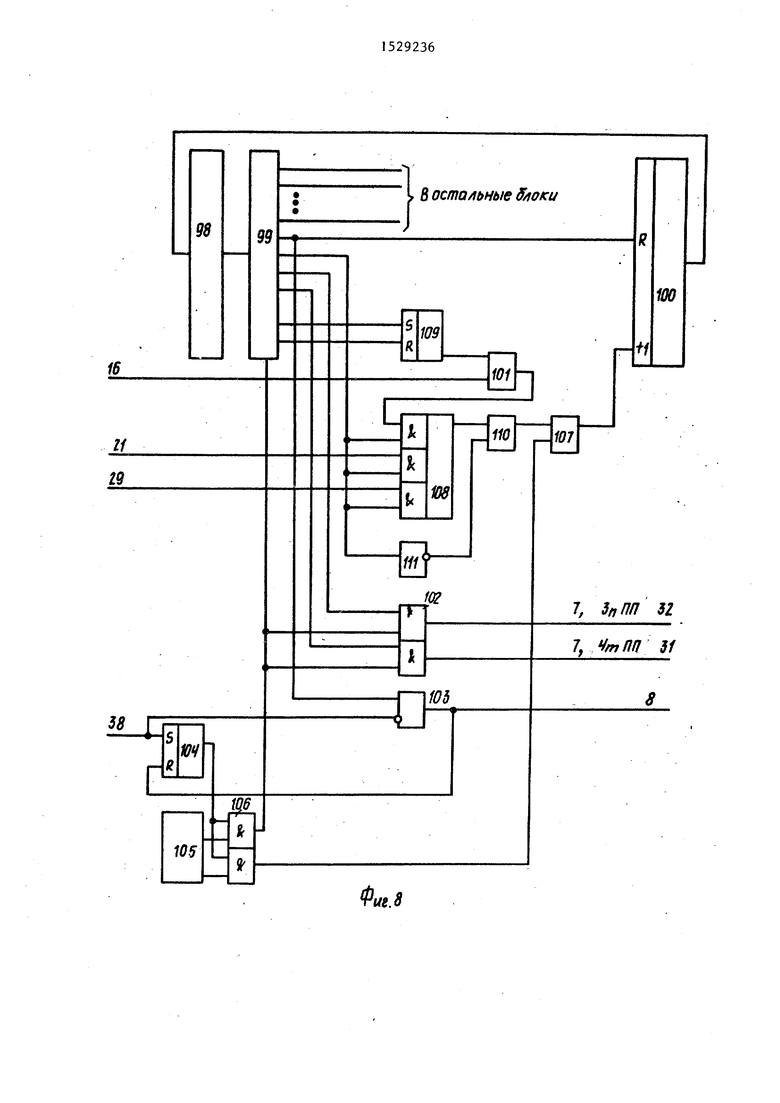

Блок 13 микропрограммного управления содержит (фиг.8) память 95 микрокоманд, регистр 99 микрокоманд, счет- чик 100 микрокоманд, элемент И 101,

ти программ (Чт ПП) и цепь 32 сигна-15 элементы И 102, элемент И 103, триг- ла Запись в память программ (Зп ПП) ..В качестве, 1Щ 1 в устройстве может быть применен, например, микропроцессор серии К580ИК80 КО.348.393 ТУ.

В качестве, АП 2 в устройстве может 20 быть применен, например, АП по авт.св. № 1144117„

Блок 4 памяти образуют (фиг.2) коммутаторы 33 и 34, шинный формирователь 35, элемент. НЕ 36, группу эле- 25 ментов И 37, элемент ИЖ 38, ассоциативное запоминающее устройство (АЗУ) 39,s состоящее из дешифратора 40, регистров 41, элементов 42 сравнения.

гер 104, генератор 105 тактовых импульсов, элементы И 106, элемент И 107, элемент И-ИЛК 108, триггер 109 элемент ИЛИ 110 и элемент НЕ 111.

В основе построения устройства лежат два принципа: принцип модульного представления программного и аппаратного обеспечения вычислительных систем и принцип взаимозаменяемости пррограммных и аппаратных модулей. Под модулем (программным или аппаратным) подразумевается объект, обладающий функциональной завершенностью, реализующий конечное число функций

40

шифратора 43 и оперативного запомина- о соответственно программным или аппа- ющего узла (ОЗУ) 44.

Регистр 3 возврата в программу включает (фиг.З) элемент И 45g триггер 46, элемент И 47, элемент ИЖ 48 и многорежимный буферный регистр 49„ г

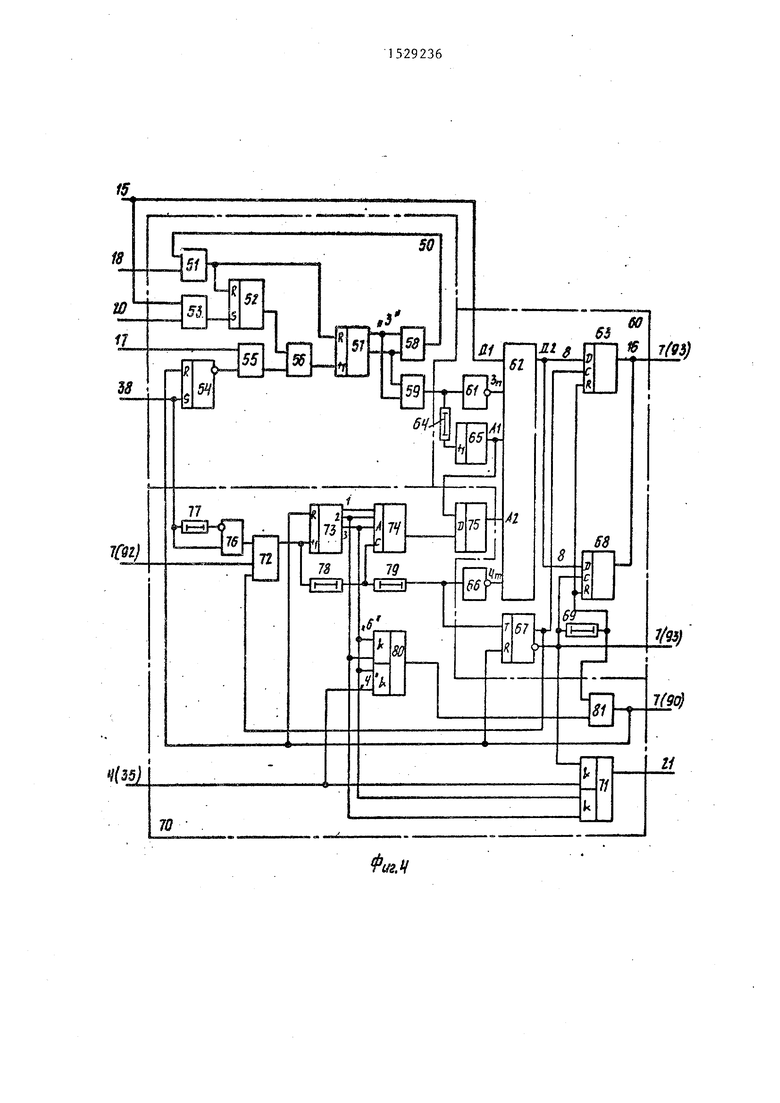

Блок 6 селекции параметров содержит (фиг„4) узел 50 управления записью, состоящий из элемента ИЛИ

а

51, триггера 52, элемента И 53, триггера 54J элемента И 55, элемента И 56 счетчика 57, элемента И 58 и элемента ИЛИ 59, узел 60 памяти, состоящий из элемента НЕ 61, регистра 62 общего назначения, регистра 63, элемента б4 зад&ржки, счетчики 65, элемента НЕ 66,

триггера 67 ,регистра 68 и элемента 69

задержки,узел 70 управления выборкой,

состоящий из, элемента И-ИЛИ 71, элемента ИЛИ 72, счетчика 73, постоянной

памяти 74, сумматора 75 элемента И

76, элемента 77 задержки, элемента

78 задержки, элемента 79 задержки,

элемента И-ИШ1 80 и элемента И 81.50

ратным путемо

В качестве аппаратного модуля в устройстве используется АП, .которьй в случае реализации нескольких арифме тических операций вьтолняет функцию многофункционального аппаратного модуля Для обработки арифметической операции АП, в общем случае, должен получить входные данные (параметры) и .код операции (команду) в соответствии с требованиями алгоритма реализуемой задачи. По окончании процесса вычисления .АП вьщает обработанные данные как результаты.

Модульное программирование помимо сокращения времени на разработку программного обеспечения, делает его более наглядным и понятным, позволяет независимо от других программных модулей кодировад-ь и тестировать их При этом все программные модули оформ ляются в виде подпрограмм (процедур), представляющих единый механизм, которому передается управление программной и от которого возвращается управление программе. Кроме того, использование подпрограмм значительно .сокра щает объем программной памяти за счет обеспечения возможности многократноРегистр 5 кода операции состоит из (фиг,5) элемента НЕ 82, многорежимного буферного регистра 83, элемента 84 задержки и элемент И 85„

Регистр 9 номера, выполнен в виде (фиг о6) регистра 86, элемента 87 за- дрржки и элемент И 88.

Регистр 7 адреса образуют (фиг,7) элемент ИПИ 89, элемент 90 задержки, элемент 91 задержки, регистр 92, сч§т- чик 93, счетчик 9А, буферный элемент 95, элемент 96 задержки и элемент И 97.

Блок 13 микропрограммного управления содержит (фиг.8) память 95 микрокоманд, регистр 99 микрокоманд, счет- чик 100 микрокоманд, элемент И 101,

элементы И 102, элемент И 103, триг-

гер 104, генератор 105 тактовых импульсов, элементы И 106, элемент И 107, элемент И-ИЛК 108, триггер 109 элемент ИЛИ 110 и элемент НЕ 111.

В основе построения устройства лежат два принципа: принцип модульного представления программного и аппаратного обеспечения вычислительных систем и принцип взаимозаменяемости пррограммных и аппаратных модулей. Под модулем (программным или аппаратным) подразумевается объект, обладающий функциональной завершенностью, реализующий конечное число функций

соответственно программным или аппа-

ратным путемо

В качестве аппаратного модуля в устройстве используется АП, .которьй в случае реализации нескольких арифметических операций вьтолняет функцию многофункционального аппаратного модуля Для обработки арифметической операции АП, в общем случае, должен получить входные данные (параметры) и .код операции (команду) в соответствии с требованиями алгоритма реализуемой задачи. По окончании процесса вычисления .АП вьщает обработанные данные как результаты.

Модульное программирование помимо сокращения времени на разработку программного обеспечения, делает его более наглядным и понятным, позволяет независимо от других программных модулей кодировад-ь и тестировать их При этом все программные модули оформляются в виде подпрограмм (процедур), представляющих единый механизм, которому передается управление программной и от которого возвращается управление программе. Кроме того, использование подпрограмм значительно .сокра- щает объем программной памяти за счет обеспечения возможности многократно51

го обращения к однажды ц писанной и отлаженной подпрограмме, исключается необходимость ее многократного дублирования в основной программе. Как и для АП, подпрограмма должна получи некоторые входные данные и выдать результаты.

При оформлении программы на языке высокого уровня обращение к подпро- грамме осуществляется путем указания ее имени в операторе обращения к подпрограмме. После трансляции и компоновки программы имя подпро

лить относительно адреса команды вызова подпрограммы по некоторой формуле, используя этот адрес в качестве базового

5„ Механизм передачи параметров в программные модули определяют структуру блока селекции адресов параметров в составе устройства для сопря - жения ЦП с группой АП,

Для определения конкретной структуры блока селекции адресов параметров рассмотрим случай использования предлагаемого устройства в составе

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

Изобретение относится к вычислительной техние и может быть использовано при построении высокопроизводительных систем в качестве средства сопряжения центрального процессора с арифметическими процессами. Целью изобретения является повышение производительности. Устройство содержит блок микропрограммного управления, блок селекции адресов параметров, регистр возврата в программу, регистр кода операции, регистр адреса, регистр номера, блок памяти, дешифратор, триггер, два элемента И, элемент ИЛИ. 1 з.п. ф-лы, 10 ил., 1 табл.

граммы сопоставляется адресу той ячей-15 микроЭВМ СМ-1800, программирование

ки памяти, в которой размещается первый байт команды подпрограммы. Выход из подпрограммы происходит по команде возврата, являющейся заключительной командой подпрограммы,20

С целью определения механизмов передачи параметров в программные модули, составленные на языке высокого

уровня, бьто выполнено дизассемблиро вание (реассемблирование) ряда программ. По результатам дизассемблиро- вания программ можно сделать следующие выводы,

1, Несмотря на различия механиз- мов передачи параметров, общим для всех компиляторов является подготовка параметров в точке вызова про- рраммного модуля, При этом копии параметров, а чаще начальные адреса параметров, засылаются либо в стек : перед вызовом программного модуля, либо в ячейки памяти, предшествующие или следующие за точкой вызова модул либо в регистры общего назначения ЦП Более общим и обязательно используемым компиляторами является способ передачи параметров по ссылке (параметры - переменные). Часто этот способ является единственным в системе,

.2о В зависимости от места подготовки параметров по отношению к точке вызова программного модуля выделяется подготовка параметров до точки вызова модуля, после точки вызова модуля и комбинированная,

3,Тенденция построения современных операционных систем предполагает вьшолнение соглашений с межпрограммных связях, в рамках которых механизмы передачи параметров в модули инвариантны к языкам программирования , .

4,Начальные адреса параметров в программной памяти можно опреде20

задач в которой осзтдествляется на языке Паскаль/МТ+, версия 5.

Предлагаемое устройство в составе вычислительной системы осуществляет перехват и передачу в арифметические процессоры тех функций, на эффективное выполнение которых ориентированы АП и которые в однопроцессорной системе реализуются программным путем При

5 передаче в АП функций устройство выделяет в программе вначале адреса параметров, а затем и сами параметры, которые обрабатывают арифметические процессоры,

0 Блок 4 памяти (фиг.2) предназначен для определения конфигурации вычислительной системы. Блок 4 построен в виде памяти-каталога на основе АЗУ 39 и функционирует в двух режи.,, мах: настройки и рабочем.

В режиме настройки блока 4 производится запись имен программных модулей, функции которых будут реализоваться в АП 2, и информационно-управляющих слов АП 2. При этом в регистры 41 записываются имена программных модулей, а в ячейки ОЗУ 44 - информационно-управляющие слова АЛ 2i код операции, номер АП, количество обрабатываемых параметров, длина обрабатываемых параметров (например, в байтах) . Запись производится под управлением ЦП 1, таким образом, что имеет место взаимно однозначное соответствие между именем К-го программного модуля, помещаемого в К-й регистр 41, и содержимым К-й ячейки ОЗУ 44, Изменяя определенным образом разрядность полей ОЗУ 44 и объем АЗУ 39, можно получить требуемое количество аппарат- но реализуемых функций в АП 2, а также необходимую длину обрабатываемых параметров „

40

45

0

5

7,15

Запись в К-й регистр 41 и К-ю ячейку ОЗУ 44 осуществляется следующим образом. На шину 14 адреса ЦП 1 устанавливают адреса, соответствующие К-му регистру 41 и К-й ячейке ОЗУ 44, на шину 15 данных подается т-т К-го программного модуля и соответствующее информационко уп-; равляющее слово АЛ 2 СигналомS Зп ЦП по. цепи 18 ос пцествляется переключение коммутаторов 33 и 34 и шинного формирователя 35 в рехким настройки „ При этом шина 14 адреса коммутируется с дешифратором 40 и адресными входами ОЗУ 44, шина 15 данных коммутируется с регистрами 41 и информа ди- онными входами-выходами ОЗУ 44 а Этим лее сигналом Зп ЦП по цепи 18 ггроизводится запись К-го имени программного модуля в регистр 41 (дешифратор 40 открывает входы К-го регистра 41) и соответствующей информации в К-ю ячейку ОЗУ 44 (сигнал Зп ЦП поступает на входы Запись .и Разрешение выбор ки ОЗУ 44)„ Осуществляя перезапись АЗУ 39J можно переориентировать устройство на обработку требтуемого КС ЛН- честна прикладных программ.

В рабочем режиме блока 4 второй кокмутатор 34 подключает шину-14 адреса к информационным входам регистров 41 и первым входам входам А) эле мен-Т ОВ 42 сравнеШ1я„ Вь1ходы шифратора 43 в рабочем режиме открыты. Ио-- скольку вторые входы тходы В) элементов 42 сравнения соединены с въ;-ходами регистров 41,, то при поступ- ,

/ 1 Ленин на первые входы элементов ч.с

сравнения с шины 14 адреса кода, равного содержимому К-го регистра 41, на выходе К-го элемента 42 сравнения появляется сигнал который поступает на прямой вход одного из элементов И 37„ Если на инверсном входе этого же К-го элемента К 37 мет сигнала Нс;А11 по цепи 24 то сигнал с К-го элемента 42 сравнения nepeKjE 04aeT элемент И1П-1 38 в единичное состояние Сигнал с К-го элемента 42 сравненш; поступает также на один из входов пифратора 43, на выходе которого устанавливается код, соответствующий .адресу К-й ячейки ОЗУ 44, Сигнал с выхода элемента ИЛИ 38 производит переключение коммутатора 33 и шинного формирователя 35 таким образом,, что они подключают соответственно зы ходы шифратора 43 с aдpecнь iи вхсда6

8

ми ОЗУ 44 и информационные входы-выходы ОЗУ 44 с входами блока 6 селекции адресов- параметров, регистра 7 адреса регистра 5 кода операции и регистра 9 номера. Этот же сигнал с выхода элемента ИЛИ 38 подается на входы Чтение и Разрешение выборки ОЗУ 44 и осуществляется выборка содержимого К-й ячейки ОЗУ 44 в блок 6 селекции адресов параметров, регистр 7 адреса, регистр 5 кода операции и регистр 9 номера. Расчеты показывают, что времени, в течение которого на шине 14 адреса присутствует адрес ячейки программной памяти (для ЦП типа К580ИК80 в течение 1-3 тактов, равных 1,5 МКС при тактовой частоте 2 МГц), достаточно для выявления обращения к аппаратно реализуемой функции и выборки содержимого К-й ячейки ОЗУ 44.

В процессе обработки информации в системе устройство выявляет обращение к тем программным модулям, функции которых подлежат .аппаратной реализации в АЛ 2,, И(, прежде чем принять на

себя управление системой, подготавливает обратный переход в программу Организация аппаратного перехода в программу происходит следующим образом Сигнал с выхода элемента ИЛИ 38 переключает в единргчное состояние триггер 46 регистра 3 возврата в программу (фиг.З)о Сигнал с выхода триггера 46 поступает на инверсный вход элемента И 45 Прямой вход последнего соединен с выходом ЦП |, управляющим разрешением выборки про-, - граммной памяти (обычно этой 15-й разряд шины 14 адреса). В результате происходит блокировка памяти программ „ При появлен ди сигнала Чт ЦП по цепи 17 на шину 15 данных поступает код команды выхода из подпрограммы RET из многорежимного буферного регистра 49 о Этот регистр в устройстве включен таким образом, что при пода че сигнала на его вхоДы ВК и ВК с выхода снимается код, набранный на информационных входах, В данном случае набран код, соответствующий команде RET о Сброс команды RET происходит при исчезновении сигнала с выхода элемента ШШ 38, а сброс блокировки программной памяти - при появлении сигнала сПЗх -ЦП по цепи 16,

Bpei ieHHaH диаграмма (фиг.9) поясняет организащ-яо аппаратного перехода

.10

в программу ЦП 1 выставляет единичный сигнал ПЗх ЦП по цепи 16 в начале третьего такта машинного цикла Чтение, если сигнал ЗЗх ЦП по цепи 22 поступает в первом такте за 180 не до нарас- 5 тающего фронта второго синхроимпульса, в противном случае этот сигнал ЦЗх ЦП выставляется в третьем такте следующего машинного цикла, АЗУ 39 (фиг. 2)5 выполненное на современ ной элементной базе, имеет очень малое время срабатьшания (порядка 70 не) , что позволяет в 1-3 тактах первого машинного цикла ЦП 1 произвести необходимые действия по i подготовке перехода в программу.

Сигнал с выхода элемента ИЛИ 38 (фиг„2) открывает входы регистра 5 кода операции (фиг.5) и регистра 9 номера (фигоб) таким образом, что вначале производится обнуление содержимого регистров 83 и 86, Элементы 84 и 87 задержки имеют задержку на время сброса (обнуления) регистров 83 и 86 соот- ветственно. Затем сигнал с выхода эле- мекта ИЛИ 38 поступает на входы С регистров 83 и 86, разрешая запись в них данных по информационным входам Сигнал, поступающий из блока 13 на вход элемента НЕ 82, открывает выходы регистра 83, в результате чего содержимое последнего (код операции) подается по цепи 23. Содержимое регистра 86 (номер АП) подается на вход дешифратора 11. Данное устройство позво- 35 ляет гибко наращивать структуру вычислительной системы арифметическими процессорами с передачей им соответствующих функций Для связи с остальными АП 2 соответствующие выводы де- 40 шифратора 11 (фиг) соединены с их входами цепью 25 Сигналы и информация, необходимые для функционирования остальных АП, выведены из устройства на соответствующие входы-выходы 45 АП 2 (на фиго выводы показаны в виде косых линий на общую шину). Инициирование конкретного АП 2 определяется содержимым регистра 9 номера.

Дня пояснения принципа действия блока 6 селекции адресов параметров (фиг.4) необходимо предварительно рассмотреть механизм передачи параметров в программные модули для указанного примера вычислительной систе- 55 мы, С этой целью на примере простейшей программы анализировали исполь-: зуемые Паскалем два способа переда-

15

20

3610

чи параметров (параметры-значения и параметры-переменные) в программные модули. Эта программа на языке Пас- каль/МТ + была скомпилирована и пропущена через дизассемблер микроЭВМ СМ-1800, в результате чего был получен файл, в котором содержатся коды на языке ассемблера, перемежающиеся с соответствуюш 1ми операторами Пас- кал я о

Анализ программы, результата ее дизассемблирования позволяет сделать ряд выводов об организации параметров в программные модули для указанной вычислительной системы

слово в стеке о

а-

АР.

САИ

CbLU

-2-4:;

0-7

АРГ АР;

,2,...Q,

где АР. - адрес первого (младшего) байта параметра;

11

- адрес второго (старгаего) байта параметра

CftUU

0-7 S-W

Q

адрес команды вызова программного модуля 5 соответственно младшие и . старшие адреса параметров количество обрабатываемых параметров.

Блок 6-селекции адресов параметров фиГо4) построен на основе узла 60 1амяти tnna FIFO и содерлсит также, уз- 1Ы 50 и 70 управления записью и выборной. В функционироваю-ти блока 6 мож- so выделить два режима; запись (копирование) программы в узел 50 (в регистр 62 общего назначения) и выбор™ а из узла 60 адресов параметров

Копирование программы осуществляется в процессе ее обработки вычислительной системой, С этой целью инфор рационный вход (Д1) регистра 62 под- лючен к шине 15 данныхj с которой поступают,команды и данные в ячейки 62„ Формирование адресов ячеек регист ра 62 и сигнала записи осуществляет узел 50 управления записью. Данный , узел 50 воспринимает сигналы Чтение

17,, Запись 1Щ по цепи 18j Синхронизация ЦП по цепи 20 и Признак выборки первого байта коман- (М1)-для тогод чтобы определить

ды

момент появления на шине

данньи

кода очередной зсоманды ирограьфш и операндов этой команды с последующей их записью в регистр 62, Сигнал Пркз нак выборки первого С)..та команды формирует ЦП 1 на шине 15 данных в первом машинном обработки команды в момент выдачи слова состояния ЦП 1 по сигналу Синхронизация ЦП по цепи 20, При этом разряд шины 1 5 данныхg соответствующий Признаку выборки первого байта команды подключен к элементу К 53,

Так как разные команды ЦП i при выполнении.выдают различные сигналы управления, то для правильной записи в регистр 62 фрагмента программы, подготавливающего параметры про50

граьфшому модулю, необходг-дао опреде лить соответствующие команды, сигналы этих команд и время выдачи сигналов. Из результатов дизассемблг-грования следуетJ что параметрь; и адреса параметров для программного модуля, в об- - щем случае формируются командами LRLD,, PUSH, LXI 5 а вызов програм1чного модуля осуществляется командой CALL в

1529236

12

o

5

„

Команды LHLD, LXI и CALL трехбайтные, команда PUSH однобайтнаяо При выборке первого байта команды из ЦП.1 вьщают- ся сигналы Чт ЦП, СН ЦП, При- , знак выборки первого байта команды которые поступают на элементы И 53 и 55 8 переклю4с1ют в единичное состояние триггер 52 и через-элемент И 56, счетчик 575 элемент ИЛИ 59, элемент

0

0

-

НЕ 61, элемент 64 задержки,и счетчик 65 формируют сигнал записи и адрес ячейки регистра 62о

, записи второго .и третьего байтов команд LXIj CALL и LHLD сигнал Чт ЦП э вьщав аемьй ЦП 1 при выборке каждого байта, поступает.на элемент И. 55 и через элемент И 56, счет чик 57, элемент ИЛИ 59, элемент НЕ 61, элемент 64 задержки и счетчик 65 формирует сигнал записи и следующие адреса ячеек регистра 62, После записи третьего байта указанных команд в регистре 62 счетчик 57 устанавливает на выходе двоичный код 3, который через элемент И 58 и элемент ШЖ 51 сбрасывает в нулевое состояние триггер 52 и счетчик 57. Сброс в нул.евое состояние триггера 52 и счетчика 57 осуществляется также по сигналу Зп подаваемому ЦП 1 после выборки комаццы PUSH.

Таким образом, при выполнении про- rpat.Mbi в регистр 62 постоянно копи- руется.фрагмент программы, длина Которого определяется емкостью регистра 62 и зависит от числа обрабатываемых программным модулем параметров. Так5 при вызове программного модуля РI число ячеек регистра 6-2 должно

быть не менее 2

Q-H

где Q - количество обрабатываемых программным модулем параметрове При этом адреса начальных адресов параметров-значений и параметров-переменных описываются одной и той же формулой

АТ-О

A,+ 4;-i-3

А

S-(s

А.

+4;

50

-

,,2s..,Q;

где ААР - начальн1Ь1й адрес адреса

первого (младшего) байта i-го параметра;

К базовый ад,рес, относительно которого вычисляются адреса адресов параметров„ ; Адреса адресов параметров должны определяться в ви,це суммы базовоЕр

13

адреса и следующих констант 3, 4, 7, 8, 11, 12, 15, 16,.., В качестве базового адреса используется адрес адреса программного модуля, который имеет аппаратный эквивалент в АП 2. Базовый адрес устанавливается на счечике 65 в момент обращения к указаннму программному модулю.

Для формирования этих адресов и выборки из регистров 62 адресов параметров используется узел 70 управления выбрркойо По сигналу с выхода элемента ИЛИ 38 происходит блокирование узла 50 управления записью путем переключения триггера 54 в нулевое состояние. Этот же сигнал с выхода элемента КПК 38 поступает через элемент 77 .задержки, элемент И 76 и элемент ИЛИ 72 на вход счетчика 73, который выполняет функцию указателя адреса памяти 74 В памяти 74 хранятся двоичные коды чисел 3, 4, 7, 8 11, 12, которые, складываясь.в сумматоре 75 с базовым адресом, формируют адреса адресов параметров, находящихся в регистре 6. „

По сигналу чтения, поступанэщему на вход регистра 62 через элемент ИДИ 72, элементы 78, 79 задержки и элемент НЕ 66, с выхода Д2 регистра 62 унимаются адреса параметров„ Так как двухбайтные адреса параметров разделены в регистре 62 на байты то при их выборке байты поступают в регистры 63 и 68. Распределением байтов по регистрам 63 и 68 управляет Т-триггер 67, который поочередно переключает регистры 63 и 68 в режим з

писи, а затем через элемент 69 задержки обнуляет их о С выходов регистров 63 и 68 адреса параметров поступают в регистр 7 адреса в виде двухбайтного кода„ Сигналом разрешения записи адреса в регистр 7 является сигнал с инверсного выхода триггера 67„

На фиг.4 показан пример исполнения схемы блока 6 селекции адресов параметров, предусматривающий наиболее типовое количество обрабатываемых в АП 2 параметров - два (входной, выходной) или три (два входных, один выходной) параметра,, Информация о количестве параметров поступает из блока 4 памяти на вход элемента И-ИЛИ 80. При этом если из блока 4 поступает одноразрядный код 1, то считается, что в АП 2 обрабатыв аются два параме а, если код

0 - три парамет10

29236

14

ра. В случае обработки в АП 2 двух параметров из памяти 74 необходимо, извлечь четыре двоичных числа 3, 4,

7,в; в случае обработки трех параметров - шесть двоичных чисел 3, 4, 7,

8,11, 12 Поэтому в первом случае счетчик 73 досчитывает до четырех, во втором - до 6, после чего счетчик

73, а также триггеры 54-67 сбрасыва5

0

5

0

5

0

45

0

55

И-ИЛИ 80 через элемент К 81,

Элемент И-ИЛИ 71 служит для анализа количества обрабатываемых в АП 2 параметров и выдачи сигнала в блок 13 после выборки из регистра 62 адресов входных параметров.

Выборка начальных адресов параметров из регистра 62 осуществляется по « сигналу с элемента ИЛИ 38, по сигналу с прямого выхода триггера 67 f после выборки первого байта адреса параметра) и по сигналу из регистра 7 адреса (после обработки в АП 2 очередного параметра). Перечисленные сигналы поступают на элемент ИЛИ 72.

Выделенные из блока 6 начальные адреса параметров поступают в счетчик 3 регистра 7 адреса (фиг.7)..Информация о длине параметров (количество байт) поступает из блока 54 в регистр 92. При этом считается, что . длина входных и выходных параметров каждой функции, выполняемой в АП 2, одинакова. По сигналам из блока 13 через элемент ИЛИ 89 осуществляется выборка адреса из счетчика 93 на буферный элемент 95 с тремя состояния ми, а через него - на шину 14 адреса. По этому адресу осуществляется.считывание из АП 2 или запись в АП 2 параметров. Если длина параметра больше одного байта, то адрес параметра циклически наращивается на единицу в счетчике 93, а длина параметра уменьшается на единицу в счетчике 94. Когда содержимое счетчика 94 становится равным нулю, на выходе элемента И 97 вырабатывается сигнал, поступающий через элемент ИШ1 21 на блоки 6 и 13, свидетельствующий об обмене одним параметром между памятью программ и АИ 2, Сброс регистра 92 и счетчиков 93 и 94 производится по сигналу из блока 6 после обмена всеми параметрами при обработке одной функгщи в АП 2.

Управляет работой блоков устройства в активном режиме блок 13 (фиг.8).

:. 151529236

Е| качестве синхронизирующего элемен- ta блока используется двухтактный rieHepaTop 105 импульсов, синхросиг

5-алы с которого поступают на узлы Слока 3 после появления сигнала с 1ыхода элемента ИЛИ 38 блока 4 на единичном входе.триггера 104. Этот сигнал означает что происходит обра п;ение к программному модулю, имеюще ьгу аппаратный эквивалент в АП 2, С выхода элементов И 106 тактовые имйуль- сы поступают: первый - на вход Раз- 1ешение записи, регистра 99 и элемен- Ы И 102 j второй на элемент И 107, По первому синхроимпульсу производится запись и вьадача управляющих сигналов из регистра 99 на внутренние узлы блока 13 и узлы устройства По кторому синхроимпульсу происходит прибавление единицы к содержимому счетчика 100 и выборка микрокоманды 13 памяти 98 микрокоманд причем пер- :)оначальньй сброс счетчика 100 производится при включении питания на уст-

)ОЙСТВОо

На вход блока 13 поступак1Т сигнал 113х ЦП по цепи 16, а также сигналы с . эыходов регистра 7 адреса (через эле- чент ИЛИ 21), блока 6 селекции адресо 1араметров (через элемент ИЛИ 21)5 (В АЛ по цепи 29, определяющие время выборки очередной микрокоманды, В блоке 13 используется система с жесткой последовательностью микрокоманд в уни тарных кодах (кайсдому разряду микрокоманды сопоставляется управляющий сигнал блока 13)« Работу блока 13 поясняет таблицаJ представляющая собой последовательность и кодировку микрокоманд, находящихся в памяти 98 микрокоманд

Разряды микрокоманды поступают:, ХО - на вход элемента И-Ш1И 1085 XI - на единичный вход триггера 109:

16

0

0

5

зо 35

40

45

50

55

Х2 - на нулевой вход триггера 109;

ХЗ - на вход дешифратора 11;

Х4 - на вход второго элемента И

группы 102 (входы чтения регистра 7 адреса, сигналы Зп АЛ по цепи 27, Чт ПП по цепи

31)1

Х5 на входы регистра 5 кода операции и сигнал Зп АИ по цепи 27 | Х6 на вход первого элемента И

группы 102 (входы чтения регистра 7 адреса, сигналы Чт АП по цепи 26, Зп ПП по цепи 32);

Х7 - на нулевой вход, счетчика 100, элемент И 103 (на нулевые входы триггеров 8 и 104), При наличии единицы в нулевом разряде микрокоманды блок 13 находится в режиме Ожидание до прихода одного из внешних сигналов на элементы 101 и 108, При нулевом состоянии этого разряда в очередном такте производится прибавление единицы в счет- чик 100 и выборка очередной микроко-. манды из памяти 98 микрокоманд в регистр 99 о

Блок 13 работает следзпощим обра- зомв При включении питания на устройство на Бьгходе регистра. 99 появляется нулевая микрокоманда npsj поступт лении сигнала с выхода элемента ИЛИ 38 на единичный вход триггера 104 на выходе регистра 99 ..появляется первая микрокоманда, которая ожидает появление сигнала ЛЗх ЦП по цепи 16„ Этот сигнал осуществляет выборку второй микрокоманды, по которой производится загрузка АЛ 2 входными параметрами до момента появления на входе элемента И-ИЛИ 108 сигнала от элемента ИЛИ 21„ После этого выбирается третья микрокоманда, по которой осуществляется загрузка АП 2 кодом операции из регистра 5 и выборка четвертой микрокомандыо

Эта микрокоманда ожидает сигнал KB АП по цепи 29„ При его появлении происходит выборка пятой микрокоманды; которая управляет вьщачей результатов вычисления из АП 2 в программную память до момента появления сигнала из регистра 5 адреса При появлении этого сигнала выбирается шестая микрокоманда,, которая ливает блок 13,

Принцип действия устройства в целом можно представить следуюпщм циклом. При обращении ЦП 1 к программному модулю, который имеет аппаратный эквивалент в АЛ 2, происходит ср батьшание блока 4 памяти и вьщача из него следующей информации: код операции в регистр 5, номер АП в регистр 9, количество параметров в блок 6, длина параметров в регистр „ Параллельно с этим производится формирование в регистре 3 команды возврата в программу, передача команды в ЦП 1 и захват шин ЦП 1 , Далее блок 6 выделяет начальные адреса параметров и передает их в регистр 7, который адресуется к программной памяти с целью выборки входных параметров и передачи их в АП 2. После этого из регистра 5 выдается код операции и осуществляется запуск АП 2, По окончании выполнения операции в АП 2 выходные параметры передаются в программную память по адресам, фор- мируемым регистром 7. Цикл работы устройства .заканчивается снятием захвата шин ЦП 1, после чего последний возобновляет обработку программы.

Устройство позволяет организовать вычислительную систему с прозрачной архитектурой, при которой пользователь может не знать , выполняется ли функция программным или аппаратным путемо При этом вычислительная система может рассматриваться как од нопроцессорная система с расширенным набором команд о

Предлагаемое построение устройства для сопряжения ЦП с группой АП не за- висит от типов используемых процессоров.

Формула изобретения

I . Устройство .для сопряжения центрального процессора с группой арифметических процессоров, содержащее блок микропрограммного управления, регистр возврата в программу, регистр

50

кода операции, регистр адреса, регистр номера, дешифратор, блок памяти, триггер, два элемента К, элемент ИЛИ, причем информационный -вход регистра возврата в программу, адресный вход блока памяти и первьй информационньш выход регистра адреса образуют группу входов-выходов устройства для подключения к группе адресных входов-выхоQс ,- 5

о

„

5

5

0

дов центрального процессора и к группе адресных входов программной памяти, первый информационный выход регистра возврата в программу, информационный вход блока памяти образуют группу входов-выходов устройства для подключения к группам информационных входов-выходов центрального про.цессора, арифме- ических процессоров группы и программ-; ной памяти, второй информационный выход регистра возврата в программу является устройства для подключения к разрешающему входу программной памяти, установочный вход регистра возврата в программу соединен с первым входом логического условия блока микропрограммного управления и является входом устройства для подключения к выходу подтверждения захвата центрального процессора, вход чтения регистра возврата в программу является входом устройства для подключения к выходу чтения центрального . процессора, вход записи блока памяти является входом устройства для подключения к выходу записи центрального процессора, первьй информационный выход блока памяти соединен с первым информационным входом регистра кода операции, с входом записи регистра номера, с вторым входом логического условия блока микропрограммного управления, „с входом записи регистра . возврата в программу, с единичным входом триггера и является выходом устройства для подключения к входу готовности центрального процессора, выход триггера является выходом устройства для подключения к входу, за-, проса захвата центрального процесса, выход регистра кода операции является выходом -устройства для подключения к входам кода операш-га арифметических процессоров группы, вход чтения блока памяти является входом устройства для подключения к выходам неисправности арифметических процессоров группы, выход дешифратора соединен с первыми входами первого, второго элементов И и является выходом устройства для подключения к разрешающим входам арифметических процессоров группы, выходы первого, второго элементов И являются выходами устройства для подключения соответственно к входам чтения и записи арифметических процессо- -ров группы, третий вход логического условия блока микропрограммного уп

|равления является входом устройства |для подключения к выходам окончания jвыполнения операции арифметических процессоров группы, первый выход бло ка микропрограммного управления соединен с входом чтения регистра кода операции и является выходом устройства для подключения к входам запуска арифметических процессоров группы, второй выход блока микропрограммного управления соединен с вторым входом первого элемента И, с первым входом чтения регистра адреса и является выходом устройства для подключения к входу записи программной памяти, третий выход блока микропрограммного управления соединен с вторым входом элемента И, с вторым-входом чтения регистра адреса и является входом устройства для подключения к входу чтения программной памяти, при этом нулевой вход триггера соединен с четвертым выходом блока микропрогра чм- ного управления, четвертый вход логи- ческого условия которого соединен с выходом элемента ИЛИ, первый вход которого соединен с вторым информационным выходом регистра адреса, первьй информационный вход которого соеди- Нен с вторым информационным выходом блока памяти,с вторым информационным входом регистра кода операиии с инсЬорма ционным входом регистра номера,выход ко | торого соединен, с информационным вхо- :дом дешифратора разрешающий вход ко торого соединен с пя1..,; выходом блока микропрограммного управление, о т - л и ч ающе ее я теМд что, с повьш1ения производительности устройства, в него введен блок селекции ад- ресов параметров, причем синхровход блока селекции адресов параметров яв- ляется входом устройства для подключения к синхровходу центрального процессора,, при этом установочный вход, вход чтения и первьй информационный вход блока селекции адресов Тпарамет- ров подключены соответственно к выход записи, выходу чтения,- и информационному входу-выходу центрального процес сора, первый и второй информационные выходы блока памяти, соединены соответственно с вторым и третьим инфор- мационными входами блока селекции адресов параметров, первый и второй выходы которого соединены соответственно с входом записи и с установочным входом регистра адреса, второй и

0

5

5 , З 50 55 0

форматщонный вход и второй информационный выход которого - соединены соответственно с информационным выходом и со счетным входом блока селекдии адресов параметров, третий выход которого соединен с вторым входом элемента ИЛИ.

S f ffspOM ty/e naffeisb

элемента И-РШИ, с вторым адресным вхдом постоянной памяти и с вторым выходом первого счетчика, третий выход которого соединен с третьим адресным входом постоянной памяти, информационный выход которой соединен с вторым информационным входом сумматора, синхров сод второго регистра соединен с единичным выходом второго триггера и с третьим входом второго элемента ИЛИ, нулевой выход первого триггера соединен с вторым входом третьего элемента И, выход которого соединен с первым входом пятого элемента И, выход которого соединен со счетным входом третьего счетчика, первый, второй выходы которого сое- динены соответственно с первым, вторым входами третьего элемента ИЛИ и с первым, вторым входами шестого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с установочным входом третьего счетчика и с нулевым входом третьего триггера, единичные вход и выход которого соединены соответственно с выходом первого элемента И и с вторым входом пятого элемента И..

KSpt/BUM АП

SuUnig

W

e

e

-

4fr

Hc/inS4(omj tf 4n}

JL

n/

i

53

37

jf

3

ЗУ

u

vy

К SxsSoM $Л9К6

К fjcffdoft ffioxifS S,S,S, ЦПЧ9

Фаз.7

1L. JL

19

38

17У

Г--И

101

110

107

Ю8

Wf

f(s

1, Зппп зг

7, J/

о

Юд

S

ь

71

I тг , T-J т

П П I

сг

/

/5 3S 22

19

Л 30

ff В

+

I

+

Т

fxT

1

5

AJ

i

t

и.

.TZ гз

. ./ -f

I

П

фиг. 9

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1988-03-30—Подача