Вх, инф. afxl

8ых. инф. 8(х)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля линейных цифровых блоков | 1988 |

|

SU1631545A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля дискретных объектов | 1987 |

|

SU1594540A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

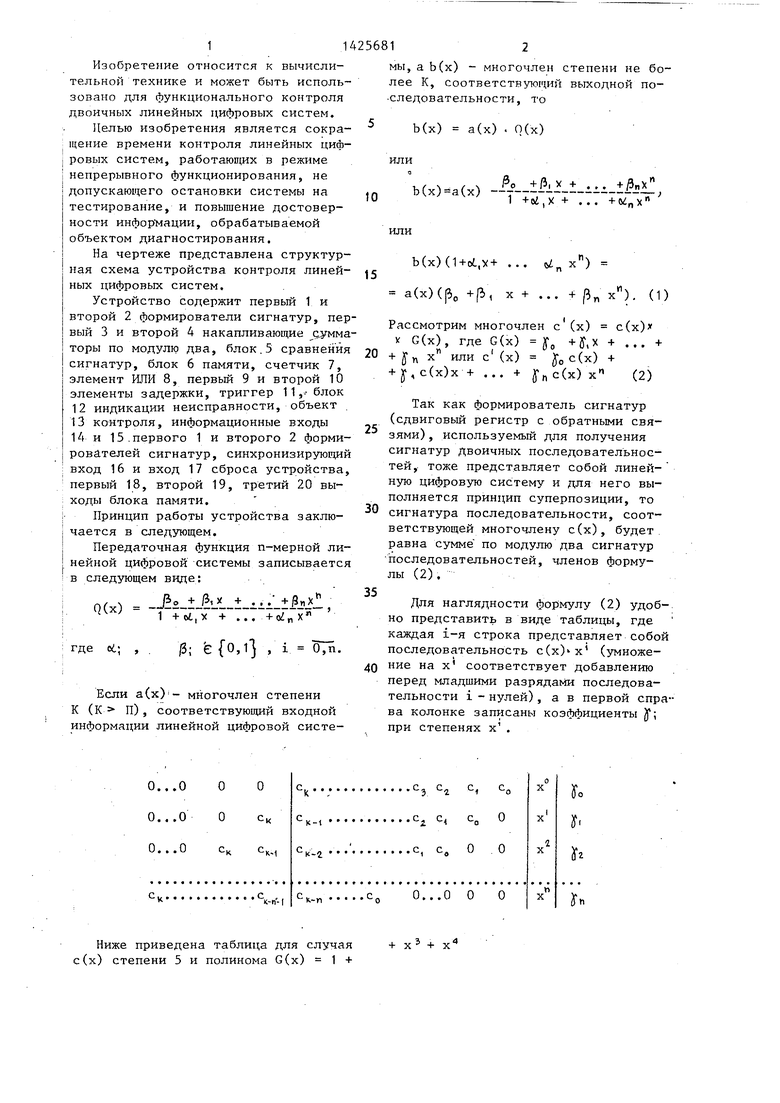

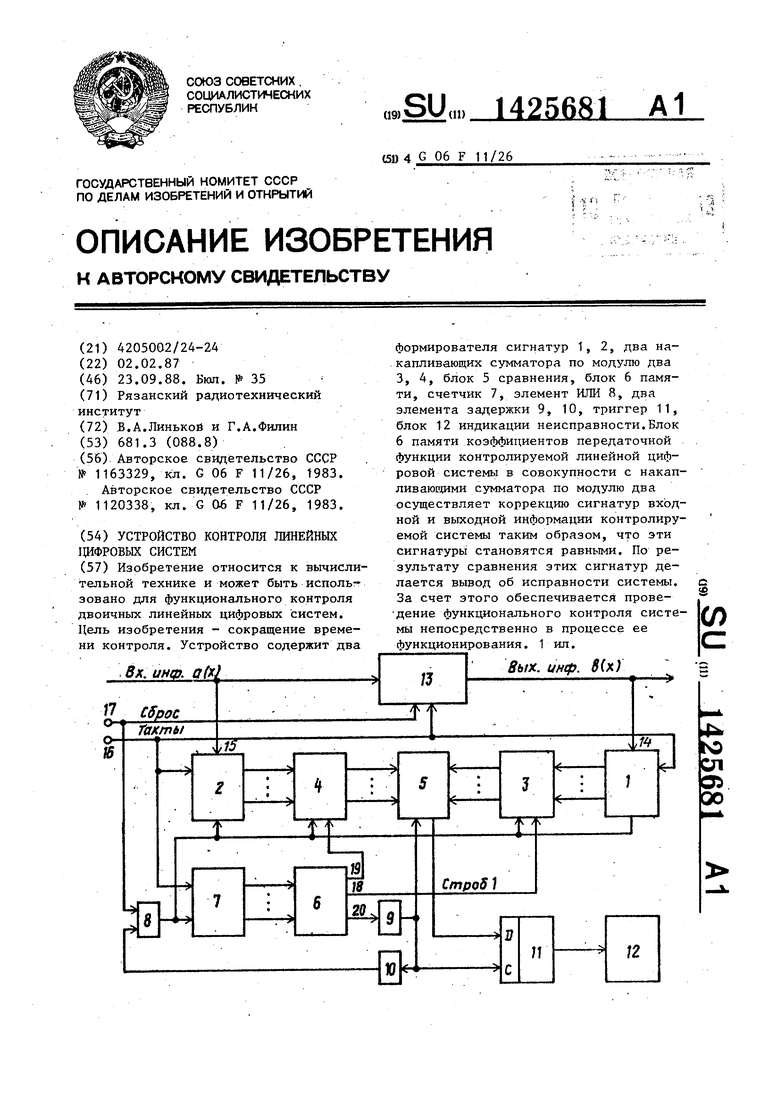

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля двоичных линейных цифровых систем. Цель изобретения - сокращение времени контроля. Устройство содержит два формирователя сигнатур 1, 2, два накапливающих сумматора по модулю два 3, 4, блок 5 сравнения, блок 6 памяти, счетчик 7, элемент ИЛИ 8, два элемента задержки 9, 10, триггер 11, блок 12 индикации неисправности.Блок 6 памяти коэффициентов передаточной функции контролируемой линейной цифровой системы в совокупности с накапливающими сз мматора по модулю два осуществляет коррекцию сигнатур входной и выходной информации контролируемой системы таким образом, что эти сигнатуры становятся равными. По результату сравнения этих сигнатур делается вывод об исправности системы. За счет этого обеспечивается прове- дение функционального контроля системы непосредственно в процессе ее функционирования. 1 ил. о (С (У)

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля двоичных линейных цифровых систем.

Целью изобретения является сокращение времени контроля линейных цифровых систем, работающих в режиме непрерывного функционирования, не допускающего остановки системы на JQ тестирование, и повышение достоверности инфор мации, обрабатываемой объектом диагностирования.

На чертеже представлена структурная схема устройства контроля линей- ных цифровых систем.

Устройство содержит первый 1 и второй 2 формирователи сигнатур, первый 3 и второй 4 накапливающие сумматоры по модулю два, блок.5 сравнения 20 I сигнатур, блок 6 памяти, счетчик 7, I элемент ИЛИ 8, первый 9 и второй 10 I элементы задержки, триггер 11,-- блок

12индикации неисправности, объект

13контроля, информационные входы

мы, а Ь(х) - многочлен степени не более К, соответствующий выходной по- следовательности, то

Ь(х) а(х) . 0(х)

или

Ь(х).а(х) -Ь..-.:,.-, 1 +ог,х + ...

или

b(x)(1+ot,x+ ... bi х) а(х)((5„ , X + ... + х). (1)

Рассмотрим многочлен с (х) сСх)

У G(x), где G(x) у, +у,х + ... + + 3-, х или с (х) JoC(x) + + у,с(х)х + ... + j nc(x)x (2)

Так как формирователь сигнатур

и кинтрил, ишуиАлчсщииппшс 25 регистр с обратными свя- 14 и 15.первого 1 и второго 2 форми- зями), используемый для получения

сигнатур двоичных последовательностей, тоже представляет собой линейную цифровую систему и для него выполняется принцип суперпозиции, то 30 сигнатура последовательности, соответствующей многочлену с(х), будет равна сумме по модулю два сигнатур

ровй-телей сигнатур, синхронизирующий : вход 16 и вход 17 сброса устройства,

первый 18, второй 19, третий 20 вы- ходы блока памяти.

i Принцип работы устройства заклю- I чается в следующем.

I Передаточная функция п-мерной ли- нейной цифровой системы записывается в следующем виде:

: - lJi-+-:L-±LlllL,

: 1 +oi,x + ...

последовательностей, членов формулы (2).

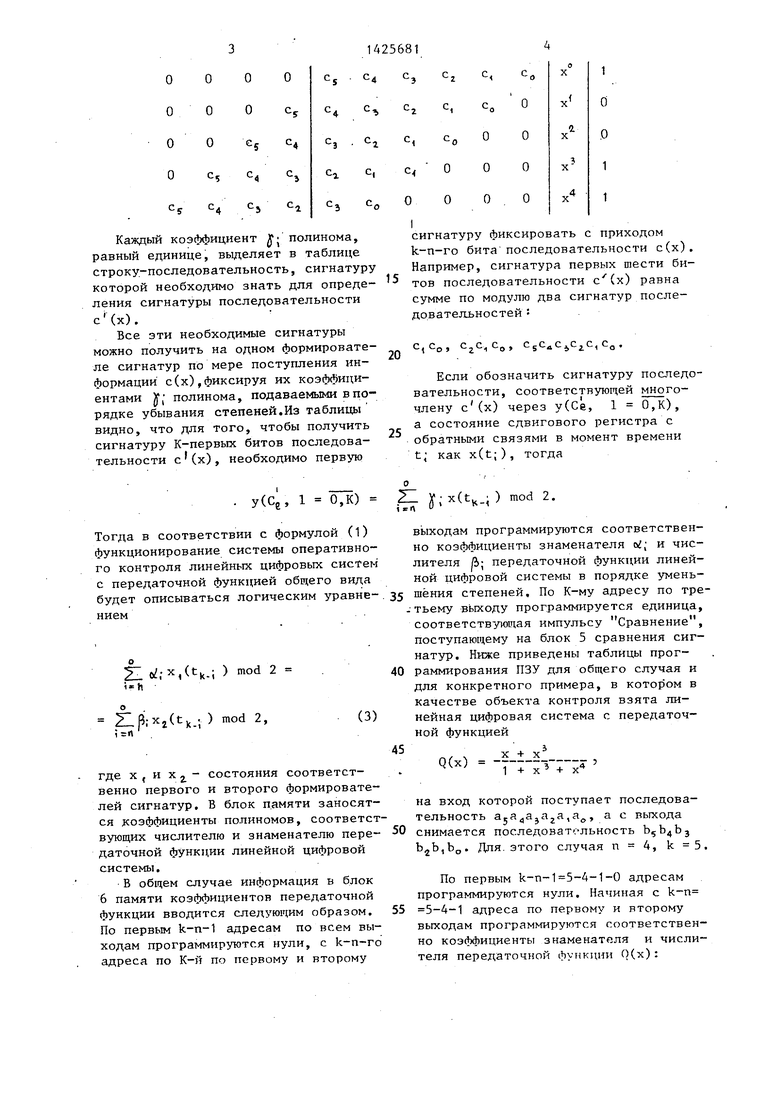

Для наглядности формулу (2) удобно представить в виде таблицы, где каждая i-я строка представляет собой последовательность с(х) х (умноже- 40 чие на х соответствует добавлению перед младшими разрядами последовательности i - нулей), а в первой спра ва колонке записаны коэффициенты У; при степенях х .

где «xL;

/3; е o,i , i о,п.

Если а(х) - многочлен степени К (к П), соответствующий входной информации линейной цифровой систеНиже приведена таблица для случая с(х) степени 5 и полинома G(x) 1 +

мы, а Ь(х) - многочлен степени не более К, соответствующий выходной по- следовательности, то

Ь(х) а(х) . 0(х)

или

Ь(х).а(х) -Ь..-.:,.-, 1 +ог,х + ...

или

b(x)(1+ot,x+ ... bi х) а(х)((5„ , X + ... + х). (1)

Рассмотрим многочлен с (х) сСх)

У G(x), где G(x) у, +у,х + ... + + 3-, х или с (х) JoC(x) + + у,с(х)х + ... + j nc(x)x (2)

последовательностей, членов формулы (2).

Для наглядности формулу (2) удобно представить в виде таблицы, где каждая i-я строка представляет собой последовательность с(х) х (умноже- 0 чие на х соответствует добавлению перед младшими разрядами последовательности i - нулей), а в первой справа колонке записаны коэффициенты У; при степенях х .

+ х + х

С4 С,

Каждый коэффициент Xj полинома, равный единице, выделяет в таблице строку-последовательность, сигнатуру которой необходимо знать для определения сигнатуры последовательности сЧх).

Все эти необходимые сигнатуры можно получить на одном формирователе сигнатур по мере поступления информации с(х),фиксируя их коэффициентами У| полинома, подаваемыми в порядке убывания степеней.Из таблицы видно, что для того, чтобы получить сигнатуру К-первых битов последовательности с (х), необходимо первую

. y(Cg, 1 О,К)

Тогда в соответствии с формулой (1) функционирование системы оперативного контроля линейных цифровых систеь с передаточной функцией o6vi,ero вида будет описываться логическим уравнением

21 ,(t.; ) mod 2

i«h

Zlp..; 2,

где X , и X 2 - состояния соответственно первого и второго формирователей сигнатур, В блок памяти заносятся коэффициенты полиномов, соответствующих числителю и знаменателю передаточной функции линейной цифровой системы,

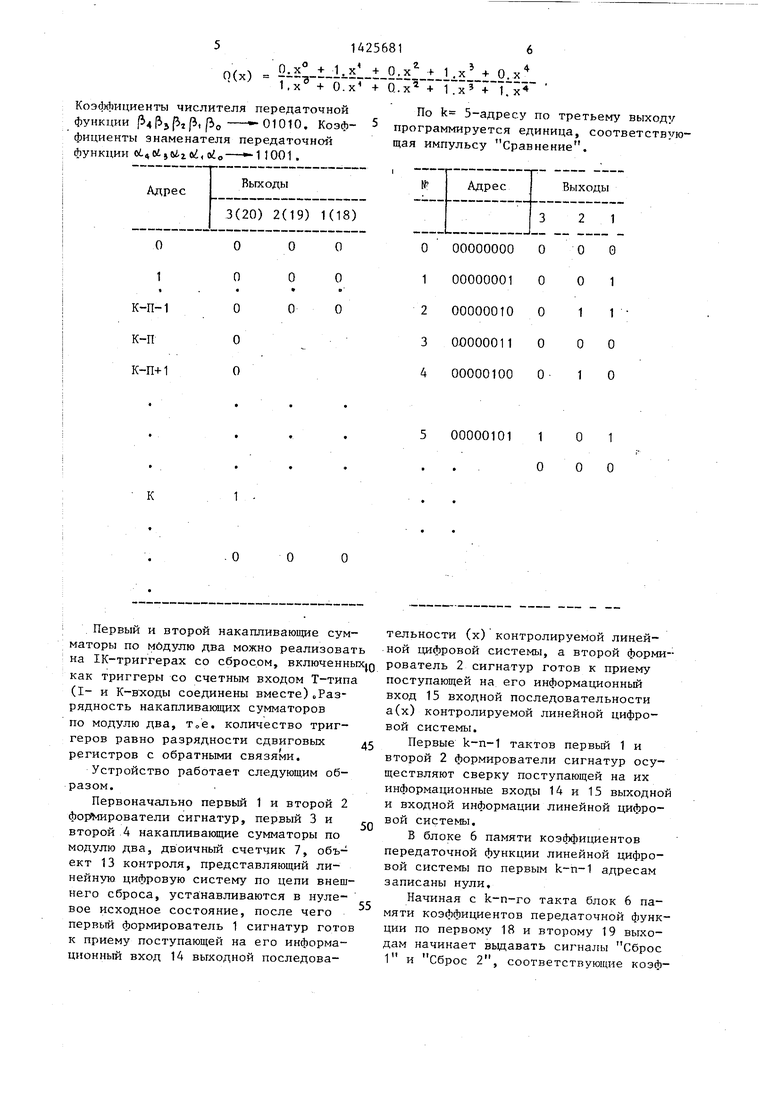

В общем случае информация в блок 6 памяти коэффициентов передаточной функции вводится следующим образом. По первым k-n-1 адресам по всем выходам программируются нули, с k-n-ro адреса по К-й по первому и второму

Cj

Cj

с,

О

1

О .0

1 1

сигнатуру фиксировать с приходом k-n-ro бита последовательности с(х). Например, сигнатура первых шести битов последовательности с (х) равна сумме по модулю два сигнатур последовательностей

20

С C(j , CQ , СдСд с , CQ ,

Если обозначить сигнатуру последовательности, соответствующей много- члену с (х) через у(Се, 1 О,К), а состояние сдвигового регистра с обратными связями в момент времени t; как x(t;), тогда

( r

;х(Ц.;) mod 2.

выходам программируются соответственно коэффициенты знаменателя oi; и числителя ft; передаточной функции линейной цифровой системы в порядке умень35 шёния степеней. По К-му адресу по тре- - тьему вьгходу программируется единица, соответствующая импульсу Сравнение, поступающему на блок 5 сравнения сигнатур. Ниже приведены таблицы прог40 раммирования ПЗУ для общего случая и для конкретного примера, в котором в качестве объекта контроля взята линейная цифровая система с передаточной функцией

J

45

Q(x)

X + X

1 + X + х

на вход которой поступает последовательность а с выхода снимается последоват-.-льность Ь5Ь4Ьз . Для. этого случая п 4, k 5.

По первым k-n-1 5-4-1-0 адресам программируются нули. Начиная с k-n 5-4-1 адреса по первому и второму выходам программируются соответственно коэффициенты знаменателя и числителя передаточной функции 0(х):

514256816

0(х) ..x l.x + О.х + Q.x -h 1.x + 1.x

КоэМтциенты числителя передаточнойПо k 5-адрес.у по третьему выходу

функции 4Р(7Р fio -01010. Коэф- 5 программируется единица, соответствуюфициенты знаменателя передаточнойщая импульсу Сравнение.

функции об . 0 0-11001.

Выходы 3(20) 2(19) 1(18)

000

000 ...

о00

о

о

45

Первый и второй накапливающие сумматоры по модулю два можно реализовать на 1К-триггерах со сбросом, включенных д как триггеры со счетным входом Т-типа (I- и К-входы соединены вместе)„Разрядность накапливающих сумматоров по модулю два, т„е. количество триггеров равно разрядности сдвиговьш регистров с обратными связями.

Устройство работает следующим образом.

Первоначально первый 1 и второй 2 фор мирователи сигнатур, первый 3 и второй 4 накапливающие сумматоры по модулю два, двоичньш счетчик 7, объект 13 контроля, представляющий линейную цифровую систему по цепи внешнего сброса, устанавливаются в нулевое исходное состояние, после чего первьй формирователь 1 сигнатур готов к приему поступающей на его информационный вход 14 выходной последова50

00000000о о о

00000001о о 1

00000010о 11

00000011000

00000100о- 1 о

00000101 1 о 1 00 о

5

д

0

тельности (х) контролируемой линейной цифровой системы, а второй формирователь 2 сигнатур готов к приему поступающей на его информационный вход 15 входной последовательности а(х) контролируемой линейной цифровой системы.

Первые k-n-1 тактов первый 1 и второй 2 формирователи сигнатур осуществляют сверку поступающей на их информационные входы 14 и 15 выходной и входной информации линейной цифровой системы.

В блоке 6 памяти коэффициентов передаточной функции линейной цифровой системы по первым k-n-1 адресам записаны нули.

Начиная с k-n-ro такта блок 6 памяти коэффициентов передаточной функции по первому 18 и второму 19 выходам начинает вьщавать сигналы Сброс 1 и Сброс 2, соответствующие коэф-

фициентам uL и и; знаменателя и числителя передаточной функции линейной цифровой системы, поступающие на первый 3 и второй 4 накапливающие сумматоры по модулю два, разрешающие прохождение в них очередных сигнатур, . снимаемых с первого 1 и второго 2 формирователей сигнатур. Таким образом, в первом 3 и втором А накапли- ваюидах сумматорах по модулю два через k тактов будут получены сигнату0

ры, равные суммам bi;x(t).; ) mod 2

n

о

И (tk-0 ° 2 соответственно.

ittl

С приходом k-ro тактового импульса блок 5 памяти коэффициентов передаточной функции по третьему 20 выходу вьщает сигнал Сравнение, который через второй элемент 10 задержки поступает на стробирующий вход блока 5

tc формационным входом триггера, о т - л и ч а. ю щ е е с я тем, что, с целью сокра1цения времени контроля, устройство содержит второй формирователь сигнатур, два накапливаюпщх сумматора по модулю два и блок памяти, причем информационный вход устройства соединен с информационным ВХОДОМ; второго формирователя сигнатур и является выходом устройства

сравнения сигнатур, разрешая сравнение сигнатур, полученных в первом 3 25 подключения информационного вхо- и втором 4 накапливающих сумматорах по модулю два (таким образом осуществляется проверка равенства (3)). В случае их нераве.нства блок 5 срав30

35

нения сигнатур выдает сигнал неисправности контролируемой линейной цифровой системы, который через триггер 11 поступает в блок 12 ин- дикации неисправности. Импульсом Сравнение через первый элемент 9 задержки элемент ИЛИ 8 осуществляет сброс устройства в нулевое состояние, после чего оно готово к приему следующего слова данных. Второй элемент 10 задержки для того, дО чтобы управляющий сигнал Сравнение поступил на блок 5 сравнения сигнатур с некоторой задержкой относительно сигналов, поступающих на ос- . тальные входы блока 5 сравнения сиг- 45 натур, что повьппает надежность выполнения сравнения. Первый элемент 10 задержки служит для осуществления задержки обнуления блоков 1,2, 3,4,7 на время выполнения операции

да контролируемой системы, первый вход элемента Ш1И соединен с выходом сброса устройства для подключения одноименного входа контролируемой системы, тактовый вход устройства соединен со счетным входом счетчика, синхровходами первого и второго формирователей сигнатур и с тактовым выходом устройства для подключения одноименного входа контролируемой системь, информационный вход первого формирователя сигнатур является входом устройства для подключения выхода контролируемой системы, выход элемента ИЛИ соединен с входами сброса первого и второго формирователей сигнатур и первого и второго накапливающих сумматоров по модулю два, группы информационных выходов первого и второго формирователей сигнатур подключены соответственно к группам информационных входов первого и второго накапливающих сумматоров по модулю два, группы выходов которых подключены соответственно к первой и

, т, / rid 13D H JJlrn:i « 1L CL rl. - сравнения в блоке 5 сравнения сигна- второй группам информационных входов тур, блока сравнения, группа выходов счет.Предлагаемое устройство позволяет реализовать непрерывный функциональный контроль без остановки объекта на тестирование, повысить достоверность результатов обработки данных, увеличить живучесть объекта контроля.

Формула изобретения

Устройство контроля линейных цифровых систем, содержащее первый фор мирователь сигнатур, блок сравнения, два элемента задержки,, элемент ИЛИ, триггер и счетчик, причем вход сброса устройства соединен с первым входом элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу первого элемента задержки и к входу сброса счетчика, выход блока сравнения соединен с инc формационным входом триггера, о т - л и ч а. ю щ е е с я тем, что, с целью сокра1цения времени контроля, устройство содержит второй формирователь сигнатур, два накапливаюпщх сумматора по модулю два и блок памяти, причем информационный вход устройства соединен с информационным ВХОДОМ; второго формирователя сигнатур и является выходом устройства

0

подключения информационного вхо-

да контролируемой системы, первый вход элемента Ш1И соединен с выходом сброса устройства для подключения одноименного входа контролируемой системы, тактовый вход устройства соединен со счетным входом счетчика, синхровходами первого и второго формирователей сигнатур и с тактовым выходом устройства для подключения одноименного входа контролируемой системь, информационный вход первого формирователя сигнатур является входом устройства для подключения выхода контролируемой системы, выход элемента ИЛИ соединен с входами сброса первого и второго формирователей сигнатур и первого и второго накапливающих сумматоров по модулю два, группы информационных выходов первого и второго формирователей сигнатур подключены соответственно к группам информационных входов первого и второго накапливающих сумматоров по модулю два, группы выходов которых подключены соответственно к первой и

i -

чика соединена с группой адресных входов блока памяти, первый, второй и третий информационные выходы которого соединены соответственно с входом разрешения второго накапливающего сумматора по модулю два, входом разрешения первого накапливающего

9142568110

сумматора по модулю два и входом мента задержки, синхровходом тригге- второго элемента задержки, выход ко- ра и стробирующим входом блока срав- торого соединен с входом первого эле- .нения.

| Устройство непрерывного тестового диагностирования линейных цифровых систем | 1983 |

|

SU1163329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-02—Подача