Изобретение относится к вычислительной технике и может быть использовано в системах параллельной обработки информации о,

Целью изобретения является расширение функциональных возможностей за счет обеспечения параллельного доступа к блокам упорядоченной информации переменной длины,,

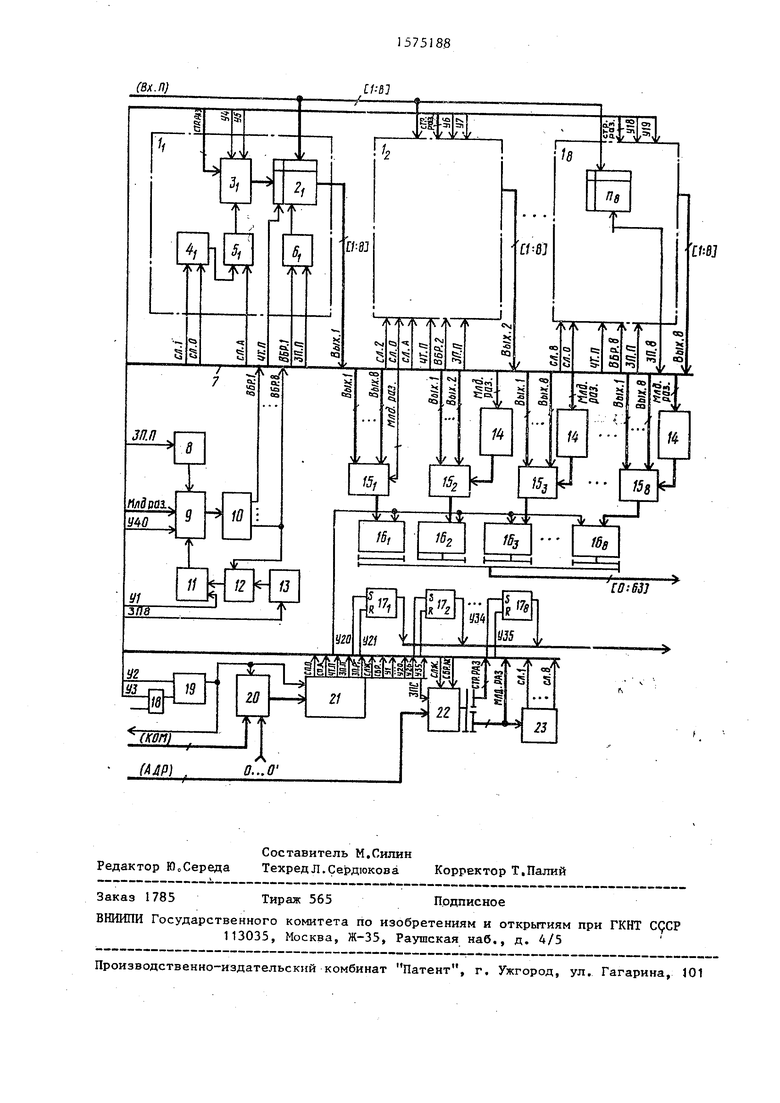

На чертеже представлена функциональная схема предлагаемого устройства,,

Устройство содержит запоминания информации группы (,8, блок 2 у памяти группы, счетчик Зк адреса группы, элемент И 4К группы, элемент ИЛИ 5 k группы, элемент И 6,; группы, магистраль 7 информационных и управляющих сигналов, элемент 8 задержку, счетчик 9, дешифратор 10, элемент ИЛИ 11, элемент И 12, элемент 13 задержки,

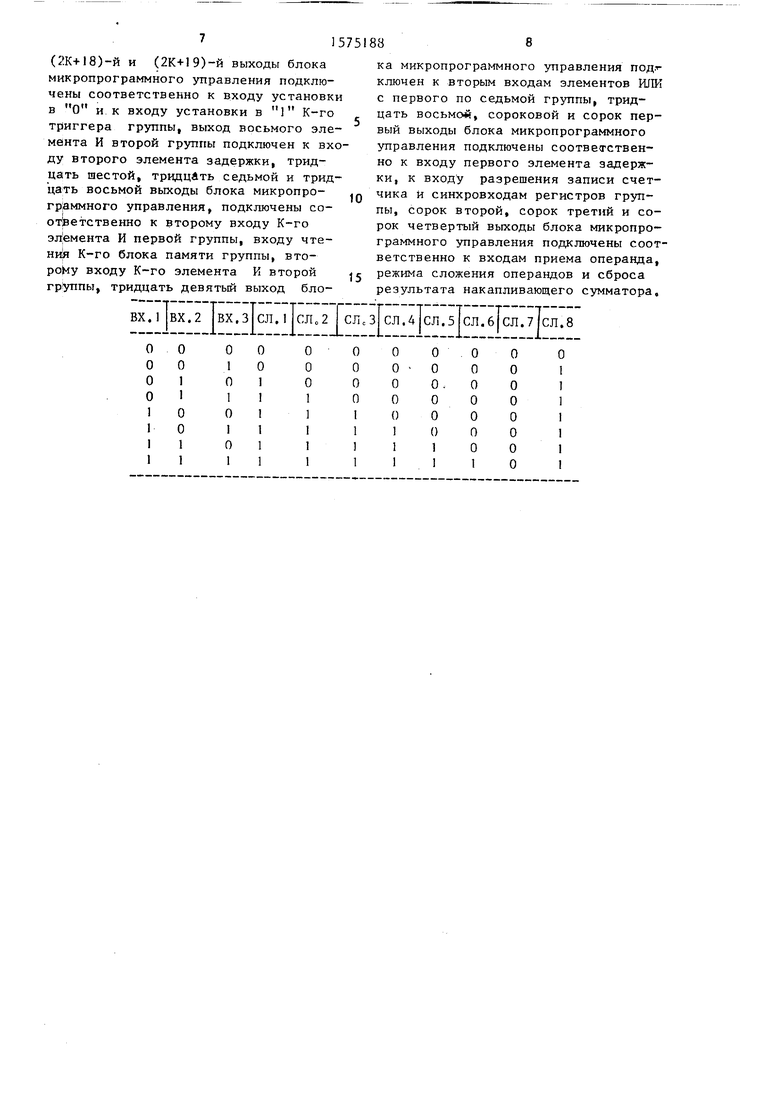

сумматор 14 по модулю восемь группы, мультиплексоры группы, регистры группы, триггеры группы, элемент ИЛИ 18, триггер 19j мультиплексор 20, блок 21 микропрограммного управления, накапливаю- щий сумматор 22, преобразователь 23 дв оичного кода в код управления приращением счетчиков адреса. Преобразователь 23 реализует преобразова- , ние двоичных кодов в соответствии с таблицей и может быть выполнен с использованием логических схем (типа И-НЕ) или ПЗУ.

Цепи начальной установки сброса устройства не показаны

Устройство работает следующим образом.

При чтении информации начальный адрес с входа устройства поступает

СП J Oi

00

оо

на вход сумматора 22. Если в качестве адреса используется смещение относительно текущего адреса, то блок 21 выдает сигнал сложения (СЛЖ) для сложения поступившего смещения с текущим содержимым сумматора 22, Функционирование блока 21 связано с микропрограммной реализацией командыt поступающей на его первый вход Старшие разряды (СТР.РАЗ) сформированного на сумматоре 22 адреса участвуют в определении порядкового номера байта в блоках памяти. При абсолютной адресации запись адреса в сумматоре про изводится сигналом запись (ЗПС), Полный адрес на сумматоре содержит две группы разрядов; СТР.РАЗ соответствующую разрядам адреса, за исключением трех младших разрядов,и МЛД.РАЗ, включающих три младших разряда адре- са, Разряды СТР.РАЗ записываются в счетчики 3 соответствующими управляющими сигналами Y,,.,eY. Далее блок 21 вьщает сигнал СЛ.А, который через элементы ИЛИ 5 поступает на входы увеличения на 1 содержимого счетчиков . Этим обеспечивается вычисление точного порядкового номера байта в блоке при предложении, что этот бай является первым байтом считываемого блока информации, Допустим, что полный адрес блока информации есть 01131 а длина блока - 3 байта, Старшие разряды СТР.РАЗ здесь равны 011. В результате счетчики будут хранить число а счетчик 3g . Дополнительное приращение содержимого счетчиков 3,-39 связано с тем, что первый и второй бай- ты считываемого блока информации являются четвертыми по порядку в соответствующих блоках памяти (седьмом и восьмом соответственно.а третий байт - пятым в блоке 2 памяти, Учет этого обстоятельства производит преобразователь 23, который в данном случа сформирует сигналы на выходе СЛ., СЛ.,1 о В итоге при подаче сигнала СЛ.0 на входы всех элементов И 4 к содержимому счетчиков 3,), 3g бу дет добавлена 1,-как это требуется. Значения остальных счетчиков 3 в данном случае не важны. Далее блок 21 выдает сигнал чтения .памяти (ЧТ.П) на все блоки памяти. Информационные байты с выходов блоков памяти поступают на входы мультиплексоров.15. Задача мультиплексоров - скоммутировать

0

0 5 « 0 , 5

5

считываемые байты так, чтобы байт с - порядковым номером р в рассматриваемом информационном блоке (не смешивать с порядковым номером байта в блоке памяти) попал в регистр 16 р. Управление коммутацией реализуют сумматоры 14л выходы которых соответствуют номерам коммутируемых направлений (блоков памяти), В регистр 16 всегда попадает первьй байт считываемого блока,, номер которого задается разрядами МЛД.РАЗо В регистр 162 коммутируется информация, считываемая из блока с номером МЛДаРАЗ+1 в регистр 16 я из блока памяти с номером ШЩ.РАЗ+2 и Т.ДР

Считываемая информация записывается в регистры 16кК.Триггеры 17,... о 1 Те указывают на наличие в одноименном регистре группы считанного байта в установленном состоянии и на отсутствие полезной информации в противном случае.

Мультиплексор 20 пропускает команду, если триггер 19 сброшен, В противном случае коммутируется нулевая константа. Высокий уровень на выходе триггера 19 поступает на выход признака готовности устройства и используется для синхронизации записи данных в команде записи.

Команда записи информации выполняется следующим образом. На информационный вход устройства выставляется байт записываемого блока информации. Старшие разряды адреса записываются в счетчики 3 сигналами У4, ... ,У4 . Далее блок 21 выдает сигнал СЛ.А, а затем СЛсО, Этим достигается формирование порядковых номеров байтов в счетчиках 3 так жер как и в ранее описанной команде чтения. Параллельно с этим в счетчик 9 записывается номер блока памяти (МЛД.РАЗ) сигналом Y. Соответственно записанному номеру дешифратор 10 возбуждает выход ВБР, который разрешает прохождение сигнала записи ЗП.П через элемент И 6 j, на вход управления записью блока памяти 2„. В случае, когда нужно записывать последовательно несколько байтов (не более восьми), дополнительно к описанному сигнал ЗП.П через элемент 8 поступает на счетный вход счетчика 9„ увеличивая его содержимое на 1, т.е. определяя этим следующий по порядку блок памяти, используемый для записи. Сигналом Y2 блок

515

21 устанавливает в 1 триггер 19. Выход триггера 19 при этом блокирует работу блока 21 и является признаком того, что на информационный вход уст- ройства можно подавать очередной байт, параллельно сбросив триггер 19 Это обеспечит продолжение прерванной работы блока 21, Отметим, что сигнал записи ЗП.8 для блока 35 сбрасы- вает счетчик 9 через элемент 13 и элементы 12 и 11. Величины времен задержек элементов 8 и 13 дожны выбираться равными времени записи в блок памяти.

Формула изобретения

Устройство адресации памяти, содержащее группу регистров, два элемента ИЛИ, триггер, элемент И, счетчик, дешифратор, два элемента задержки, группу блоков памяти, две группы элементов И, причем выход сметчика подключен к входу дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения параллельного доступа к блокам упорядоченной информации переменной длины, в него введены группа элементов ИЛИ, группа счетчиков адреса, группа мультиплексоров, группа сумматоров по модулю восемь, группа триггеров, мультиплексор, блок микропрограммного управления, накапливающий сумматор и преобразователь двоичного кода в код управления приращением счетчиков адреса, причем вход кода команды устройства подключен к первому информационному входу мультиплексора, второй информационный вход, управляющий вход и выход которого подключены соответственно к входу логического нуля устройства, выходу триггера и входу кода команды блока микропрограммного управления, вход запуска устройства подключен к первому входу первого элемента ИЛИ, выход которого подключен к входу установки в 0м триггера, выход которого подключен к входу блокировки блока микропрограммного управления и к выходу признака готовности устройства, вход начального адреса устройства подключен к информационному входу накапливающего сумматора, выход старших разрядов которого подключен к информационным входам счетчиков адреса группы, выход К-го счетчика адреса

g

5

0

5

0

5

0

5

0

5

88

группы подключен к адресному входу К-го блока памяти группы (,8), информационный вход которого подключен к информационному входу устрой- ства, выход младших разрядов накапливающего сумматора подключен к информационному входу счетчика и к входу преобразователя двоичного кода в код управления приращением счетчиков адреса, К-й выход которого подключен к первому входу К-го элемента К первой труп - пы, выход которого подключен к первому входу К-го элемента ИЛИ группы, выход которого подключен к счетному входу К-го счетчика адреса группы, выходы блоков памяти группы с первого по восьмой подключены соответственно к информационным входам мультиплексоров группы с первого по восьмой, выход младших разрядов накапливающего сумматора подключен к управляющему входу первого мультиплексора группы и к входам сумматоров по модулю восемь группы с первого по седьмой, выходы которых подключены соответственно к управляющим входам мультиплексоров группы с второго по восьмой, выход К-го мультиплексора группы подключен к информационному входу К-го регистра группы, выход которого подключен к К-му выходу устройства, выход К-го триггера группы подключен к К-му выходу индикации наличия информации устройства, выход К- го элемента И второй группы подключен к входу записи К-го блока памяти группы вход установки в О и счетный вход счетчика подключены соответственно к выходу второго элемента ИЛИ и к выходу первого элемента задержки, выход второго элемента задержки подключен к первому входу элемента К, t выход которого подключен к первому входу второго элемента ИЛИ, К-й выход дешифратора подключен к первому входу К-го элемента И второй группы, восьмой выход дешифратора подключен к второму входу элемента И, выходы блока микропрограммного управления с первого по третий подключены соответственно к второму входу второго элемента ИЛИ, входу установки в 1 триггера, второму входу первого элемента ИЛИ, (2К+2)-й и (2К+3)-й выходы блока микропрограммного управления подключены соответственно к входу режима приема информации и входу режима счета К-го счетчика адреса группы,

715

(Ж+18)-й и (2К+19)-й выходы блока микропрограммного управления подключены соответственно к входу установки в О и к входу установки в 1 К-го триггера группы, выход восьмого элемента И второй группы подключен к входу второго элемента задержки, тридцать шестой, тридцать седьмой и тридцать восьмой выходы блока микропрограммного управления, подключены соответственно к второму входу К-го элемента И первой группы, входу чтения К-го блока памяти группы, второму входу К-го элемента К второй группы, тридцать девятый выход бло

8

r

ка микропрограммного управления под.ч- ключен к вторым входам элементов ИЛИ с первого по седьмой группы, тридцать восьмой, сороковой и сорок первый выходы блока микропрограммного управления подключены соответственно к входу первого элемента задержки, к входу разрешения записи счетчика и синхровходам регистров группы, сорок второй, сорок третий и сорок четвертый выходы блока микропрограммного управления подключены соответственно к входам приема операнда, режима сложения операндов и сброса результата накапливающего сумматора.

(Вх.П)

L1--&1

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах параллельной обработки информации. Целью изобретения является расширение функциональных возможностей за счет обеспечения параллельного доступа к блокам упорядоченной информации переменной длины. Устройство содержит группу узлов запоминания информации, причем в каждый узел входят блок памяти, счетчик адреса, два элемента И и элемент ИЛИ, магистраль, элементы задержки, счетчик, дешифратор, элементы ИЛИ, элемент И, сумматоры по модулю восемь, группу мультиплексоров, группу регистров, триггер, мультиплексор, блок микропрограммного управления, накапливающий сумматор, преобразователь двоичного кода в код управления приращением счетчика адреса, группу триггеров. 1 ил.

Составитель М.Сюшн Редактор Ю Середа Техред Л. Сердюков а Корректор Т.Палий

Заказ 1785

Тираж 565

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС.СР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Устройство для адресации памяти | 1986 |

|

SU1355977A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для параллельного формирования адресов | 1987 |

|

SU1418711A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-26—Подача