Изобретение относится к связи и может быть использовано в радиотехнических системах для отслеживания фазы принимаемого сигнала.

Целью изобретения является расширение диапазона подстройки.

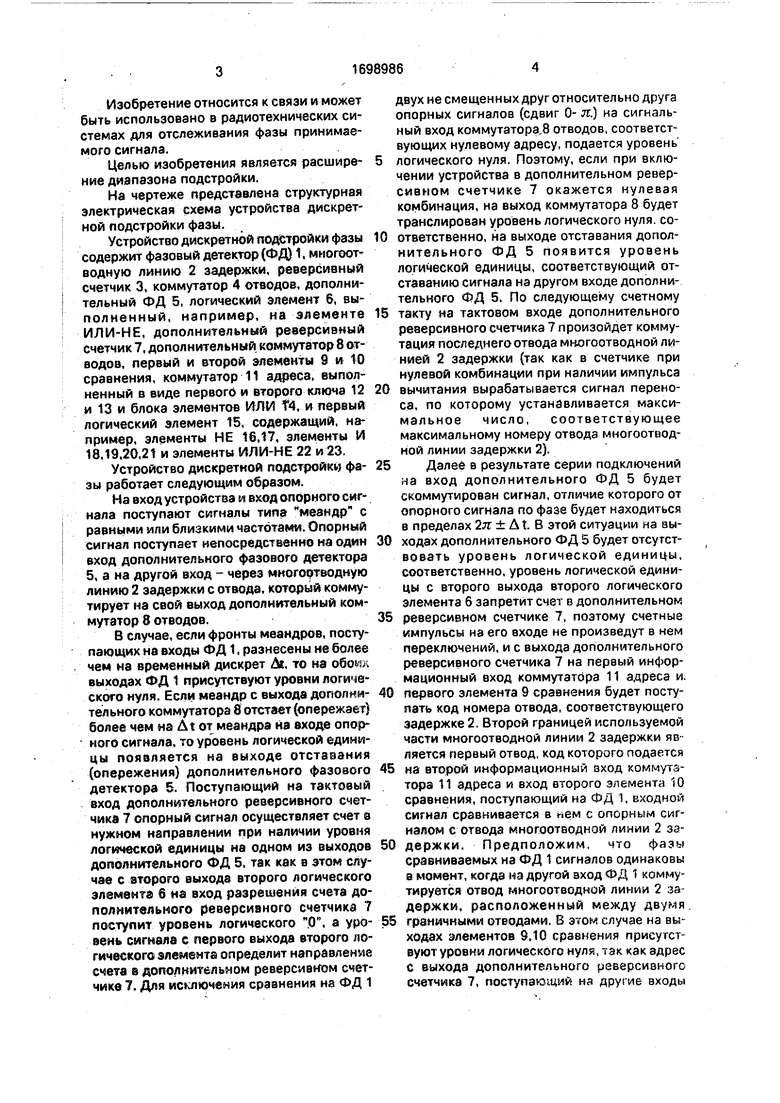

На чертеже представлена структурная электрическая схема устройства дискретной подстройки фазы.

Устройство дискретной подстройки фазы содержит фазовый детектор (ФД) 1, многоотводную линию 2 задержки, реверсивный счетчик 3, коммутатор 4 отводов, дополнительный ФД 5, логический элемент 6, выполненный, например, на элементе ИЛИ-НЕ, дополнительный реверсивный счетчик 7, дополнительный коммутатор 8 отводов, первый и второй элементы 9 и 10 сравнения, коммутатор 11 адреса, выполненный в виде первого и второго ключа 12 и 13 и блока элементов ИЛИ Т4, и первый логический элемент 15, содержащий, например, элементы НЕ 16,17, элементы И 18.19,20,21 и элементы ИЛИ-НЕ 22 и 23.

Устройство дискретной подстройки фазы работает следующим образом.

На вход устройства и вход опорного сигнала поступают сигналы типа меандр с равными или близкими частотами. Опорный сигнал поступает непосредственно на один вход дополнительного фазового детектора 5, а на другой вход - через многоотводную линию 2 задержки с отвода, который коммутирует на свой выход дополнительный коммутатор 8 отводов.

В случае, если фронты меандров, поступающих на входы ФД 1, разнесены не более чем на временный дискрет их., то на обок, выходах ФД 1 присутствуют уровни логического нуля. Если меандр с выхода дополнительного коммутатора 8 отстает (опережает) более чем на At от меандра на входе опорного сигнала, то уровень логической единицы появляется на выходе отставания (опережения) дополнительного фазового детектора 5. Поступающий на тактовый вход дополнительного реверсивного счетчика 7 опорный сигнал осуществляет счет в нужном направлении при наличии уровня логической единицы на одном из выходов дополнительного ФД 5, так как в этом случае с второго выхода второго логического элемента 6 на вход разрешения счета дополнительного реверсивного счетчика 7 поступит уровень логического О, а уровень сигнала с первого выхода второго логического элемента определит направление счета в дополнительном реверсивном счетчике 7. Для исключения сравнения на ФД 1

двух не смещенных друг относительно друга опорных сигналов (сдвиг 0- л:.) на сигнальный вход коммутатора отводов, соответствующих нулевому адресу, подается уровень

логического нуля. Поэтому, если при включении устройства в дополнительном реверсивном счетчике 7 окажется нулевая комбинация, на выход коммутатора 8 будет транслирован уровень логического нуля, соответственно, на выходе отставания дополнительного ФД 5 появится уровень логической единицы, соответствующий отставанию сигнала на другом входе дополнительного ФД 5. По следующему счетному

такту на тактовом входе дополнительного реверсивного счетчика 7 произойдет коммутация последнего отвода многоотводной линией 2 задержки (так как в счетчике при нулевой комбинации при наличии импульса

вычитания вырабатывается сигнал переноса, по которому устанавливается максимальное число, соответствующее максимальному номеру отвода многоотводной линии задержки 2).

Далее в результате серии подключений на вход дополнительного ФД 5 будет екоммутирован сигнал, отличие которого от опорного сигнала по фазе будет находиться в пределах 2л ± At. В этой ситуации на выходах дополнительного ФД 5 будет отсутствовать уровень логической единицы, соответственно, уровень логической единицы с второго выхода второго логического элемента 6 запретит счет в дополнительном

реверсивном счетчике 7, поэтому счетные импульсы на его входе не произведут в нем переключений, и с выхода дополнительного реверсивного счетчика 7 на первый информационный вход коммутатора 11 адреса и.

первого элемента 9 сравнения будет поступать код номера отвода, соответствующего задержке 2. Второй границей используемой части многоотводной линии 2 задержки является первый отвод, код которого подается

на второй информационный вход коммутатора 11 адреса и вход второго элемента 10 сравнения, поступающий на ФД 1, входной сигнал сравнивается в нем с опорным сигналом с отвода многоотводной линии 2 задержки. Предположим, что фазы сравниваемых на ФД 1 сигналов одинаковы в момент, когда на другой вход ФД 1 коммутируется отвод многоотводной линии 2 задержки, расположенный между двумя

граничными отводами. В этом случае на выходах элементов 9,10 сравнения присутствуют уровни логического нуля, так как адрес с выхода дополнительного реверсивного счетчика 7, поступающий на другие входы

элементов 9,10 сравнения, отличается от граничных. На выходах ФД 1 также будут присутствовать уровни логического нуля,

Предположим, что частота меандра на сигнальном входе выше частоты опорного сигнала. В этом случае спустя определенное количество тактов синфазность сигналов на входах ФД -1 нарушится - сигнал, поступающий с выхода коммутатор 4, будет отставать на величину, большую чем At. В результате появится уровень логической единицы на выходе опережения ФД 1 и на втором выходе первого логического элемента 15, который определяет режим сложения в реверсивном счетчике 3. Под воздействием тактов, поступающих с входа опорного сигнала, коммутатор 4 переключает отвод в сторону увеличения номера, после чего в течение некоторого времени наблюдается состояние синфазности. Затем, происходит новое переключение коммутатора. Так, сигнал на выходе коммутатора 4 отслеживает фазу сигнала на входе устройства. Увеличение номера коммутируемого отвода производится до тех пор. пока первый элемент 9 сравнения не зафиксирует равенство кодов. 8 этом случае уровень логической единицы с него откроет второй ключ 13, и код адреса с первого отвода через него и блек элементов ИЛИ 14 поступит на информационные входы реверсивного счетчика 3 Уровень логической единицы первого элемента 9 сравнения поступит также на первый вход первого логического элемента и при очередном нарушении синфазности сигнал с ФД 1 через первый логический элемент 15 установит реверсивный счетчик 3 в заданное состояние, соответствующее адресу первого отвода Таким образом осуществляется закольцсвка многоотводной линии 2 задержки на нужных отводах

В случае, когда частота меандра на входе устройства ниже частоты опорного сигнала, переключение коммутатора 4 при отслеживании фазы входного сигнала осуществляется в прО1ивоположном направлении, т.е. в сторону уменьшения номера отвода при появлении уровня логической единицы на выходе отставания ФД 1, соответственно, уровней логического нуля на входах разрешения счета и направления счета реверсивного счетчика 3 При этом в момент достижения первого отвода многоотводной линии 2 задержки сигнал равенства кодов вырабатывает второй элемент 10 сравнения и открывается первый ключ 12. Дальнейиее отслеживание фазы приводит к переключению на отвод многоотводной линии 2 задержки, код которого поступает из дополнительного реверсивного счетчика

7 через первый ключ 12 и блок элементов ИЛИ 14 на информационный вход реверсивного счетчика 3. Это переключение происходит под воздействием сигнала установки,

посыпающего на реверсивный счетчик 3 с третьего выхода первого логического элемента 15.

Формула изобретения 1, Устройство дискретной подстройки фазы,

0 содержащее фазовый детектор, реверсивный счетчик, многоотводную линию задержки, коммутатор отводов и дополнительный фазовый детектор, вход многоотводной линии задержки, тактовый вход реверсивного счетчика и

5 сигнальный вход коммутатора отводов, соответствующий нулевому адресу, являются входом опорного сигнала, другие сигнальные входы коммутатора отводов соединены с отводами многоотводной линии задержки,

0 его адресные входы присоединены к выходам реверсивного счетчика, а выход - к одному входу фазового детектора, другой вход которого является входом устройства, отличающееся тем, что, с целью расширения

5 диапазона подстройки, в него введены дополнительный реверсивный счетчик, дополнительный коммутато.) отводов, коммутатор адреса, первый я einoof злемон-ы сравнения, первый и второй логические блоки, при0 чем один вход дополнительного фазового детектора и тактовые входы реверсивных счетчиков соединены с входом опорного сигнала, сигнальный вход дополнительного коммутатора отводов соответствующий ну5 левому адресу, является oxjflC f для подачи уровня логического пуля, сигнальные входы дополнительюго i.-ivwyiaropa отводов соединены с ОТРОДЭН-Ч к но-сотводной линии задержки его здре-ные зходы с вы0 ходами дополнительно о реверсивного счетчика, а выход - „ дру и ч Ь .одом дополнительного фазовою дй-емога, одни входы обоих элементов гния соединены с выходами дополнительного реверсивного

5 счетчика, другой вход первого элемента сравнении и первый информационный вход коммутатооа адреса соединены с выходами дополните/иного реверсивного счетчика, другой вход второго элемента сравнения и

0 второй информационный зход коммутатора адреса являются ьходс ДРЯ подали нулевого кода, выход коммутатора подключен к информационному входу реверсивного счетчика у 1равляющке входы коммутатора

5 адреса подключены к выходгм элементов сравнения, первый и второй входы первого логического Блока подключены соответственно к выходам перйого и второго элементов сравнения, третей четвертый входы - к выходам опережения запаздывания фазового детектора соответственно, первый, второй и третий выходы первого логического блока подключены соответственно к ахо- ду записи, входу направления счета и входу разрешения счета реверсивного счегчика, при этом первый логический блок реализует преобразования вида:

Yi /xi + хз//х2 + xV; Ya xi хз;

УЗ « /Х1 + ХЗ//Х2 + ,

гдех1,Х2, хз, х сигналы на первом, втором, третьем и четвертом входах первого логического блока соответственно;

Yi, Y2 и Уд -- сигналы на его первом, втором и третьем выходах соответственно, первый и второй входы второго логического элемента соединены соответственно с выходами опережения и отставания дополнительного фазового детектора, а его первый и второй выходы - с входами направления счета и разрешения счёта дополнительного реверсивного счетчика соответственно, при

этом второй логический элемент выполняет преобразование вида Y$ xs, Ys (xs + xs), где xs м хо - сигналы на выходах опережения и отставания дополнительного фазового де- лектора, a Y и Yg сигналы из его первом и втором выходах соответственно,

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что, коммутатор адреса содержит последовательно соединенные первый ключ и блок элементов ИЛИ, а также второй ключ, выход которого соединен с вторым входом блока элементов ИЛИ, причем информационные входы первогй и второго ключей являются соответственно первым и вторым информационным входами коммутатора адреса, входы управления первого и второго ключей являются управляющими входами коммутатора адресса, а выход блока элементов ИЛИ является выходом коммутатора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Цифровое устройство для фазовой автоподстройки | 1984 |

|

SU1172049A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ГЕНЕРАТОРА ИМПУЛЬСОВ | 2004 |

|

RU2259630C1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2267221C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Цифровой фазометр | 1989 |

|

SU1711090A1 |

Изобретение относится к связи и может быть использовано в радиотехнических системах для отслеживания принимаемого сигнала Це/,ью является расширение диапазона подстройки Устройство содержит два кольца фазовой автоподст- роЛки частоты, одно из которых, содержащее фазовый детектор 1, первый логический элемент 15, реверсивный счетчик 3. коммутатор 4 отводов и многоотводную линию 2 задержки, производит собственно подстройку фазы входного сигнала под опорное колебание, а другое, содержащее дополнительный фазовый детектор 5, второй логический элемент 6, дополнительный реверсивный счетчик 7 и дополнительный коммутатор 8 отводов, служит для определения номера отвода многоотводной линии,2 задержки, соответствующего задержке опорного сигнала на 2л. Цель изобретения достигается ограничением изменения состояния реверсивного счетчика 3 этим номером отвода с помощью коммутатора 11 адреса и первою и второго элементов 9 и 10 сравнения. 1 з.п. ф-лы, 1 ил. сл с Os о 00 о 00 о

| Алексеев Б.П и др Высокочастотный дискретный выделитель тактового синхросигнала | |||

| - Труды НИИР, 1984, N5 1, с.45-48. |

Авторы

Даты

1991-12-15—Публикация

1989-10-23—Подача