Изобретение относится к радиотехнике и может быть использовано в системах синхронизации и когерентт

ных системах связи при высокой частоте сигнала, фаза которого отслеживается.

Целью изобретения является повышение точности фазовой автоподстройки.

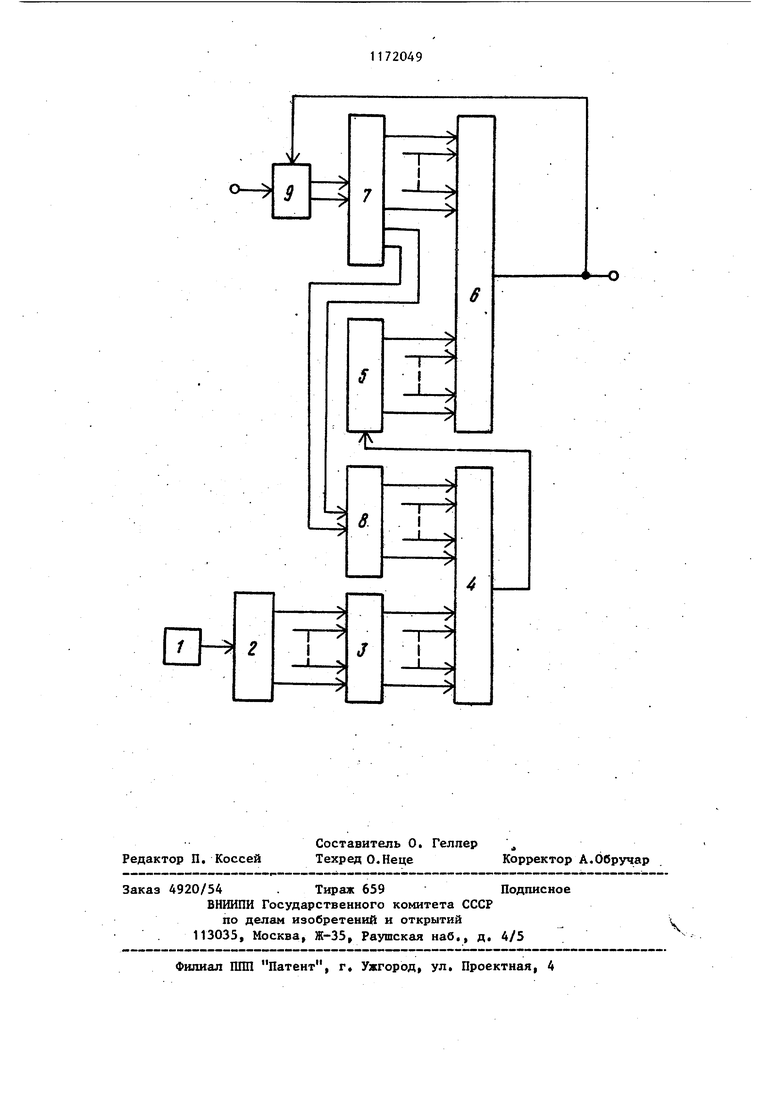

На чертеже изображена структурная электрическая схема предложенного устройства.

Предложенное цифровое устройство .для фазовой автоподстройки содержит задающий генератор 1, счетчик 2, дешифратор 3, первый мультиплексор 4, многоотводную линию 5 задержки, второй мультиплексор 6, первый и второй ревёрсивнь:е счетчики 7 и 8, фазовый дискриминатор 9.

Устройство работает следующим образом.

Входной сигнал, поступающий с входа устройства, сравнивается с выходным сигналом, восстановленным устройством, в фазовом дискриминаторе 9. На вьгходе фазового дискриминатора 9 вырабатываются сигналы ошибки в виде импульсов, которые поступают на входы добавления-вычитания реверсивных счетчиков 7 и 8. Реверсивные счетчики 7 и 8 осуществляют управление мультиплексорами 6 и 4, на информационные входы которых поступают импульсные последовательности с различными начальными фазами. На входах мультиплексора 4 импульсные последовательности с различными начальными фазами формируются с помощью многофазного генератора, включающего последовательно соединенные задающий генератор 1, счетчик 2 и дешифратор 3. На выходе дешифратора 3 частоты следования импульсов

Р f/Nc4, где - частота следования импульсов задающего генератора 1; Nj.(.- коэффициент счета счетчика 1 2 (разность начальньк фаз последовательностей импульсов на двух соседних выходах . дешифратора 3).

Код на выходах разрядов второго реверсивного счетчика 8 разрешает прохождение на выход первого мультиплексора 4 последовательности импульсов с

соответствующей начальной фазой, которая поступает на вход многоотводной линии 5 задержки. Многоотводная лини 5 задержки выполнена в виде последовательно соединенных логических элементов, выход каждого из которых подключен к соответствующему входу второго мультиплексора 6, Суммарное время задержки всех логических элементов 1 1/f определяется временем отставания (опережения) последовательности импульсов на двух ближайших выходах дешифратора 3. Таким образом, первый реверсивный счетчик 7 совместно со вторым мультиплексором 6 осуществляет подстройку начальной фазы последовательности импульсов, поступающей с выхода первого мультиплексора 4 в пределах времени задержки между ближайшими последовательностями импульсов. Ошибка квантования фазы на выходе мультиплексора 6 определяется вьфажением

лЧ ,

где коэффициент счета реверсивного счетчика 8, Коэффициент Np равен количеству логических элементов многоотводной линии 5 задержки. С выхода мультиплесора 6 последовательность импульсов поступает на выход устройства и одновременно на управляющий вход фазового дискриминатора 9 для сравнения с входным сигналом, поступающим с входа устройства-на информациойный вход фазового дискриминатора 9, На выходе устройства формируется сигнал с частотой следования , .выходных импульсов

. F f/Nc«

и максимальной величиной ошибки фазы

uV 360VNc4 +Npc

Очевидно, что величина 1/Npc характеризует выигрьш предлагаемой схемы по сравнению с прототипом.

Изобретение в отличие от прототип позволяет в несколько раз уменьшить величину ошибки фазы выходного сигнала.

- ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ФА ЗОВОЙ АВТОПОДСТРОЙКИ, содержащее задающий генератор, фазовый дискриминатор, выходы которого подключены к соответствующим входам добавлениявычитания первого реверсивного счетчика,отличающееся тем, что, с целью повышения точности фазовой автоподстройки, в него введены второй реверсивный счетчик, многоотводная линия задержки, дешифратор, первый и второй мультиплексоры и счетчик, выходы которого подключены к соответствующим входам дешифратора, выходы которого подключены к первым соответствующим входам первого мультиплексора, вторые входы которого подключены к соответствующим выходам второго реверсивного счетчика, входа добавления-вычитания которого соединены с соответствующими выходами переноса первого реверсивного счетчика, а:дресные выходы которого соединены с соответствующими входами второго мультиi плексора, информационные входы которого подключены к выходам многоотвод(Л ной линии задержки, вход которой соединен с выходом первого мультиплексора, при этом выход задающего генератора подключен к входу счетчика, а выход второго мультиплексора соединен с управляющим входом фазового дискриминатора. (э о 4 СО

| Линдсей У.Ч | |||

| и др | |||

| Обзор цифровых систем автоподстройки частоты | |||

| ТИИЭР, 1980, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-08-07—Публикация

1984-01-05—Подача