ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1644158A1 |

| Устройство для вычисления коэффициентов Фурье | 1980 |

|

SU1098004A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье цифровых фильтров, вычислительных машин с комплексной аП иФмегик и. Целью изобретения является оасширэнмн Функциональных возможностей устройстрэ за счет выполнения операции деления кг плскгных чисел. Устройство содержит э/ ченгы ИЛИ 11, 23, 24. триггеры 12.. 22, узел 15 ончисления обратной величины, элементы И 14, 16, 20. элемент НЕ ,21,ком- мутэторы 17,18. 19, регистры 13.25.26,27,28, 30, умножитель 29 комплексных чисел. 2 ил.

vj

о ел оо ю о

Изобретение относится к вычислительной технике и может быть использовано для построения процессоров быстрого преобразования Фурье, цифропых фильтров, вычислительных машин с комплексной арифметикой.

Цель изобретения - расширение функциональных возможностей за счет выполнения операции деления комплексных чисел.

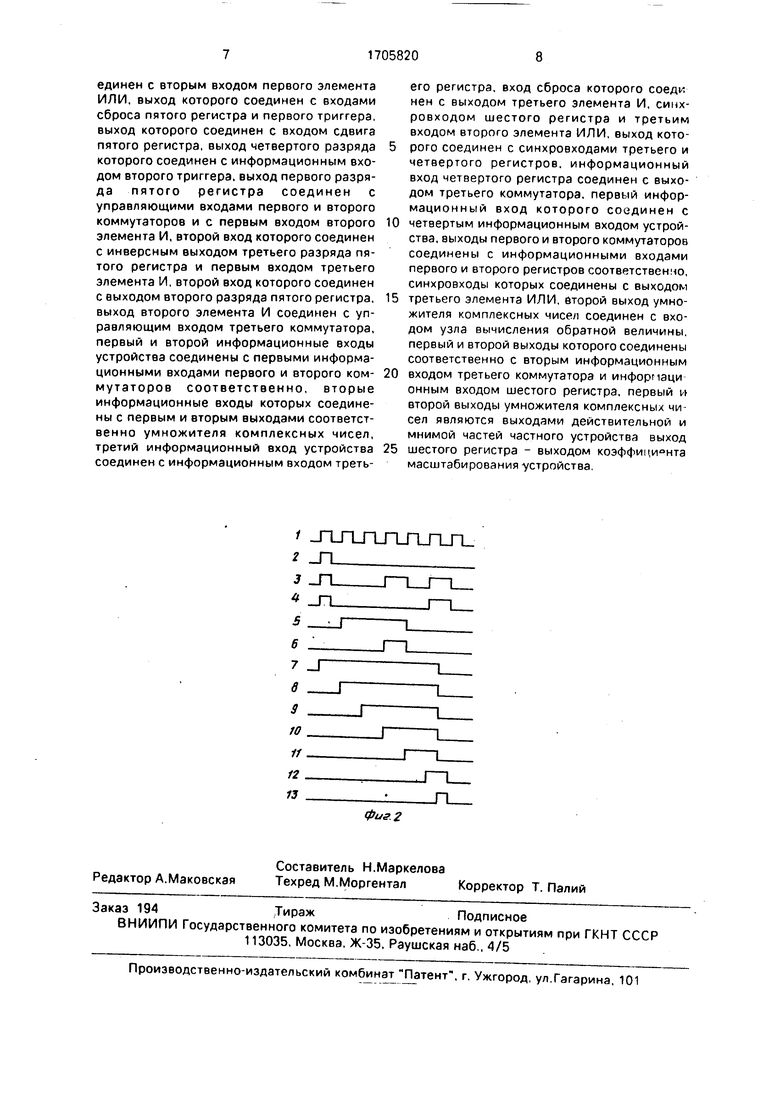

На фиг. 1 представлена функциональная схема вычислительного устройства; на фиг.2 - временная диаграмма выполнения операции деления,

Устройство содержит вход 1 начальной установки, вход 2 кода операции, вход 3 записи кода операции, вход 4 тактовых импульсов, второй 5 и первый б входы разрешения записи информации, первый 7, второй 8, третий 9 и четвертый 10 информационные входы, первый элемент ИЛИ 11, первыйтриггер 12. пятый регистр 13, второй элемент И 14, узел 15 вычисления обратной величины, третий элемент И 16, коммутаторы 17-19, первь.Д элемент И 20, элемент НЕ 21.второй триггер 22, второй и третий элементы ИЛИ 23 и 24, с первого по четвертый регистры 25-28. умножитель 29 комплексных чисел, шестой регистр 30, первый 31, второй 32 и третий 33 информационные выходы устройства.

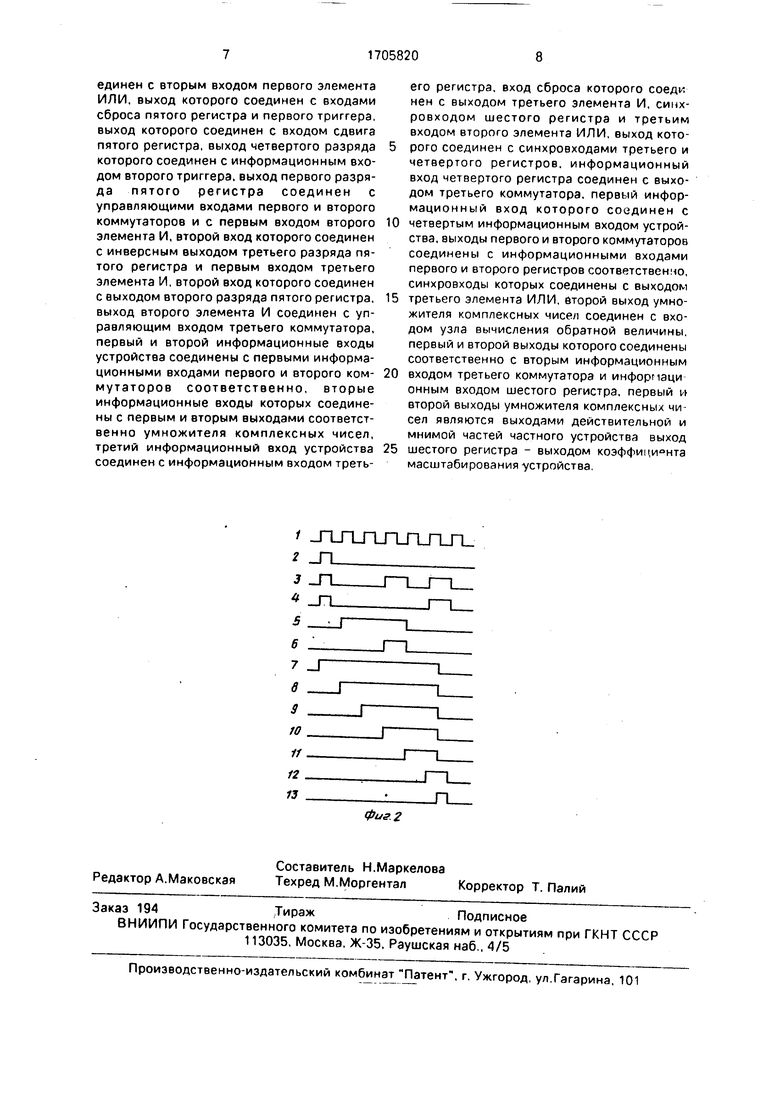

Временная диаграмма (фиг.2) иллюстрирует соотношение сигналов на входах 4(1) и 3(2). на выходах элементов ИЛИ 23(3) и 24(4), на выходах элементов И 14(5), 16(6) и 20(13), на выходах, триггеров 12(7) и 22(12) и на выходах первого (8), второго (9), третьего (10) и четвертого (11) разрядов регистра (13) при выполнении операции деления комплексных чисел.

Устройство работает следующим образом.

Перед началом работы с входа 1 поступает импульс положительной полярности, который устанавливает регистр 13 и триггеры 12 и 22 0 состояние Лог. О. Сигнал Лог. О с выхода первого разряда регистра 13 устанавливает коммутаторы 17-19 в состояние, когда на их выходы поступает информация с первых входов.

Рассмотрим работу устройства при выполнении операции умножения комплексных чисел. На вход 2 кода операции поступает код умножения (Лог, 0), а на информационные входы 7-10 - соответственно действительная (ReCi ai) и мнимая (ImCi 01) части первого числа, действительная (ВеСг 32) и мнимая (imC b2) части второго числа.

По переднему фронту сигналов (перепадов уровней с Лог.О в Лог. 1) на входах

3-6 происходит запись информации в триггер 12 (Лог. О), регистры 25 (ai), 26 (bi), 27 (32) и 28 (b2). Информация с выходов регистров 2S--28 поступает на входы умножителя

29 комплексных чисел, на выходе которого получаем произведение комплексных чисел, действительная часть которого поступает на выход 31, а мнимая - на выход 32. Быстродействие устройства при выполне0 нии операции умножения комплексных-чи- сел определяется быстродействием умножителя 29 комплексных чисел.

Рассмотрим работу устройства при выполнении операции деления комплексных

5 чисел. На вход 2 кода операции поступает код деления (Лог, 1), а на информационные входы 7-10 - соответственно действительная (Red :ai), мнимая (imCi bi), мнимая (imCi bi) и действительная (ReCi ai) части

0 делителя Ст. По переднему фронту сигналов на входах 3-6, которые совпадают с передним фронтом первого тактового импульса, происходит запись информации в триггер 12 (Лог. 1), регистры 25 (ai), 26 (bi), 27 (02)

5 и 28 (ai). Информация с выходов регистров 25-28 поступает на входы умножителя 29 комплексных чисел. По переднему фронту второго тактового импульса Лог.1 с выхода триггера 12 записывается в первый раз0 ряд регистра 13. Сигнал Лог. 1 с выхода первого разряда регистра 13 устанавливает коммутаторы 17-19 в положение, когда на их выходы поступает информация с вторых входов. Перед началом третьего такта на

5 выходах умножителя 29 формируются результаты умножения. Произведение мнимой части данного умножения (ai2 +bi2) поступает на вход узла 15 вычисления обратной величины. По приходу переднего

0 фронта третьего тактового импульса происходит сдвиг информации в регистре 13. В течение третьего такта на первых выходах узла 15 формируется нормализованный ре), который про5

0

5

зультат вычисления

-а2:

ходит через коммутатор 19 и поступает на вход регистра 28. Коэффициент масштабирования, получаемый при нормализации результатов вычисления обратной величины/ --п). формируется на вторых выхо- 4)1 + ЬГ

дах узла 15 и поступает на входы регистра 30.

По переднему фронту четвертого импульса происходит сдвиг информации в ре- гистре 13. Сигнал Лог. 1 с выхода третьего разряда регистра 13 устанавливает на выходе элемента И 16 Лог. 1, которая устанавливает регистр 27 в О, а на выходе

элемента ИЛИ 23 - Лог. 1. Передними фронтами импульсов на синхровходах регистров 28 и 30 производится запись информации в данные регистры. В четвертом такте на входы действительной и мнимой частей первого числа и на входы действительной и мнимой частей второго числа умножителя 29 поступают соответственно at.

01, О и . По приходу переднего фронai +Ь1

та пятого импульса происходит сдвиг информации в регистре 13. Сигнал Лог.О с инверсного выхода четвертого разряда регистра 13 поступает на вторые входы элементов И 14, 16 и устанавливает на их выходах Лог. О. Сигнал Лог. О с выхода элемента И 14 устанавливает коммутатор 19 в положение, когда на его выходы поступает информация с первого входа. В пятом такте на входы 9 и 10 поступают соответственно действительная (Re Сг аг) и мнимая (imC2 b2) части делимого С. На выходах умножителя 29 формируются результаты умножения, которые, проходя через коммутаторы 17 и 18, поступают на входы

31 b1 Ч «Urf

регистров 25 (2- - -)и +ЬГ

По

Л, 27(а2) и 28 (Ь2),

ai + bV N a переднему фронту шестого импульса происходит сдвиг информации в регистре 13 и запись Лог. 1 в триггере 22, которая поступает на второй и третий входы соответственно элементов 24, 23 и устанавливает на их выходах Лог. 1. По переднему фронту сигналов с выходов элементов ИЛИ 23 и 24 происходит запись информации в регистры ое/ а, 2б/ Ы

ги 1-я---х

а1 +bV ai -Некоторая с выходов данных регистров поступает на входы умножителя 29. В шестом такте на выходе элемента И 20 формируется импульс положительной полярности, равный по длительности интервалу между тактовыми импульсами. Сигнал Лог. 1 с выхода элемента И 20 проходит через элемент И 11 и устанавливает триггер 12 и регистр 13 в О. Сигнал Лог. О с выхода первого разряда регистра 13 устанавливает коммутаторы 17 и 18 в положение, когда на их выходы поступает информация с первых входов. По переднему фронту седьмого тактового импульса в триггер 22 записывается Лог. О. В конце седьмого такта на выходах умножителя 29 получаем частное, действи/ Э1Э2 4- blD2 I

тельная часть(--5--ъ которого постуV ъъ 4. н

/aiD2 -azbi)

al+tf пает на выход 31, а мнимая

V

а + ltf

-Jна выход 32. На выходе 33 получаем масш

табирующий коэффициент результата деления.

Деление комплексных чисел в данном устройстве выполняется за время 7 тактов, 5 длительность которых равна т р2 + км + ум.к 2 где tp2 - время записи в регистр;

Ткм - время задержки информации на

10 коммутаторе;

tyM.K - время умножения комплексных чисел.

Предлагаемое устройство эффективно используется при делении комплексных чи15 сел на комплексную константу. При этом деление комплексных чисел на комплексную константу сводится к операции умножения делимого на предварительно вычисленную обратную величину делителя.

20

Формула изобретения Вычислительное устройство, содержащее четыре регистра и умножитель комплексных чисел, причем выходы первого и

25 второго регистров соединены соответственно с входами действительной и мнимой частей первого операнда умножителя комплексных чисел, входы действительной и мнимой частей второго операнда которого

30 соединены с выходами третьего и четвертого регистров соответственно, первый и второй выходы умножителя комплексных чисел соединены с выходом действительной и мнимой частей произведения устройства,

35 отличающееся тем, что. с цепью расширения функциональных возможностей путем выполнения операции деления комплексных чисел, устройство содержит пятый и шестой регистры, два триггера, три

40 коммутатора, узел вычисления обратной величины, потри элемента ИЛИ и И и элемент НЕ, причем вход кода операции устройства соединен с информационным входом первого триггера, сйнхровход которого соеди45 нен с входом записи кода операции устройства, вход начальной установки которого соединен с первым входом первого элемента ИЛИ и входом сброса второго триггера, сйнхровход которого соединен с

50 входом элемента НЕ, синхровходом пятого регистра и входом тактовых импульсов устройства, первый и второй входы разрешения записи устройства соединены с первыми входами второго и третьего эле55 ментов ИЛИ соответственно, вторые входы которых соединены с выходом второго триггера и первым входом первого элемента И. второй вход которого соединен с выходом элемента НЕ, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входами сброса пятого регистра и первого триггера, выход которого соединен с входом сдвига пятого регистра, выход четвертого разряда которого соединен с информационным входом второго триггера, выход первого разряда пятого регистра соединен с управляющими входами первого и второго коммутаторов и с первым входом второго элемента И, второй вход которого соединен с инверсным выходом третьего разряда пятого регистра и первым входом третьего элемента И, второй вход которого соединен с выходом второго разряда пятого регистра, выход второго элемента И соединен с управляющим входом третьего коммутатора, первый и второй информационные входы устройства соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые информационные входы которых соединены с первым и вторым выходами соответственно умножителя комплексных чисел, третий информационный вход устройства соединен с информационным входом треть1 jTjnjTj-Lnj-LTL.

2 П

J Л

его регистра, вход сброса которого соеди нен с выходом третьего элемента И, синх- ровходом шестого регистра и третьим входом второго элемента ИЛИ, выход которого соединен с синхровходами третьего и четвертого регистров, информационный вход четвертого регистра соединен с выходом третьего коммутатора, первый информационный вход которого соединен с

четвертым информационным входом устройства, выходы первого и второго коммутаторов соединены с информационными входами первого и второго регистров соответственно, синхровходы которых соединены с выходом

третьего элемента ИЛИ, второй выход умножителя комплексных чисел соединен с входом узла вычисления обратной величины, первый и второй выходы которого соединены соответственно с вторым информационным

входом третьего коммутатора и информэци онным входом шестого регистра, первый и второй выходы умножителя комплексных чисел являются выходами действительной и мнимой частей частного устройства выход

5 шестого регистра - выходом коэффициента масштабирования устройства.

| Устройство для деления | 1986 |

|

SU1322258A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| - М.: Мир, 1978, с | |||

| СПОСОБ ПОЛУЧЕНИЯ СУБСТАНТИВНЫХ ДЛЯ ХЛОПКА АЗОКРАСИТЕЛЕЙ | 1921 |

|

SU706A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-15—Публикация

1990-05-14—Подача