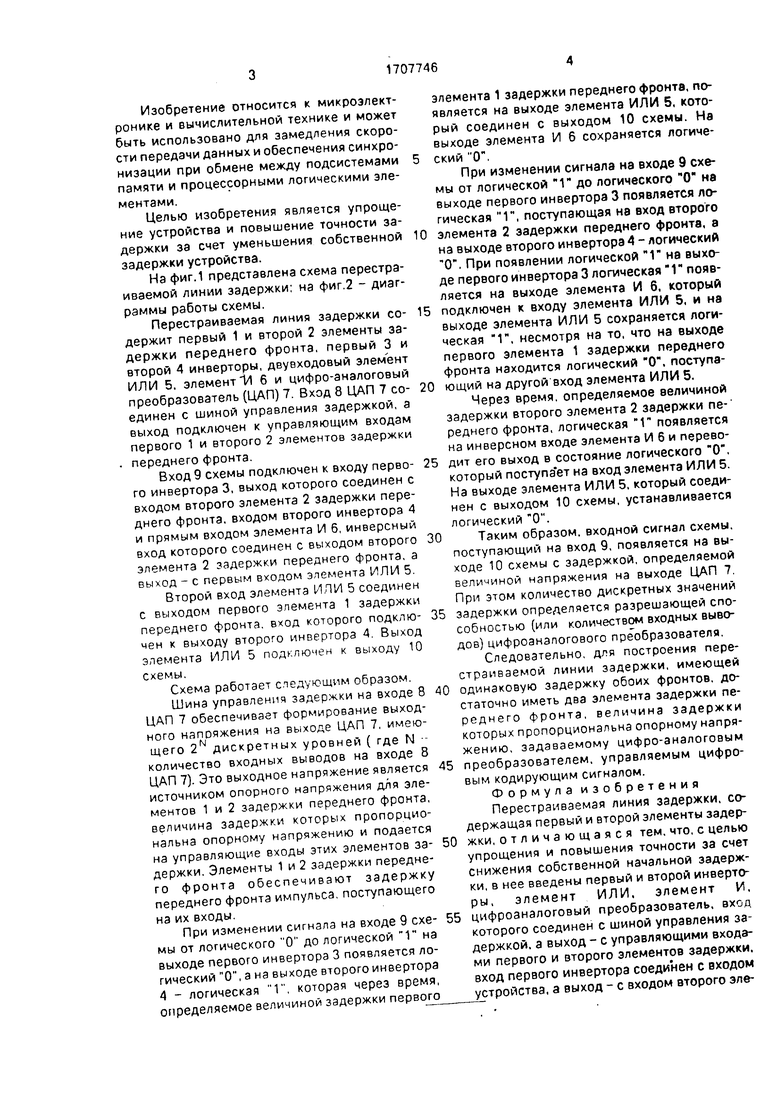

Фиг. I

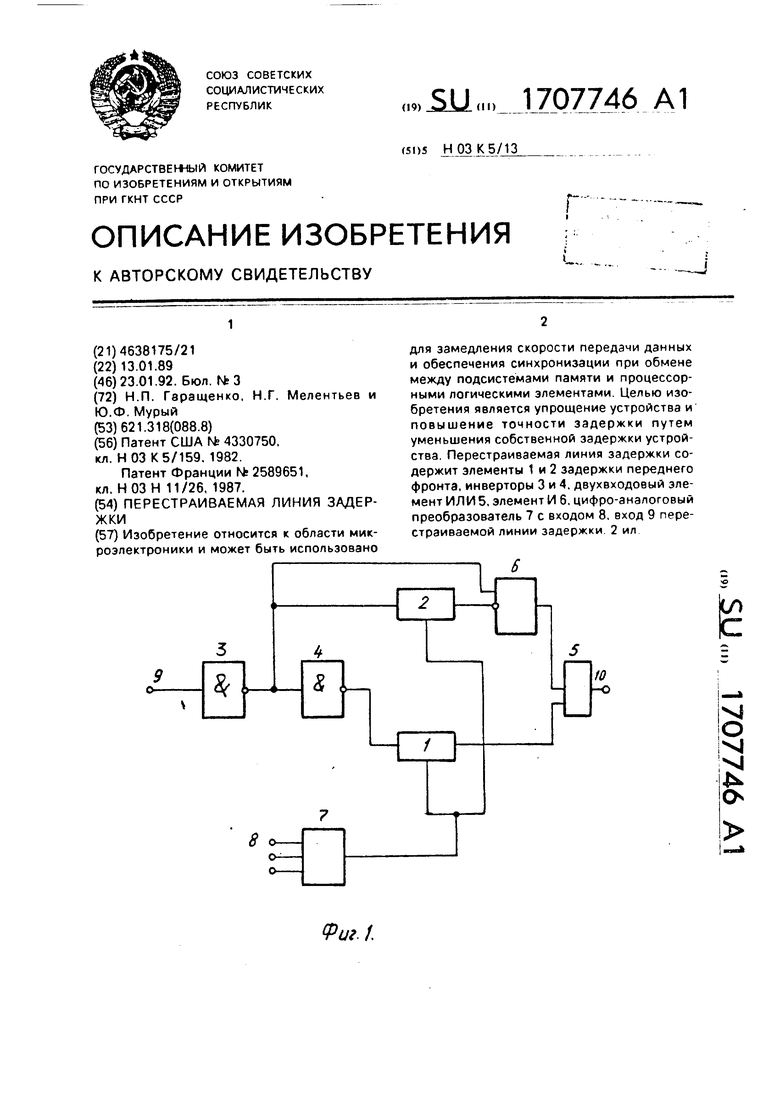

Изобретение относится к микроэлектронике и вычислительной технике и может быть использовано для замедления скорости передачи данных и обеспечения синхронизации при обмене между подсистемами памяти и процессорными логическими элементами.

Целью изобретения является упрощение устройства и повышение точности задержки за счет уменьшения собственной задержки устройства.

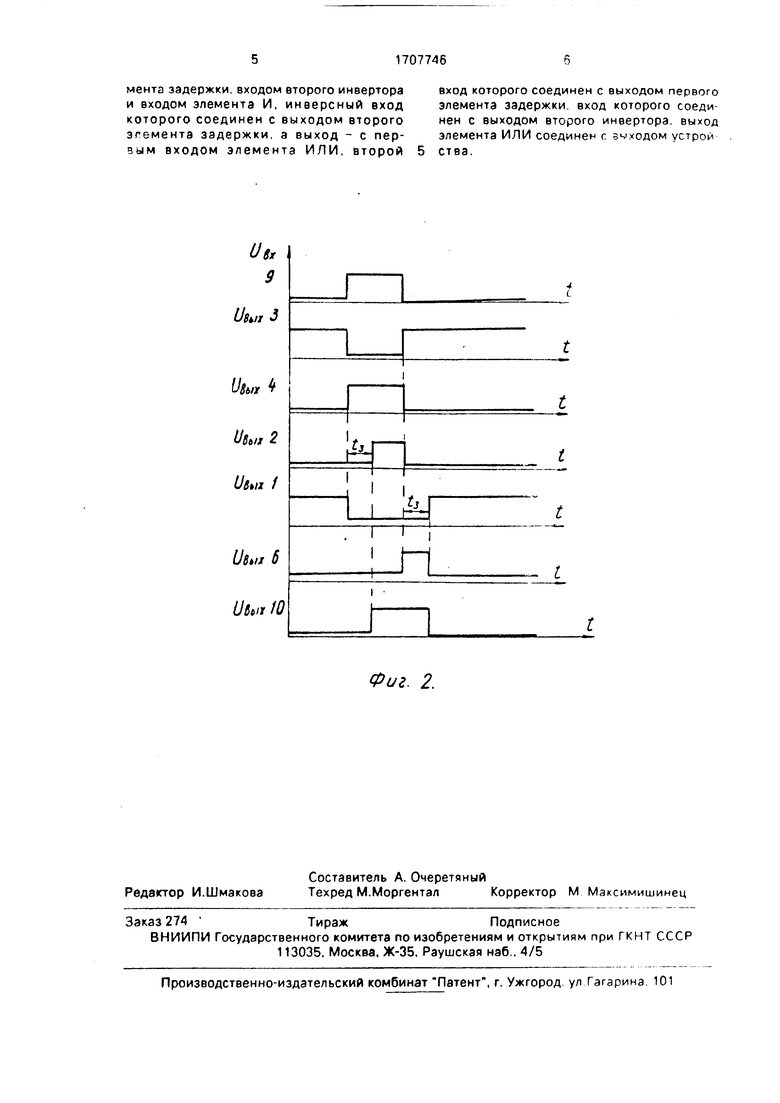

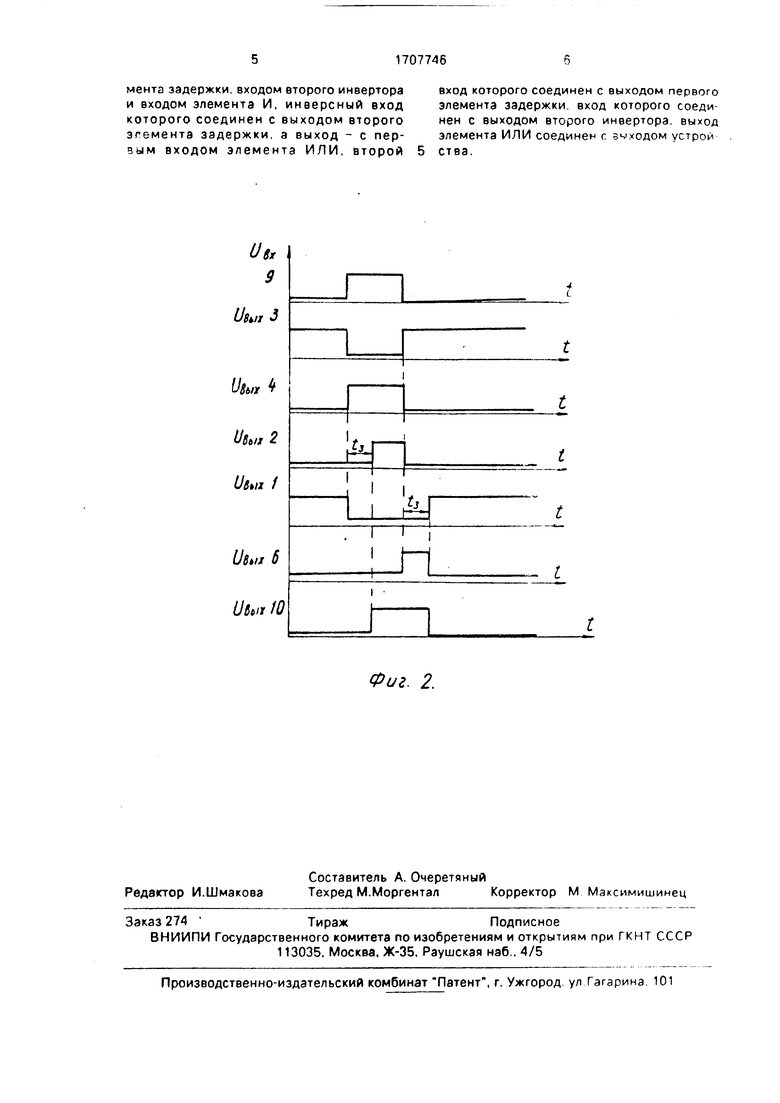

На фиг.1 представлена схема перестраиваемой линии задержки; на фиг.2 - диаграммы работы схемы.

Перестраиваемая линия задержки со- держит первый 1 и второй 2 элементы задержки переднего фронта, первый 3 и второй 4 инверторы, двувходовый элем ент ИЛИ 5, элемент 1/1 6 и цифро-аналоговый преобразователь (ЦАП) 7. Вход 8 ЦАП 7 со- единен с шиной управления задержкой, а выход подключен к управляющим входам первого 1 и второго 2 элементов задержки переднего фронта.

Вход 9 схемы подключен к входу перво- го инвертора 3, выход которого соединен с входом второго элемента 2 задержки переднего фронта, входом второго инвертора 4 и прямым входом элемента И 6, инверсный вход которого соединен с выходом второго элемента 2 задержки переднего фронта, а выход - с первым входом элемента ИЛИ 5.

Второй вход элемента ИЛИ 5 соединен с выходом первого элемента 1 задержки переднего фронта, вход которого подклю- чен к выходу второго инвертора 4. Выход элемента ИЛИ 5 подключен к выходу 10 схемы.

Схема работает следующим образом.

Шина управления задержки на входе 8 ЦАП 7 обеспечивает формирование выходного напряжения на выходе ЦАП 7, имеющего 2N дискретных уровней ( где N - количество входных выводов на входе 8 ЦАП 7). Это выходное напряжение является источником опорного напряжения для элементов 1 и 2 задержки переднего фронта, величина задержки которых пропорциональна опорному напряжению и подается на управляющие входы этих элементов за- держки. Элементы 1 и 2 задержки переднего фронта обеспечивают задержку переднего фронта импульса, поступающего на их входы.

При изменении сигнала на входе 9 схе- мы от логического О до логической Г на выходе первого инвертора 3 появляется логический О, а на выходе второго инвертора 4 - логическая 1, которая через время, определяемое величиной задержки первого

элемента 1 задержки переднего фронта, появляется на выходе элемента ИЛИ 5, который соединен с выходом 10 схемы. На выходе элемента И б сохраняется логический О,

При изменении сигнала на входе 9 схемы от логической 1 до логического О на выходе первого инвертора 3 появляется логическая 1, поступающая на вход второго элемента 2 задержки переднего Фронта, а на выходе второго инвертора 4 - логический О. При появлении логической 1 на выходе первого инвертора 3 логическая Г появляется на выходе элемента И 6, который подключен к входу элемента ИЛИ 5, и на выходе элемента ИЛИ 5 сохраняется логическая 1, несмотря на то, что на выходе первого элемента 1 задержки переднего фронта находится логический О, поступающий на другой вход элемента ИЛИ 5.

Через время, определяемое величиной задержки второго элемента 2 задержки пе- реднего фронта, логическая Г появляется на инверсном входе элемента И 6 и переводит его выход в состояние логического О, который поступа ет на вход элемента ИЛИ 5. На выходе элемента ИЛИ 5, который соединен с выходом 10 схемы, устанавливается логический О.

Таким образом, входной сигнал схемы. поступающий на вход 9, появляется на выходе 10 схемы с задержкой, определяемой величиной напряжения на выходе ЦАП 7. При этом количество дискретных значений задержки определяется разрешающей способностью (или количеством входных выводов) цифроанапогового преобразователя.

Следовательно, для построения перестраиваемой линии задержки, имеющей одинаковую задержку обоих фронтов, достаточно иметь два элемента задержки переднего фронта, величина задержки которых пропорциональна опорному напряжению, задаваемому цифро-аналоговым преобразователем, управляемым цифровым кодирующим сигналом.

Формула изобретения

Перестраиваемая линия задержки, содержащая первый и второй элементы задержки, отличающаяся тем. что, с целью упрощения и повышения точности за счет снижения собственной начальной задержки, в нее введены первый и второй инверторы, элемент ИЛИ. элемент И, цифроаналоговый преобразователь, вход которого соединен с шиной управления задержкой, а выход - с управляющими входами первого и второго элементов задержки, вход первого инвертора соединен с входом устройства, а выход - с входом второго эле

мента задержки, входом второго инверторавход которого соединен с выходом первого

и входом элемента И, инверсный входэлемента задержки, вход которого соедикоторого соединен с выходом второгонен с выходом второго инвертора, выход

эгемента задержки, а выход - с пер-элемента ИЛИ соединен с зшходом устрой

зым входом элемента ИЛИ, второй5 ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕСТРАИВАЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1992 |

|

RU2019912C1 |

| Цифровой следящий привод | 1983 |

|

SU1151925A1 |

| Синтезатор частот | 1985 |

|

SU1358092A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU1023649A1 |

| Генератор гармонических сигналов | 1988 |

|

SU1596428A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1979 |

|

SU955183A2 |

| Цифровой измеритель уровня переменного напряжения | 1984 |

|

SU1226322A1 |

| Устройство для задержки прямоугольных импульсов переменной амплитуды | 1986 |

|

SU1370749A1 |

Изобретение относится к области микроэлектроники и может быть использовано для замедления скорости передачи данных и обеспечения синхронизации при обмене между подсистемами памяти и процессорными логическими элементами. Целью изобретения является упрощение устройства и повышение точности задержки путем уменьшения собственной задержки устройства. Перестраиваемая линия задержки содержит элементы 1 и 2 задержки переднего фронта, инверторы 3 и 4. двухвходовый элемент ИЛИ 5, элемент И 6, цифро-аналоговый преобразователь 7 с входом 8. вход 9 перестраиваемой линии задержки. 2 ил

Фиг. 2.

| Патент США № 4330750 | |||

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| СПОСОБ ДИАГНОСТИКИ ЦЕНТРАЛЬНЫХ ИШЕМИЧЕСКИХ ВЕСТИБУЛЯРНЫХ НАРУШЕНИЙ | 2015 |

|

RU2589651C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-23—Публикация

1989-01-13—Подача