§

СП

00

о ел

с

ОО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Устройство для контроля равновесного кода К из @ | 1987 |

|

SU1559411A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

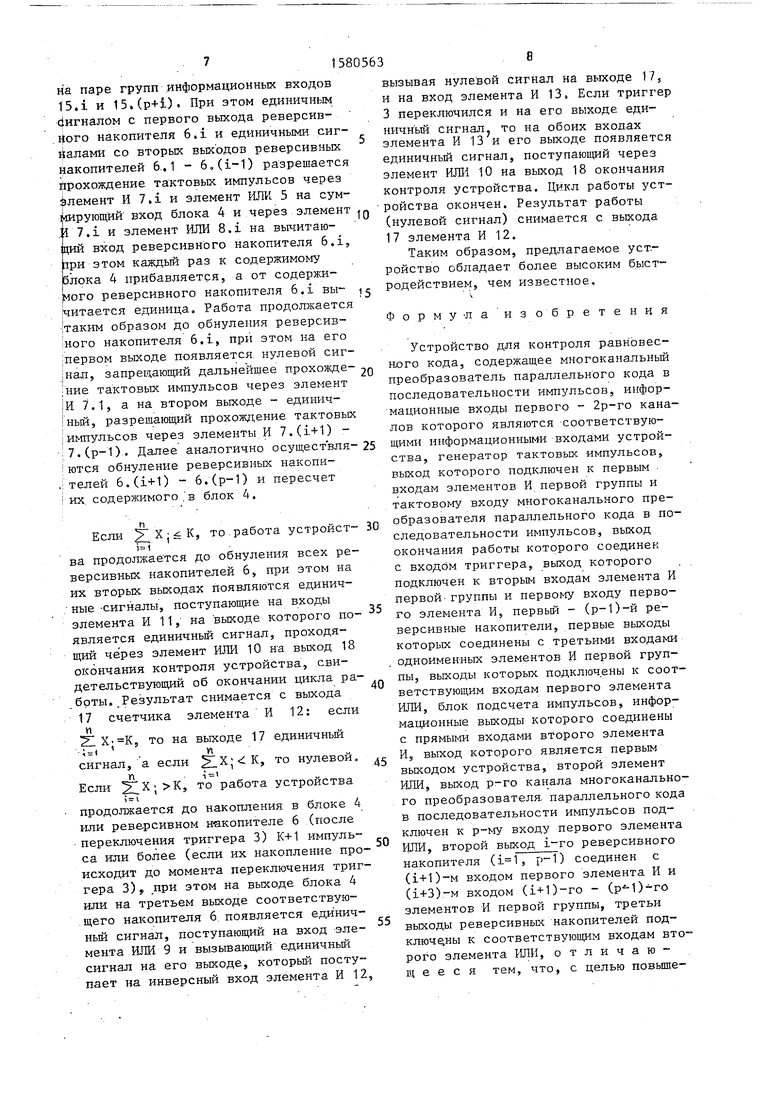

Изобретение относится к автоматике и вычислительной технике. Его использование в системах обработки цифровой информации позволяет повысить быстродействие. Устройство содержит генератор 1 тактовых импульсов, многоканальный преоразователь 2 параллельного кода в последовательности импульсов, триггер 3, блок 4 подсчета импульсов, элементы ИЛИ 5, 9, реверсивные накопители 6, группу 7 элементов И, элементы И 11,12. Поставленная цель достигается благодаря введению элемента ИЛИ 10, элемента И 13, группы элементов ИЛИ 8 и группы элементов И 14. 1 ил.

/sfiW й/ йЦМ «;

;5/до аи; /s/м &IP-I)

Изобретение относится к автомати- се и вычислительной технике и может Ьыть использовано в системах обработ- JCH цифровой информации.Цель изобретения - повышение быстродействия.

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, триг- гер 3, блок 4 подсчета импульсов, |первый элемент ИЛИ 5, реверсивные на- копители 6, первую группу элементов и 7, группу элементов ИЛИ 8, второй 9 и третий 10 элементы ИЛИ, первый - третий элементы И 11-13 и вторую группу элементов И 14. Устройство со- держит информационные 15 и установочные 16 входы, первый 11 и второй 18 выходы.

Устройство предназначено для контроля n-разрядного кода с постоянным числом К единиц.

Многоканальный преобразователь 2 может быть выполнен на распределителе импульсов, выходы которого соединены с первыми входами 2р групп эле- ментов И (2р - число каналов преобразователя) , вторые входы элементов И каждой группы являются информационными входами соответствующего канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которого является выходом соответствующего канала преобразователя 2, тактовый вход распределителя импульсов является тактовым входом преобразова- теля 2, а выход его последнего разряда - выходом окончания работы преобразователя 2.

Многоканальньй преобразователь 2 может быть также выполнен в виде 2р регистров сдвига, соединенных информационными входами с соответствующими информационными входами преобразователя, тактовыми входами - с его тактовым входом, а выходами переноса-с выходами соответствующих каналов преобразователя 2, инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с входами элемента И, выход которого является выходом окончания работы преобразователя 2, входы разрешения записи регистров

сдвига соединены с входами записи преобразователя 2.

Триггер 3 выполняется в виде RS- триггера. Если многоканальный преобразователь 2 выполнен на регистрах сдвига либо на распределителе импульсов, сигнал на выходе окончания работы которого синхронизован с паузой между тактовыми импульсами, или в виде счетного триггера, если преобразователь 2 выполнен на распределителе импульсов, сигнал на выходе окончания работы которого синхронизован с тактовым импульсом.

Реверсивный накопитель 6 может быть выполнен в виде реверсивного счетчика с двумя счетными входами на

(RH), (K+,-) разрядов, соединенного инверсными выходами с входами элемента И, инверсный и прямой выходы которого являются первым и вторым выходами реверсивного накопителя 6, либо прямые выходы реверсивного счетчика соединяются с входами элемента ИЛИ, прямой и инверсный выходы которого являются первым и вторым выходами реверсивного накопителя 6, суммирующий и вычитающий счетные входы счетчика являются соответственно первым и вторым счетным входами реверсивного накопителя 6, прямые выходы счетчика соединены также с входами порогового блока, выход которого является третьим- выходом реверсивного накопителя 6. Пороговый блок реализует пороговую функцию с весами входов 21 и порогом .

В исходном состоянии в счетчик реверсивного накопителя 6.1 с входов 16. i/записывается код числа п р + , входов (р+1)-го канала многоканального преобразователя 2.

Блок 4 подсчета импульсов может быть выполнен в виде реверсивного счетчика с двумя счетными входами на

,,(R+1), (K+1,) разряI

дов, выходы разрядов реверсивного

счетчика являются информационными выходами блока 4, кроме того, прямые выходы разрядов счетчика соединены с входами порогового блока, выход которого является выходом переполнения блока 4. Пороговый блок реализует по- роговую функцию с весами входов 2 и порогом . В исходном состояi 4 записывается код числа q+n2p k -К-1. В этом случае с вхонии с входов 16.р в счетчик блока 4 записан код числа njpвходов (2р)-го канала преобразователя 2.

Кроме того, блок 4 может быть выполнен в виде реверсивного счетчика, причем выходом переполнения блока 4 является прямой выход старшего разряда реверсивного счетчика. В этом случае в исходном состоянии в счетчи блока где q

дами элемента И 12 устройства соединяются прямые выходы разрядов счетчика блока 4 с номерами, равными номерам единичных разрядов в двоичном представлении числа q+K, и инверсные выходы остальных разрядов счетчика блока 4.

Аналогично реверсивный накопитель 6 может быть выполнен без использования порогового блока. При этом он имеет счетчик разрядностью , прямой выход старшего разряда которого является третьим выходом реверсивного накопителя 6, а элемент И реверсивного накопителя 6 соединен входами с прямыми выходами разрядов счетчика с номерами, равными номерам единичных разрядов в двоичном представлении числа q, где -K-1, и инверсными выходами остальных разрядов счетчика, причем прямой выход элемента И является вторым выходом накопителя 6, а инверсный выход - его первым выходом.

Элементы И 14 второй группы могут быть установлены непосредственно на выходах каналов многоканального преобразователя 2.

Устройство функционирует следующим образом.

В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательность импульсов, триггер 3, накопители 6 и блок 4 сброшены. На выходе триггера нулевой сигнал. На информационные входы 15 подан контролируемый код, причем на входы каналов от первого до р-го он подан в прямом виде, а на входы каналов от (р+0-го до (2р)-го - в инверсном виде либо в прямом, но инвертируется установкой инверторов на входах соответствующих каналов много- 1 канального преобразователя 2 либо выполнением соответствующих входов преобразователя 2 инверсным.

g

5

0

При поступлении тактовых импуль - сов на тактовый вход многоканального преобразователя 2 с выхода генератора

1тактовых импульсов преобразователь

2преобразует количество единичных сигналов на информационных входах 15 от первого до р-го и количество нулевых сигналов на информационных входах 15 каналов от (р+1)-го до (2р)-го

в количество импульсов на соответствующих информационных выходах. Импульсы с выхода (2р)-го канала многоканального преобразователя 2 поступают на вычитающий вход блока 4, а с выхода р-го канала - через элемент ИЛИ 5 на суммирующий вход блока 4. Если импульс поступает только на суммирующий или только на вычитающий вход блока 4, то к его содержимому прибавляется или от его содержимого вычитается соответственно единица. Импульсы с выхода 1-го канала многоканального преобразователя 2 поступа- 5 ют на суммирующий вход реверсивного накопителя 6.1, а с выхода (p+i)-ro канала - на вычитающий счетный вход реверсивного накопителя 6.1 через элемент ИЛИ 8.1. Если импульс поступает только на суммирующий вход реверсивного накопителя 6, то к его содержимому прибавляется единица, а если только на вычитающий вход, то от его содержимого вычитается единица. Если импульсы поступают одновременно с выходов 1-го и (р+1)-го или р-го и (2р)-го каналов преобразователя 2, то состояние реверсивного накопителя 6.1 или блока 4 не изменяется благодаря элементам И 14.

Работа продолжается таким образом до окончания преобразования входного кода многоканальным преобразователем 2. По окбнчании преобразования он самоблокируется и далее импульсов на своих информационных выходах не формирует. При этом он сигналом с выхода окончания работы переключает триггер 3, на выходе которого появляется единичный сигнал. Далее происходит процесс последовательного пересчета содержимого реверсивных накопителей 6 в блок 4

Пусть 6.1 наименьший номер реверсивного накопителя, в который записан ненулевой код, причем к моменту окончания работы преобразователя 2 в каждый реверсивный накопитель 6.1 записан код числа единичных сигналов

0

5

0

5

0

S

158

на паре групп информационных входов 15.1 и 15,(p+i), При этом единичным Сигналом с первого выхода реверсивного накопителя 6.1 и единичными сигналами со вторых выходов реверсивных накопителей 6.1 - 6„(1-1) разрешается прохождение тактовых импульсов через Элемент И 7.1 и элемент ИЛИ 5 на суммирующий вход блока 4 и через элемент И 7.1 и элемент ИЛИ 8.1 на вычитающий вход реверсивного накопителя 6.1, три этом каждый раз к содержимому рлока 4 прибавляется, а от содержимого реверсивного накопителя 6.1 вычитается единица. Работа продолжается таким образом до обнуления реверсивного накопителя 6.1, при этом на его первом выходе появляется нулевой сиг

нал, запрещающий дальнейшее прохожде- 2п н-ого кода, содержащее многоканальный

преобразователь параллельного кода в последовательности импульсов, информационные входы первого - 2р-го каналов которого являются соответствующими информационными входами устройства, генератор тактовых импульсов, выход которого подключен к первым входам элементов И первой группы и тактовому входу многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания работы которого соединен с входом триггера, выход которого подключен к вторым входам элемента И первой группы и первому входу первого элемента И, первый - (р-1)-й реверсивные накопители, первые выходы которых соединены с третьими входами одноименных элементов И первой группы, выходы которых подключены к соот ветствующим входам первого элемента ИЛИ, блок подсчета импульсов, информационные выходы которого соединены с прямыми входами второго элемента И, выход которого является первым выходом устройства, второй элемент ИЛИ, выход р-го канала многоканального преобразователя параллельного кода в последовательности импульсов подключен к р-му входу первого элемента ИЛИ, второй выход 1-го реверсивного накопителя (, р-1) соединен с (1+1)-м входом первого элемента И и (1+3)-м входом (1+1)-го - (р-Н)-го элементов И первой группы, третьи выходы реверсивных накопителей под- ключедш к соответствующим входам второго элемента ИЛИ, отличающее с я тем, что, с целью повышение тактовых импульсов через элемент И 7.1, а на втором выходе - единичный, разрешающий прохождение тактовых импульсов через элементы И 7.(1+1) - 7.(р-1). Далее аналогично осуществля-25 ются обнуление реверсивных накопителей 6.(1+1) - 6.(р-1) и пересчет их содержимого в блок 4.

Если 21 X 6 К, то работа устройст1 1

ва продолжается до обнуления всех реверсивных накопителей 6, при этом на их вторых выходах появляются единичные сигналы, поступающие на входы элемента И 11, на выходе которого появляется единичный сигнал, проходящий через элемент ИЛИ 10 на выход 18 окончания контроля устройства, свидетельствующий об окончании цикла работы. Результат снимается с выхода

17 счетчика элемента И 12: если п , то на выходе 17 единичный

i « VI

сигнал, а если lELX K, то нулевой.

n Если , то работа устройства

i V

продолжается до накопления в блоке 4 или реверсивном накопителе 6 (после переключения триггера 3) К+1 импульса или более (если их накопление происходит до момента переключения триггера 3), ,при этом на выходе блока 4 или на третьем выходе соответствующего накопителя 6 появляется единичный сигнал, поступающий на вход элемента ИЛИ 9 и вызывающий единичный сигнал на его выходе, который поступает на инверсньй вход элемента И 12,

563

8

вызывая нулевой сигнал на выходе 17, и на вход элемента И 13. Если триггер 3 переключился и на его выходе единичный сигнал, то на обоих входах элемента И 13 и его выходе появляется единичный сигнал, поступающий через элемент ИЛИ 10 на выход 18 окончания контроля устройства. Цикл работы устройства окончен. Результат работы (нулевой сигнал) снимается с выхода 17 элемента И 12.

Таким образом, предлагаемое устройство обладает более высоким быстродействием, чем известное.

Формула изобретения Устройство для контроля равновесп н-ого кода, содержащее многоканальный

5

0

5

0

5

0

5

преобразователь параллельного кода в последовательности импульсов, информационные входы первого - 2р-го каналов которого являются соответствующими информационными входами устройства, генератор тактовых импульсов, выход которого подключен к первым входам элементов И первой группы и тактовому входу многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания работы которого соединен с входом триггера, выход которого подключен к вторым входам элемента И первой группы и первому входу первого элемента И, первый - (р-1)-й реверсивные накопители, первые выходы которых соединены с третьими входами одноименных элементов И первой группы, выходы которых подключены к соответствующим входам первого элемента ИЛИ, блок подсчета импульсов, информационные выходы которого соединены с прямыми входами второго элемента И, выход которого является первым выходом устройства, второй элемент ИЛИ, выход р-го канала многоканального преобразователя параллельного кода в последовательности импульсов подключен к р-му входу первого элемента ИЛИ, второй выход 1-го реверсивного накопителя (, р-1) соединен с (1+1)-м входом первого элемента И и (1+3)-м входом (1+1)-го - (р-Н)-го элементов И первой группы, третьи выходы реверсивных накопителей под- ключедш к соответствующим входам второго элемента ИЛИ, отличающее с я тем, что, с целью повышения быстродействия, в устройство введены группа элементов ИЛИ, вторая группа элементов И, третий элемент ИЛИ и третий элемент И, первый вход которого подключен к выходу триггера, выходы 2р-го и первого - (р-1)-го каналов многоканального преобразователя параллельного кода в последовательности импульсов соединены COOT- ветственно с прямыми входами 2р-го и первого - (р-1 )-го и инверсными входами р-го - (2р-1)-го элементов И второй группы, выходы (р+1)-го - (2р-1)-го каналов многоканального преобразова- теля параллельного кода в последовательности импульсов соединены с первыми входами соответственно первого - (р-1)-го элементов ИЛИ группы, вторые входы которых подключены к выхо- дам одноименных элементов И первой группы, выходы первого - (р-1)-го элементов ИЛИ группы и первого элемента ИЛИ подключены соответственно к инверсным входам первого - (р-1)-го и 2р-го и прямым входам (р+1)-го (2р-1)-го и р-го элементен И второй группы, выходы 1-го и (p+i)-ro эле- ментов И второй группы , р-1) соединены соответственно с первым и вторым счетными входами 1-го реверсивного накопителя, установочные входы которого являются i-ми установочт ными входами устройства, выходы р-го и 2р-го элемента И второй группы подключены соответственно к первому и второму счетным входам блока подсчета импульсов, установочные входы которого являются р-ми установочными входами устройства, выход переполнения блока подсчета импульсов соединен с р-м входом второго элемента ИЛИ, выход которого подключен к инверсному входу второго элемента И и второму входу третьего элемента И, выход которого и выход первого элемента И соединены с первым и вторым входами третьего элемента ИЛИ, выход которого является вторым выходом устройства.

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом К | 1982 |

|

SU1149260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения ошибок в параллельном п-разрядном коде | 1986 |

|

SU1325480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1987-12-08—Подача