Изобретение относится к цифровой технике и дискретной автоматике и может быть использовано для быстрого пересчета импульсов в двоичном коде.

Известен счетчик со сквозным переносом межразрядной информации (Филиппов А.Г., Белкин О.С. Проектирование логических узлов ЭВМ. М.: Сов. радио, 1974, с. 150, рис. 2.87.), содержащий в каждом из разрядов триггер, а в разрядах, начиная с третьего двухвходовый логический элемент И, причем синхровход счетчика соединен с С-входами всех триггеров, выход логического элемента И каждого разряда соединен с Т-входом триггера этого же разряда. Достоинством этого счетчика является простота и регулярность межразрядных связей, а основным недостатком является низкое быстродействие: Тмин=tп+(N-2)tзи,

где Тмин - минимальный период следования синхроимпульсов;

tп - время переключения триггера разряда;

tзи - задержка логического элемента И.

Известно счетное устройство (Брайловский Г.С., Лазер И.М. Счетное устройство. Авт. свидетельство СССР №1529445, Н03К 23/40 - «БИ», 1989, №46.) содержащее счетчик и счетные разряды, каждый из которых содержит триггер, а в разрядах, начиная с третьего - логические элементы И-НЕ и ИЛИ-НЕ. Существенным недостатком этого устройства является его сложность, обусловленная большим количеством межразрядных связей и использованием разнотипных логических элементов И-НЕ и ИЛИ-НЕ. Кроме того, для формирования сигнала переноса в разрядах используются как прямые так и инверсные выходы триггеров, что значительно затрудняет реализацию этого устройства в ПЛИС. Поскольку среди библиотечных элементов в ПЛИС, например, семейства Spartan, содержатся триггеры только с прямым выходом, то для организации инверсого выхода потребуется n/2 логических элементов НЕ и n связей, что еще больше усложняет реализацию этого устройства в ПЛИС.

Известен счетчик с параллельным (одновременным) переносом межразрядной информации (Филиппов А.Е., Белкин О.С. Проектирование логических узлов ЭВМ. М.: Сов. радио, 1974, с. 151, рис. 2.88, а так же Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. - 4-е изд., перераб. и доп. М.: Техносфера, 2009, с. 194, рис. 5.9, а.), содержащий в каждом из разрядов триггер, а в разрядах, начиная с третьего логический элемент И, причем синхровход счетчика соединен с С-входами всех триггеров, выход логического элемента И каждого разряда соединен с Т-входом триггера этого же разряда, а с входами логического элемента И каждого разряда соединены выходы триггеров всех предыдущих разрядов. Этот счетчик относится к категории наиболее быстродействующих синхронных счетчиков. Основными недостатками этого счетчика является большое количество связей, зависимость нагрузочной способности по выходам от числа разрядов и необходимость применения многовходовых логических элементов И для формирования сигналов переноса межразрядной информации. Так, например, для N-го разряда требуется (N-1)-входовый логический элемент И.

Наиболее близким по технической сущности к заявляемому изобретению является, выбранный в качестве прототипа, счетчик с параллельным (одновременным) переносом межразрядной информации (Букреев И.Н., Горячев В.И. Мансуров Б.М. Микроэлектронные схемы цифровых устройств. - 4-е изд., перераб. и доп. М.: Техносфера, 2009, с. 194, рис. 5.9, б.), содержащий в каждом из разрядов триггер, а в разрядах, начиная с i-го (i=3, 4, …, N) содержит m=(i-2)-двухвходовых логических элементов И, причем сипхровход счетчика соединен с С-входами всех триггеров, в i-ом разряде со вторым входом m-го (m=1, 2, …, i-2) логического элемента И соединен выход (m+1)-го логического элемента И этого же разряда, с первым входом m-го логического элемента И i-го разряда соединен выход триггера (i-2)-го разряда, а с первым входом (i-2)-го логического элемента И i-го разряда соединен выход триггера (i-1)-го разряда, выход первого логического элемента И i-го разряда соединен с Т-входом триггера этого же разряда. В этом счетчике, по сравнению с предыдущим счетчиком, используются лишь двухвходовые логические элементы И, что исключает необходимость применения многовходовых логических элементов И. Основным недостатком этого счетчика является сложность его реализации, обусловленная большим количеством связей и оборудования (двухвходовых логических элементов И). Так для реализации N-разрядиого счетчика требуется (N-1)⋅(N-2)/2-двухвходовых логических элементов И и (N-1)⋅(N-2) связей.

Цель изобретения - упрощение устройства.

Цель достигается тем, что в счетчик, содержащий в каждом из разрядов триггер, во втором разряде - логический элемент И, а в каждом из последующих разрядов - два логических элемента И, синхровход счетчика соединен с С-входами всех триггеров, причем выход триггера первого разряда соединен с первым входом логического элемента И второго разряда и с первым входом второго логического элемента И третьего разряда, выход второго логического элемента И каждого разряда соединен с первым входом первого логического элемента И этого же разряда, выход триггера второго разряда соединен с вторым входом второго логического элемента И третьего разряда, выход первого логического элемента И каждого разряда соединен с Т-входом триггера этого же разряда. В него введен к-разрядный счетчик, С-вход которого соединен с синхровходом счетчика, а выход переноса - с Т-входом триггера первого разряда и со вторым входом первого логического элемента И каждого из последующих разрядов, а в каждом из разрядов, начиная с третьего, выход триггера и второго логического элемента И соединены соответственно с первым и вторым входами второго логического элемента И следующего разряда.

Сопоставительный анализ технического решения с устройством, выбранным в качестве прототипа, показывает, что новизна технического решения заключается в интеграции в заявляемое устройство к-разрядного счетчика с выходом сигнала переноса и оптимизации оборудования (количества двухвходовых логических элементов И в разрядах).

Таким образом, заявляемое техническое решение соответствует критерию изобретения «новизна».

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные схемные элементы известны. Однако введение их в счетчик с указанными связями придает ему новые свойства, а именно, позволяет реализовывать на практике многоразрядные счетчики предельного быстродействия с минимальным количеством оборудования и связей.

Таким образом, техническое решение соответствует критерию ''изобретательский уровень'', так как оно для специалиста явным образом не следует из уровня техники.

Изобретение касается построения узлов цифровой техники и дискретной автоматики на Т-триггерах и двухвходовых логических элементах И и может быть реализовано преимущественно в БИС и ПЛИС.

Таким образом, изобретение соответствует критерию ''промышленная применимость''.

Счетчик содержит в каждом из разрядов 1=1-1=m триггер, во втором разряде 1=2 - логический элемент И 2=2, а в каждом из последующих разрядов 1=3-1-m - два логических элемента И 2=3 и 3=3, синхровход счетчика 4 соединен с С-входами всех триггеров, причем выход триггера первого разряда 1=1 соединен с первым входом логического элемента И 2=2 второго разряда 1=2 и с первым входом второго логического элемента И 3=3 третьего разряда 1=3, выход второго логического элемента И каждого разряда соединен с первым входом первого логического элемента И этого же разряда, выход триггера второго разряда 1=2 соединен с вторым входом второго логического элемента И 3=3 третьего разряда 1=3, выход первого логического элемента И каждого разряда соединен с Т-входом триггера этого же разряда, к-разрядный счетчик 5 с параллельным переносом, С-вход которого соединен с синхровходом счетчика 4, а выход переноса - с Т-входом триггера первого разряда 1=1 и со вторым входом первого логического элемента И каждого из последующих разрядов 1=2-1=m, а в каждом из разрядов 1=3-1=m-1, выход триггера и второго логического элемента И соединены соответственно с первым и вторым входами второго логического элемента И следующего разряда.

Работает счетчик следующим образом.

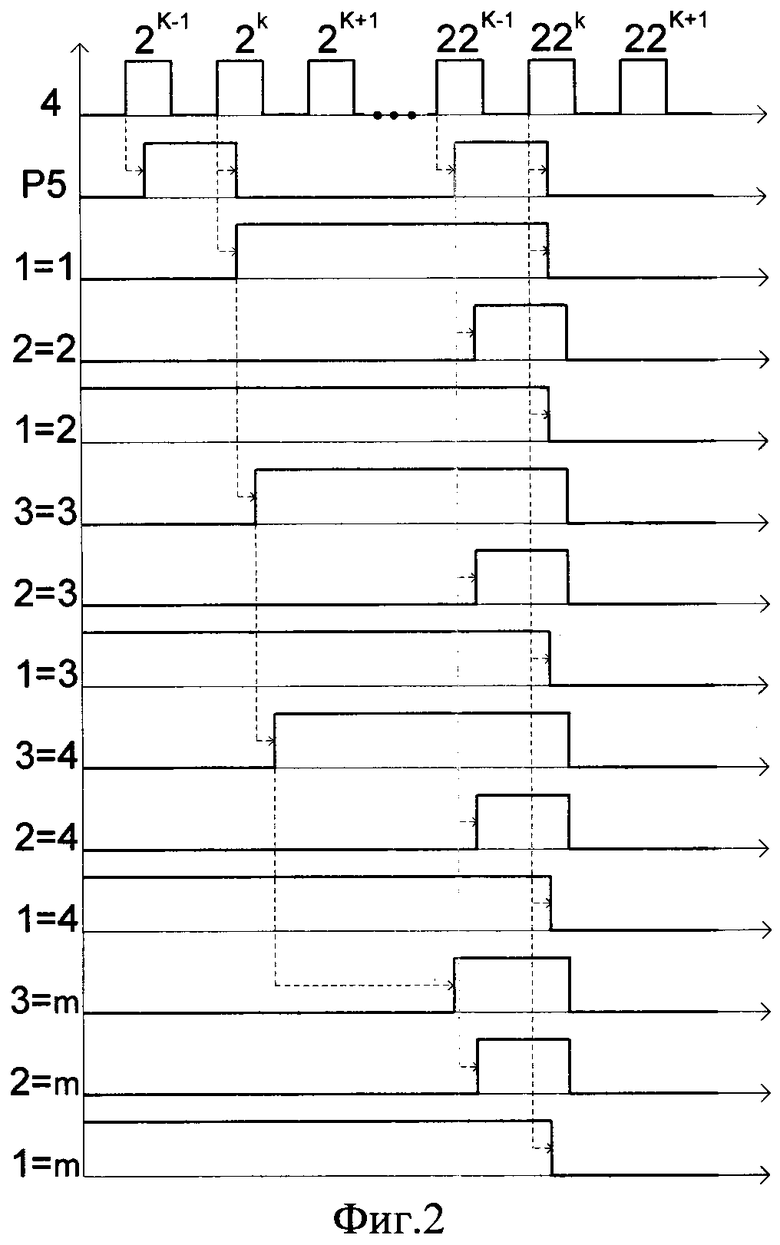

Прямой взвешенный N-разрядный код счетчика (фиг. 1) формируется на к-прямых выходах счетчика 5 и m-прямых выходах триггеров разрядов 1=1-1=m. Функционирование счетчика поясняется временной диаграммой (фиг. 2), на которой представлены счетные импульсы на синхровходе 4 с номерами 2к-1, 2к, 2к+1, …, 2⋅2к-1, 2⋅2к, 2⋅2к+1. Из-за ограниченных размеров временной диаграммы на ней показан наихудший случай, когда к моменту поступления на синхровход 4 2к-го счетного импульса на выходе триггера разряда 1=1 установился лог.0, а выходах разрядов 1=2-1=m - лог.1. По фронту 2к-го счетного импульса при наличии сигнала переноса Р на выходе счетчика 5, равного лог.1, на выходе триггера разрядов 1=1 устанавливается лог.1 и по цепи из логических элементов 3=3, 3=4, …, 3=m начинает распространяться сигнал сквозного переноса, равный лог.1. Для обеспечения предельного быстродействия N-разрядного счетчика, необходимо, чтобы к моменту поступления очередного фронта 2к-го счетного импульса на вход 4 сигнал сквозного переноса успел распространиться до m-го разряда по цепи из логических элементов 3=3, 3=4, …, 3=m, а это возможно лишь если m будет выбираться из условия

(2k-1)⋅Тмин≥(m-2)tзи,

где к - число разрядов счетчика 5;

Тмин - минимальный период следования синхроимпульсов на входе 4, определяемый быстродействием Т-триггера разряда;

m - количество счетных разрядов;

tзи - задержка логического элемента И.

Из приведенного выше условия получаем, что число разрядов m, охваченных сквозным переносом, определяется из выражения

m≤(2k-1)⋅Тмин/tзи+2.

Так, например, если Тмин=5 tзи, то при к=1 получаем m≤7, а N≤8, при к=2 получаем m≤17, а N≤19, при к=3 получаем m≤37, а N≤40, а при к=4 получаем m≤77, а N≤81 и т.д., т.е. при к=1 можно реализовать счетчик с предельным быстродействием максимум на 8 разрядов, а при к=4 можно реализовать счетчик с предельным быстродействием максимум на 81 разряд.

По фронту очередного 2к-го счетного импульса счетчик устанавливается в исходное состояние лог.0 на всех его выходах. На фиг. 3 и 4 показаны варианты реализации Т-триггера разряда на основе библиотечных элементов ПЛИС семейства Spartan D-триггера с элементом исключающего ИЛИ и JK-триггера.

Таким образом, предлагаемый счетчик, по сравнению с прототипом, позволяет уменьшить число двухвходовых логических элементов И на величину (N2-7 N)/2+6, а число связей - на величину N2-7 N+12 и тем самым значительно упростить счетчик при сохранении его максимального быстродействия. Кроме того, за счет простоты и регулярности, появилась возможность реализации многоразрядных счетчиков с предельным быстродействием.

Для реализации заявляемого устройства были использованы известные ПЛИС Xilinx семейства Spartan, выпускаемые зарубежной промышленностью.

ФУШЦИОНАЛЬНАЯ СХЕМА

Фиг. 1 - функциональная схема счетчика, где обозначены:

1=1 - 1=m - разряды счетчика;

2=2 - 2=m - первые двухвходовые логические элементы И разрядов, начиная со второго;

3=2 - 3=m - вторые двухвходовые логические элементы И разрядов, начиная со третьего;

4 - синхровход счетчика;

5 - к-разрядный счетчик с параллельным переносом;

р - выход переноса к-разрядного счетчика 5.

Фиг. 2 - временная диаграмма, поясняющая работу счетчика.

Фиг. 3 - вариант реализации Т-триггера разряда на основе библиотечных элементов ПЛИС семейства Spartan: D-триггера с элементом исключающего ИЛИ.

Фиг. 4 - вариант реализации Т-триггера разряда на основе JK-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| СЧЕТЧИК С СОХРАНЕНИЕМ КОЛИЧЕСТВА ЕДИНИЦ | 2020 |

|

RU2761135C1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| АСИНХРОННЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 2009 |

|

RU2452084C2 |

| Сдвигающее устройство | 1989 |

|

SU1686480A1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

Изобретение относится к цифровой технике и дискретной автоматике и может быть использовано для быстрого пересчета импульсов в двоичном коде. Технический результат - упрощение устройства. Для достижения результата введен k-разрядный счетчик с параллельным переносом, С-вход которого соединен с синхровходом счетчика, а выход переноса – с Т-входом триггера первого разряда и со вторым входом первого логического элемента И каждого из последующих m разрядов, причем m выбирается из условия m≤(2k-1)/Тмин/tзи+2, где k - число разрядов k-разрядного счетчика с параллельным переносом, Тмин - минимальный период следования синхроимпульсов на синхровходе счетчика, tзи - задержка логического элемента И, а в каждом из m-1 разрядов, начиная с третьего разряда, выходы триггера и второго логического элемента И соединены соответственно с первым и вторым входами второго логического элемента И следующего разряда. Простота и регулярность межразрядных связей позволяют строить многоразрядные счетчики с предельным быстродействием. 4 ил.

Счетчик, содержащий в каждом из m разрядов триггер, во втором разряде - логический элемент И, а в каждом из последующих разрядов - два логических элемента И, синхровход счетчика соединен с С-входами всех триггеров, причем выход триггера первого разряда соединен с первым входом логического элемента И второго разряда и с первым входом второго логического элемента И третьего разряда, выход второго логического элемента И каждого из m разрядов, начиная с третьего, соединен с первым входом первого логического элемента И этого же разряда, выход триггера второго разряда соединен со вторым входом второго логического элемента И третьего разряда, а выход первого логического элемента И каждого из m разрядов, начиная со второго, соединен с Т-входом триггера этого же разряда, отличающийся тем, что в него введен k-разрядный счетчик с параллельным переносом, С-вход которого соединен с синхровходом счетчика, а выход переноса – c Т-входом триггера первого разряда и со вторым входом первого логического элемента И каждого из последующих m разрядов, причем m выбирается из условия m≤(2k-1)/Тмин/tзи+2, где k - число разрядов k-разрядного счетчика с параллельным переносом, Тмин - минимальный период следования синхроимпульсов на синхровходе счетчика, tзи - задержка логического элемента И, а в каждом из m-1 разрядов, начиная с третьего разряда, выходы триггера и второго логического элемента И соединены соответственно с первым и вторым входами второго логического элемента И следующего разряда.

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ УПРАВЛЯЮЩИХ СИГНАЛОВ С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ | 2011 |

|

RU2475954C2 |

| Счетчик | 1976 |

|

SU657617A1 |

| US 4167789 A1, 11.09.1979 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2019-08-26—Публикация

2017-09-01—Подача