;

XI

XI

-N СЛ XI

Изобретение откосится к вычислительной технике, в частности к устройствам уп- равления памятью, и может быть использовано при построении запоминающих устройств.

Известно устройство управления памятью, которое содержит три регистра, причем один из них - сдвиговый, три счетчика, блок памяти, элементы И и ИЛИ, четыре триггера, мультиплексор и формирователь импульсов, Триггеры задают режим работы устройства, два счетчика через мультиплексор осуществляют адресацию блока памяти, а выход признака переполнения третьего счетчика является выходом признака ошибки устройства.

Наличие в устройстве нескольких одновременно переключающихся счетчиков и регистров снижает его помехозащищенность.

Наиболее близким к предлагаемому является устройство, которое содержит группу элементов И, два дешифратора, три блока памяти адресов, счетчик стека, элементы И-НЕ и ИЛИ. В первом блоке памяти фиксируются нормализованные в порядке их возрастания физические адреса включенных блоков памяти, во втором -устанавливается соответствие между физическими и логическими адресами, в третьем - фиксируется занятость блоков внешними обращениями. Первой из заявок с определенным адресом предоставляется первый из включенных и незанятых заявками с иным адресом блоков. По сигналу заема переноса стека индицируется занятость заявками всех включенных блоков.

Быстродействие устройства ограничивается необходимостью производить последовательноевыявлениеипереадресацию всех включенных занятых блоков памяти при каждом изменении их конфигурации. Кроме этого, быстродействие устройства снижается из-за его двухтактного управления.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для выборки блоков памяти, содержащее группу элементов И, блок памяти переадресации и дешифратор, причем К-й выход дешифратора подключен к К-му выходу управления выборкой памяти устройства (К 1, ... М, где М - количество выбираемых блоков памяти), вход логического адреса устройства подключен к адресному входу блока памяти, выход которого подключен к входу дешифратора, входы разрешения и записи блока памяти подключены соответственно к входу режима задания конфигурации и синхровходу устройства, К-й вход признака занятости блоков памяти устройства подключен к первому входу К-го элемента И, введены приоритетный шифратор, группа элементов эквивалентности и регистр, причем К-й выход дешифратора подключен к первому входу К-го элемента эквивалентности, выход которого подключен к входу К-го разряда регистра, выход которого подключен к второму входу

0 К-го элемента И и второму входу К-го элемента эквивалентности, выход К-го разряда элемента И подключен к входу К-го разряда шифратора, первый выход которого подключен к информационному входу блока па5 мяти, а второй - к выходу индикации занятости всех блоков памяти устройства, входы начальной установки, задания режима обмена с памятью и синхровход устройства подключены соответственно к входам

0 начальной установки, разрешения записи и синхровходу регистра.

Новая совокупность известных элементов позволяет в процессе загрузки блоков памяти, оперативно изменяя их конфигура5 цию и обеспечивая одноконтактное управление, исключить операцию опроса задействованных блоков после каждой из реконфигурации и ускорить возбуждение адресуемых блоков, ускорив адресацию как

0 минимум вдвое.

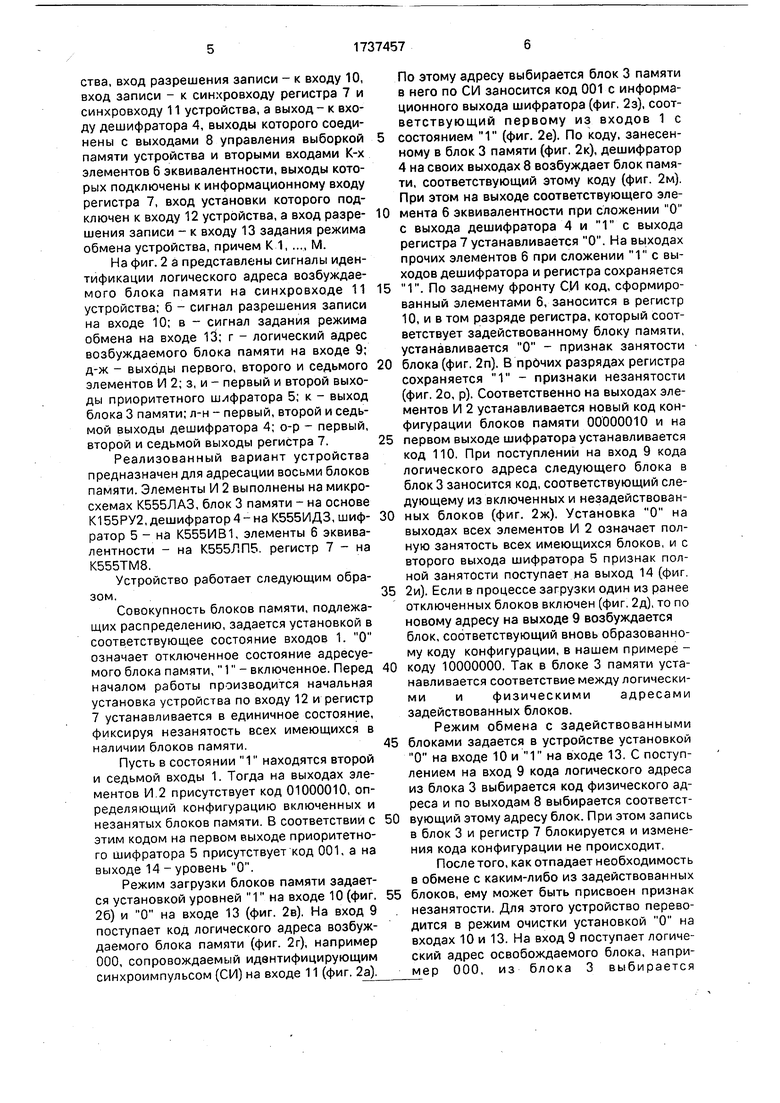

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 - временные диаграммы его работы.

Устройство содержит группу из М вхо5 дов 1 признаков занятости блоков памяти устройства, группу из М элементов И 2, блок 3 памяти переадресации, дешифратор 4, приоритетный шифратор 5, группу из М элементов 6 эквивалентности, регистр 7, выхо0 ды 8 управления выборкой памяти устройства, вход 9 логического адреса устройства, вход 10 разрешения записи устройства, синхровход 11 устройства, вход 12 начальной установки устройства, вход 13 за5 дания режима обмена устройства и выход 14 устройства для индицирования полной занятости блока памяти.

К-е входы 1 соединены с первыми входами К-х элементов И 2, вторые входы кото0 рых подключены к соответствующим выходам регистра 7 и первым входам К-х элементов 6 эквивалентности, а выходы соединены с соответствующими входами приоритетного шифратора 5, второй выход

5 которого подключен к выходу 14 устройства для индицирования полной занятости блоков, а первый выход соединен с информационным входом блока 3 памяти, адресный вход которого подключен к входу 9 устройства, вход разрешения записи - к входу 10, вход записи - к синхровходу регистра 7 и синхровходу 11 устройства, а выход- к входу дешифратора 4, выходы которого соединены с выходами 8 управления выборкой памяти устройства и вторыми входами К-х элементов 6 эквивалентности, выходы которых подключены к информационному входу регистра 7, вход установки которого подключен к входу 12 устройства, а вход разрешения записи - к входу 13 задания режима обмена устройства, причем К 1, ..., М.

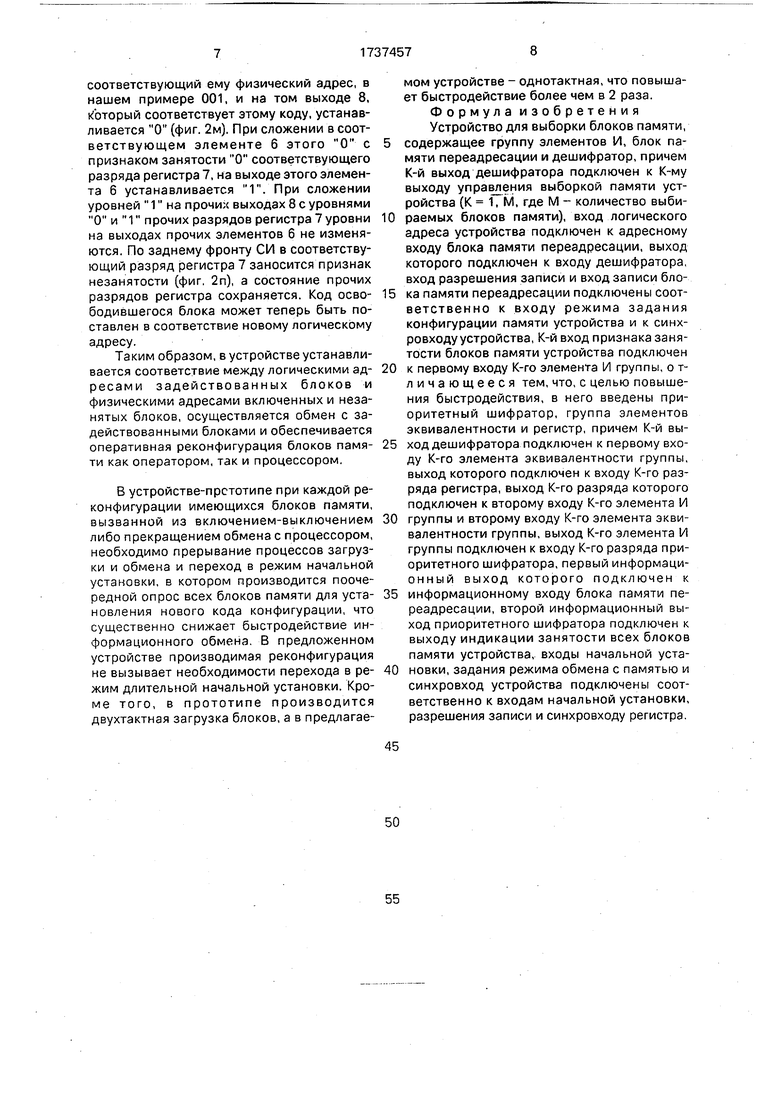

На фиг. 2 а представлены сигналы идентификации логического адреса возбуждаемого блока памяти на синхровходе 11 устройства; б - сигнал разрешения записи на входе 10; в - сигнал задания режима обмена на входе 13; г - логический адрес возбуждаемого блока памяти на входе 9; д-ж - выходы первого, второго и седьмого элементов И 2; з, и - первый и второй выходы приоритетного шифратора 5; к - выход блока 3 памяти; л-н - первый, второй и седьмой выходы дешифратора 4; о-р - первый, второй и седьмой выходы регистра 7.

Реализованный вариант устройства предназначен для адресации восьми блоков памяти. Элементы И 2 выполнены на микросхемах К555ЛАЗ, блок 3 памяти - на основе К155РУ2, дешифратор 4 - на К555ИДЗ, шифратор 5 - на К555ИВ1, элементы 6 эквивалентности - на К555ЛП5. регистр 7 - на К555ТМ8.

Устройство работает следующим образом.

Совокупность блоков памяти, подлежащих распределению, задается установкой в соответствующее состояние входов 1. О означает отключенное состояние адресуемого блока памяти, 1 - включенное. Перед началом работы производится начальная установка устройства по входу 12 и регистр 7 устанавливается в единичное состояние, фиксируя незанятость всех имеющихся в наличии блоков памяти.

Пусть в состоянии 1 находятся второй и седьмой входы 1. Тогда на выходах элементов И 2 присутствует код 01000010, определяющий конфигурацию включенных и незанятых блоков памяти. В соответствии с этим кодом на первом выходе приоритетного шифратора 5 присутствует код 001, а на выходе 14 - уровень О.

Режим загрузки блоков памяти задается установкой уровней 1 на входе 10 (фиг. 26) и О на входе 13 (фиг. 2в). На вход 9 поступает код логического адреса возбуждаемого блока памяти (фиг. 2г), например 000, сопровождаемый идентифицирующим синхроимпульсом (СИ) на входе 11 (фиг. 2а).

По этому адресу выбирается блок 3 памяти в него по СИ заносится код 001 с информационного выхода шифратора (фиг. 2з), соответствующий первому из входов 1 с

состоянием 1 (фиг. 2е). По коду, занесенному в блок 3 памяти (фиг. 2к), дешифратор 4 на своих выходах 8 возбуждает блок памяти, соответствующий этому коду (фиг. 2м). При этом на выходе соответствующего эле0 мента 6 эквивалентности при сложении О с выхода дешифратора 4 и 1 с выхода регистра 7 устанавливается О. На выходах прочих элементов 6 при сложении 1 с выходов дешифратора и регистра сохраняется

5 1. По заднему фронту СИ код, сформированный элементами 6, заносится в регистр 10, и в том разряде регистра, который соответствует задействованному блоку памяти, устанавливается О - признак занятости

0 блока (фиг. 2п). В прочих разрядах регистра сохраняется 1 - признаки незанятости (фиг, 2о, р). Соответственно на выходах элементов И 2 устанавливается новый код конфигурации блоков памяти 00000010 и на

5 первом выходе шифратора устанавливается код 110. При поступлении на вход 9 кода логического адреса следующего блока в блок 3 заносится код, соответствующий следующему из включенных и незадействован0 ных блоков (фиг. 2ж), Установка О на выходах всех элементов И 2 означает полную занятость всех имеющихся блоков, и с второго выхода шифратора 5 признак полной занятости поступает на выход 14 (фиг.

5 2и). Если в процессе загрузки один из ранее отключенных блоков включен (фиг. 2д), то по новому адресу на выходе 9 возбуждается блок, соответствующий вновь образованному коду конфигурации, в нашем примере 0 коду 10000000. Так в блоке 3 памяти устанавливается соответствие между логически- ми и физическими адресами задействованных блоков.

Режим обмена с задействованными

5 блоками задается в устройстве установкой О на входе 10 и 1 на входе 13. С поступлением на вход 9 кода логического адреса из блока 3 выбирается код физического адреса и по выходам 8 выбирается соответст0 вующий этому адресу блок. При этом запись в блок 3 и регистр 7 блокируется и изменения кода конфигурации не происходит.

После того, как отпадает необходимость в обмене с каким-либо из задействованных

5 блоков, ему может быть присвоен признак незанятости, Для этого устройство переводится в режим очистки установкой О на входах 10 и 13. На вход 9 поступает логический адрес освобождаемого блока, например 000, из блока 3 выбирается

соответствующий ему физический адрес, в нашем примере 001, и на том выходе 8, Который соответствует этому коду, устанавливается О (фиг. 2м). При сложении в соответствующем элементе 6 этого О с признаком занятости О соответствующего разряда регистра 7, на выходе этого элемента 6 устанавливается 1. При сложении уровней 1 на прочих выходах 8 с уровнями О и 1 прочих разрядов регистра 7 уровни на выходах прочих элементов 6 не изменяются. По заднему фронту СИ в соответствующий разряд регистра 7 заносится признак незанятости (фиг, 2п), а состояние прочих разрядов регистра сохраняется. Код освободившегося блока может теперь быть поставлен в соответствие новому логическому адресу.

Таким образом, в устройстве устанавливается соответствие между логическими ад- ресами задействованных блоков и физическими адресами включенных и незанятых блоков, осуществляется обмен с задействованными блоками и обеспечивается оперативная реконфигурация блоков памяти как оператором, так и процессором.

В устройстве-прототипе при каждой реконфигурации имеющихся блоков памяти, вызванной из включением-выключением либо прекращением обмена с процессором, необходимо прерывание процессов загрузки и обмена и переход в режим начальной установки, в котором производится поочередной опрос всех блоков памяти для установления нового кода конфигурации, что существенно снижает быстродействие информационного обмена. В предложенном устройстве производимая реконфигурация не вызывает необходимости перехода в режим длительной начальной установки. Кроме того, в прототипе производится двухтактная загрузка блоков, а в предлагае0

5

0

5

0

5

0

мом устройстве - однотактная, что повышает быстродействие более чем в 2 раза. Формула изобретения Устройство для выборки блоков памяти, содержащее группу элементов И, блок памяти переадресации и дешифратор, причем К-й выход дешифратора подключен к К-му выходу управления выборкой памяти устройства (К 1, М, где М - количество выбираемых блоков памяти), вход логического адреса устройства подключен к адресному входу блока памяти переадресации, выход которого подключен к входу дешифратора, вход разрешения записи и вход записи блока памяти переадресации подключены соответственно к входу режима задания конфигурации памяти устройства и к синх- ровходу устройства, К-й вход признака занятости блоков памяти устройства подключен к первому входу К-го элемента И группы, о т- личающееся тем, что, с целью повышения быстродействия, в него введены приоритетный шифратор, группа элементов эквивалентности и регистр, причем К-й выход дешифратора подключен к первому входу К-го элемента эквивалентности группы, выход которого подключен к входу К-го разряда регистра, выход К-го разряда которого подключен к второму входу К-го элемента И группы и второму входу К-го элемента эквивалентности группы, выход К-го элемента И группы подключен к входу К-го разряда приоритетного шифратора, первый информаци- онный выход которого подключен к информационному входу блока памяти переадресации, второй информационный выход приоритетного шифратора подключен к выходу индикации занятости всех блоков памяти устройства, входы начальной установки, задания режима обмена с памятью и синхровход устройства подключены соответственно к входам начальной установки, разрешения записи и синхровходу регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для поиска свободных зон памяти | 1990 |

|

SU1829046A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для динамического преобразования адреса | 1985 |

|

SU1265771A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для поиска свободных зон памяти | 1987 |

|

SU1481851A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для адресации памяти | 1990 |

|

SU1805472A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления памятью, и может быть использовано при построении запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Устройство содержит группы входов 1 признаков занятости блоков памяти устройства и элементов И 2, блок 3 памяти переадресации, дешифратор 4, приоритетный шифратор 5, группу элементов 6 эквивалентности, регистр 7, выходы 8 управления выборкой памяти устройства, входы 9 логического адреса и входы 10 разрешения записи устройства, синхровход 11, входы 12 начальной установки, вход 13 задания режима обмена и выход 14 для индицирования полной занятости блока памяти. Поставленная цель достигается введением новых элементов и связей. В устройстве устанавливается соответствие между логическими адресами задействованных блоков и физическими адресами включенных и незанятых блоков памяти, осуществляется обмен с задействованными блоками и обеспечивается оперативная реконфигурация блоков памяти как оператором,так и процессором.2 ил.

Фаг. 2

| Устройство управления памятью | 1986 |

|

SU1401465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации блоков памяти | 1987 |

|

SU1481777A1 |

Авторы

Даты

1992-05-30—Публикация

1990-03-19—Подача