Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1986 |

|

SU1356260A1 |

| Устройство для формирования бинарных телевизионных сигналов | 1991 |

|

SU1818707A1 |

| Видеоконтроллер | 1990 |

|

SU1816326A3 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ТОЧЕЧНЫХ ОБЪЕКТОВ | 1989 |

|

SU1623537A1 |

| Устройство для распознавания образов | 1990 |

|

SU1725240A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

Изобретение относится к связи и может быть использовано в телевидении, фотографии, видеотелефонии для передачи изобра- жений по цифровым линиям связи со сжатием. Цель изобретения - уменьшение искажений изображения путем согласования параметров кодирования сигналов изображения со зрительным восприятием помех на разных уровнях яркости декодированного изображения. Устройство для кодирования сигналов изображения содержит дешифратор 1, аналого-цифровой преобра

vj

а ы

00

ю

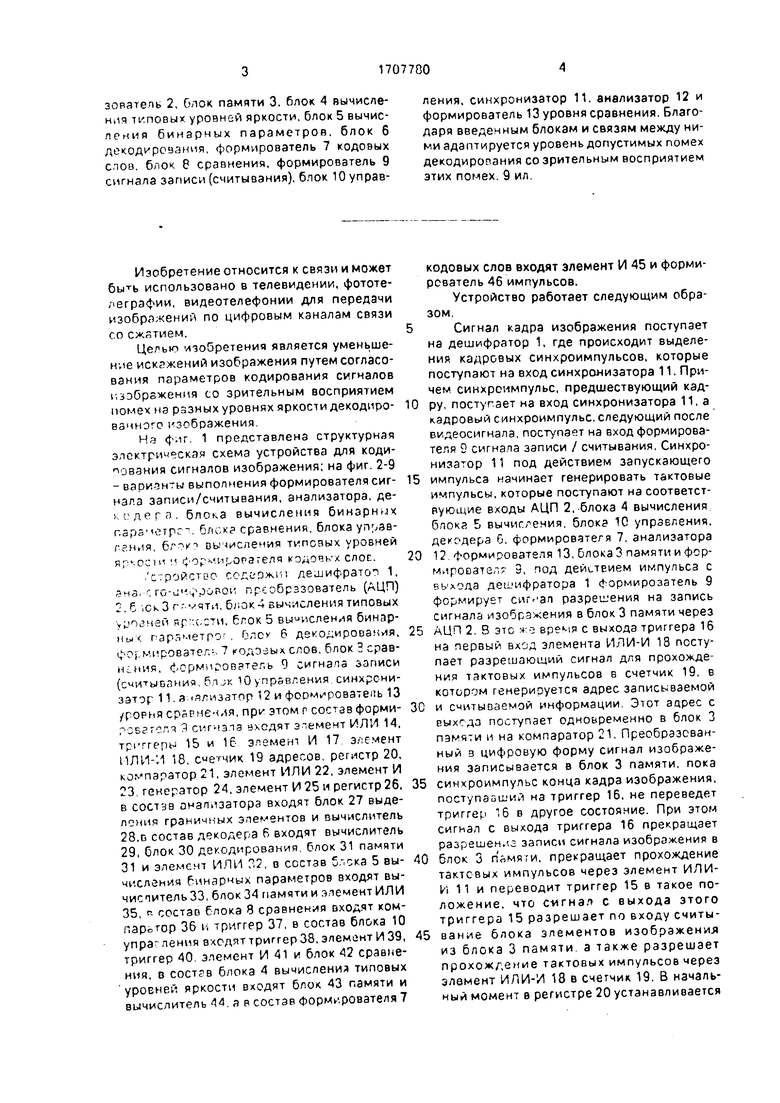

Фиг.1

зователь 2, блок памяти 3. блок 4 вычисления типовых, уровней яркости, блок 5 вычисления бинарных параметров, блок 6 декодирования, формирователь 7 кодовых слов, блок 8 сравнения, формирователь 9 сигнала записи (считывания), блок 10 управИзобретение относится к связи и может быть использовано в телевидении, фототелеграфии, видеотелефонии для передачи изображений по цифровым каналам связи со сжатием.

Целью изобретения является уменьшение искажений изображения путем согласования параметров кодирования сигналов г.зэбргженмя со зрительным восприятием помех на рззных уровнях яркости декодированного изображения.

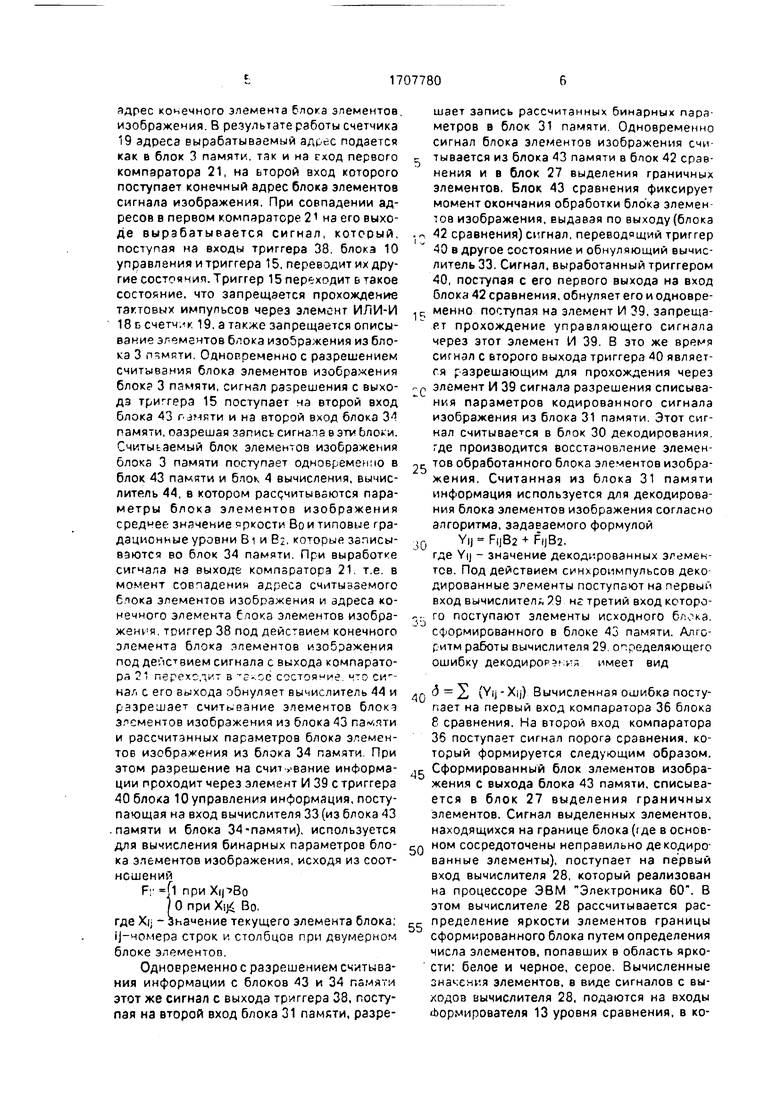

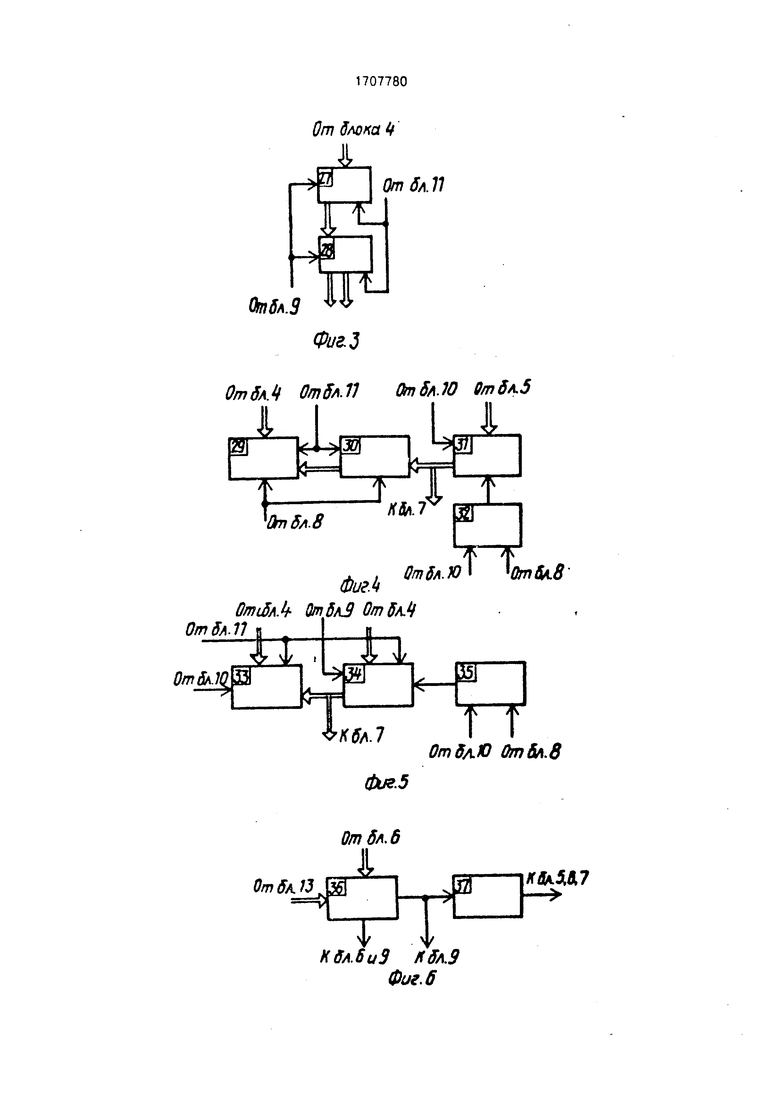

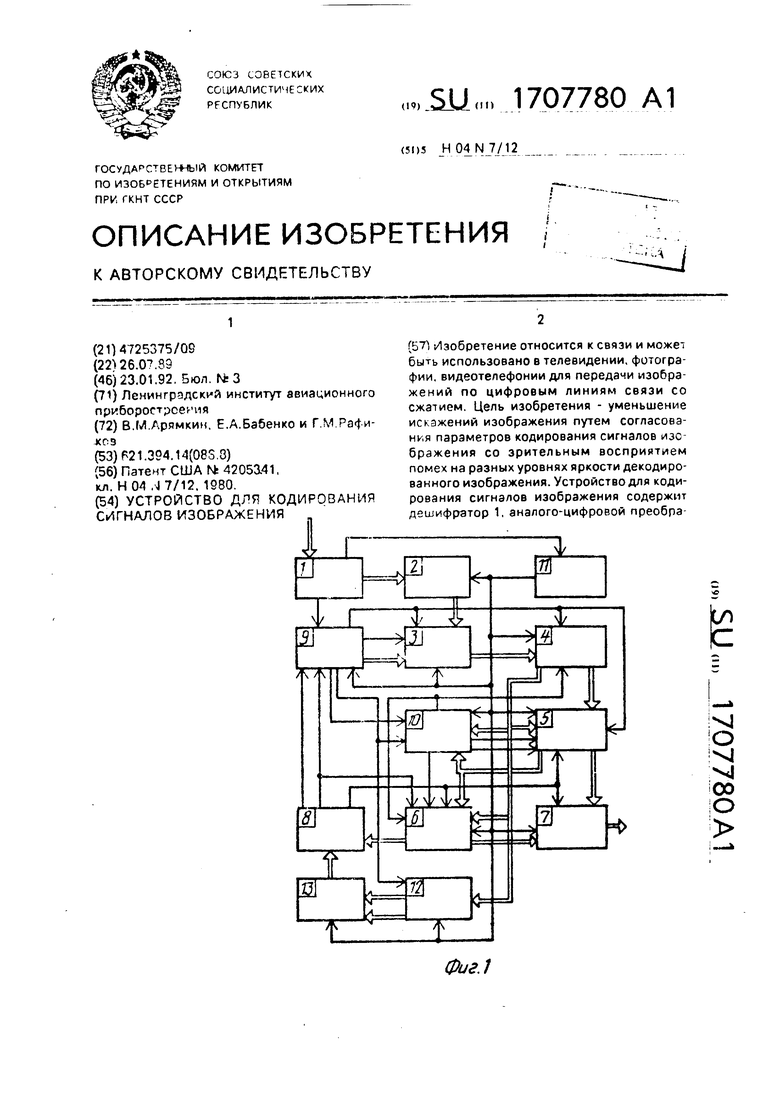

На фиг. 1 представлена структурная электрическая схема устройства для коди- пования сигналов изображения; на фиг. 2-9 - варианты выполнения формирователя сигнала записи/считывания, анализатора, де- кс ле Г а. блока вычисления бинэрнмх параметре, блек сравнений, блока управления, вычисления типовых уровней яр -ости фор.иропагеля кодовых СЛОЕ.

/стройстоо содержи г де ифраточ 1, ана,с го- и ророй преобразователь (АЦП) 1, б.-.ck 3 г /чти. блок 4 вычисления типовых ууозней яркости, блок 5 вычисления бинарных гараметрог. блох б декодирования, фО|.мировэтегл. 7 кодэзых слов, блок 3 сравнения, формирователь 9 сигнала записи (считывания,блJK 10 управления,синхронизатор 11. анализатор 2 и формирователь 13 /рорнясрарне ия, при этом г состав формирователя Я сигнала аходят элемент ИЛИ 14, триггеры 15 и 16. элемент И 17, элемент ИЛИ- И 18, сметчик 19 адресов, регистр 20, компаратор 21, элемент ИЛИ 22, элемент И 23, генератор 24, элемент И 25 и регистр 26, в состав анализатора входят блок 27 выделения граничных элементов и вычислитель 28,о состав декодера 6 входят вычислитель 29, блок 30 декодирования, блок 31 памяти 31 и элемент ИЛИ 32, в состав блока 5 вычисления бинарных параметров входят вы- чиспительЗЗ, блок 34 памяти и элемент ИЛИ 35, R состав блока 8 сравнения входят ком- парьтор 36 и триггер 37, в сослав блока 10 упраг ления входят триггер 38, элемент И 39, триггер 40. элемент И 41 и блок 42 сравнения, в состав блока 4 вычисления типовых уровней яркости входят блок 43 памяти и вычислитель 44. а в состав формирователя

ления, синхронизатор 11. анализатор 12 и формирователь 13 уровня сравнения. Благодаря введенным блокам и связям между ними адаптируется уровень допустимых помех декодирования со зрительным восприятием этих помех. 9 ил.

кодовых слов входят элемент И 45 и формирователь 46 импульсов.

Устройство работает следующим образом.

Сигнал кадра изображения поступает на дешифратор 1, где происходит выделения кадровых синхроимпульсов, которые поступают на вход синхронизатора 11. Причем синхроимпульс, предшествующий кадру, поступает на вход синхронизатора 11, а кадровый синхроимпульс, следующий после видеосигнала, поступает на вход формирователя 9 сигнала записи / считывания, Синхронизатор 11 под действием запускающего

импульса начинает генерировать тактовые импульсы, которые поступают на соответствующие входы АЦП 2,-блока 4 вычисления; блока Б вычисления, блока 10 управления, декодера б, формирователя 7, анализатора

12, формирователя 13, блока 3 памяти и фср- мировате/iz 9, под действием импульса с выхода дешифратора 1 Формирователь 9 формирует сигнал разрешения на запись сигнала изображения в блок 3 памяти через

АЦП 2. 8 это же время с выхода триггера 16 на первый вход элемента ИЛИ-И 18 поступает разрешающий сигнал для прохождения тактовых импульсов в счетчик 19. в котором генерируется адрес записываемой

и считываемой информации. Этот адрес с выхода поступает одновременно в блок 3 памяти и на компаратор 21. Преобразованный з цифровую форму сигнал изображения записывается в блок 3 памяти, пока

синхроимпульс конца кадра изображения, поступавший на триггер 16, не переведет триггер 1.6 в другое состояние. При этом сигнал с выхода триггера 16 прекращает разрешение записи сигнала изображения в

блок 3 п ймяги, прекращает прохождение тактовых импульсов через элемент ИЛИ- И 11 и переводит триггер 15 в такое положение, что сигнал с выхода этого триггера 15 разрешает по входу считывание блока элементов изображения из блока 3 памяти, а также разрешает прохождение тактовых импульсов через элемент ИЛИ-И 18 в счетчик. 19. В начальный момент в регистре 20 устанавливается

адрес конечного элемента блока элементов, изображения. В результате работы счетчика 19 адреса вырабатываемый адрес подается как в блок 3 памяти, так и на сход первого компаратора 21, на ьторой вход которого поступает конечный адрес блока элементов сигнала изображения. При совпадении адресов в первом компараторе 21 на его выходе вырабатывается сигнал, который, поступая на входы триггера 38. блока 10 управления и триггера 15, переводит их другие состояния. Триггер 15 переходит ъ такое состояние, что запрещается прохождение тактовых импульсов через элемент ИЛИ-И 18 Б счетчик. 19, а также запрещается списывание элементов блока изображения из блока 3 памяти. Одновременное разрешением считывания блока элементов изображения блок 3 памяти, сигнал разрешения с выхода триггера 15 поступает на второй вход блока 43 памяти и на второй вход блока 34 памяти, оазрешая запись сигнала в эти Ьлоки. Считываемый блок элементов изображения блока 3 памяти поступает одновременно в блок 43 памяти и блок 4 вычисления, вычислитель 44, в котором рассчитываются параметры блока элементов изображения среднее значение яркости Во и типовые градационные уровни В1 и В2, которые записываются во блок 34 памяти. При выработке сигнала на выходе компаратора 21. т.е. в момент совпадения адреса считываемого блока элементов изображения и адреса конечного элемента блока элементов изображения, триггер 38 под действием конечного элемента блока элементов изображения под действием сигнала с выхода компаратора 21 переходит в г-.оё состояние, что нал с его выхода обнуляет вычислитель 44 и разрешает считывание элементов блокэ элементов изображения из блока 43 па«.лти и рассчитанных параметров блока элементов изображения из блока 34 памяти, При этом разрешение на считывание информации проходит через элемент И 39 с триггера 40 блока 10 управления информация, поступающая на вход вычислителя 33 (из блока 43 .памяти и блока 34-памяти), используется для вычисления бинарных параметров блока элементов изображения, исходя из соотношений

-fl при XipBo

OnpnXiji Во,

где Xij -Значение текущего элемента блока; ij-номера строк и столбцов при двумерном блоке элементов.

Одновременно с разрешением считывания информации с блоков 43 и 34 памяти этот же сигнал с выхода триггера 38, поступая на второй вход блока 31 памяти, разре5

5

0

шает запись рассчитанных бинарных параметров в блок 31 памяти. Одновременно сигнал блока элементов изображения считывается из блока 43 памяти в блок 42 сравнения и в блок 27 выделения граничных элементов. Блок 43 сравнения фиксирует момент окончания обработки блока элементов изображения, выдавая по выходу (блока 42 сравнения) сигнал, переводящий триггер 40 в другое состояние и обнуляющий вычислитель 33. Сигнал, выработанный триггером 40, поступая с его первого выхода на вход блока 42 сравнения, обнуляет его и одновременно поступая на элемент И 39, запрещает прохождение управляющего сигнала через этот элемент И 39. В это же время сигнал с второго выхода триггера 40 является разрешающим для прохождения через элемент И 39 сигнала разрешения списывания параметров кодированного сигнала изображения из блока 31 памяти. Этот сигнал считывается в блок 30 декодирования, где производится восстановление элементов обработанного блока элементов изображения. Считанная из блока 31 памяти информация используется для декодирования блока элементов изображения согласно алгоритма,задаваемого формулой

Yij FijB2-t- RjB2,

где YIJ - значение декодированных элементов. Под действием синхроимпульсов декодированные элементы поступают на первый вход вычислителя, 29 нг третий вход которого поступают элементы исходного блока. сформированного в блоке 43 памяти. Алгоритм работы вычислителя 29, определяющего ошибку декодирор ;ия имеет вид

O

( (Yij Xij). Вычисленная ошибка поступает на первый вход компаратора 36 блока 8 сравнения. На второй вход компаратора 35 поступает сигнал порога сравнения, который формируется следующим образом. с Сформированный блок элементов изображения с выхода блока 43 памяти, списывается в блок 27 выделения граничных элементов. Сигнал выделенных элементов, находящихся на границе блока (где в основном сосредоточены неправильно декодированные элементы), поступает на первый вход вычислителя 28, который реализован на процессоре ЭВМ Электроника 60. В этом вычислителе 28 рассчитывается распределение яркости элементов границы сформированного блока путем определения числа элементов, попавших в область яркости: белое и черное, серое. Вычисленные значения элементов, в виде сигналов с выходов вычислителя 28, подаются на входы Формирователя 13 уровня сравнения, в ко0

0

5

тором формируется сигнал, пропорциональный отношению числа элементов, выделенных на границе, принадлежащих области серого относительно области белое и черное. При меньшем числе элементов, принадлежащих области серое в качестве уроэня сравнения берется отношение значений величин, попавших в область иеоое и область белое и чгрное. В про- тгоном случае беротся величина обоатная дополнительному коду. Сформированный - Тппгированний уровень (порог) сравнения пода,.- второй вход компаратора 36, на пергой вход к,, .,: гр| подается величина ошиоки декодирования сформированного в С оке 43 памяти блока элементов изображения. Если вегичина ошибки декодирования не превышает порога сравнения, учитывающего зрительное восприятие искаженных элементов , тогда с первого выхода компаратор 36 поступает сигнал на сход триггера 37, который вырабатывает сигнал, разрешающий прохождение информационного сигнала через блок элементов И 45. Этот же сигнал с первого выхода компаратора 36 разрешает списывание рассчитанных параметров из блоков 34 и 31 памяти. ти поэмстрь1 кодирования через блок элемент о V Л6 1 средзются в формирователь, предстзьг. -.ющий coT.jfi регистр сдвига, из кс.соого год дсмстпитм тактирующих импульсов сФорА -лроЕ анныГ- ci-.it.эл поступает в KSHPI сгязи. Одновременно сигнал с первого о дг компаратора ЗЬ гюсг. оает на «о злен- --топ :А 1.3, на г-.;ерйгор 2- и H;J G..J элементов И 17. L- результате работы

СТ.,.. СЛОЮВ p33piAUt OTCf. СПИСЫ ЕЧИг НЭчзльн.-ro ад;;.са сле-ующ е б г ./.-.а эг,емс-н- тоа изобргг е - -иг блока 3 гачптл. Это производите Гтп5гсдгрг разрешающему сигналу, дейстсующему ли в:.олу блока эле- м:нт-: 5 И 17, разре и- юи;ему .if схождение предыдушого значения адреса из г б: 1стра 20 г, счетчик 19. Предыдущий конечный адрес блока элементов изображения становится начальным адресом нового блока элементов изображения. Из генератора 2-1 через бло элементов И 23 в регистр 20 зап.- сывзется конечный адрес нового блока элементов изображения. Этот же сигнал с первого выхода компаратора 36, поступающий, чегсэ элементу ИЛИ 22 и 14 переводит ipi -ер 15 в такое состояние, что рззреша- подача тактовых импульсов через эле- Mew 18 в счетчик 19 и разрешается списывание очередного блока элементов изображения из блока 3 памяти. Сигнал с сыхода элемента ИЛИ 22. поступая на входы триггеров 38 и 40, переводит их в исходное состояние, а сигнал, поступающий на

вход блока 27 выделения граничных элементов и вычислителя 28, обнуляет эти блоки и приводит их в исходное состояние, после чего работа устройства повторяется до тех

пор, пока не будут сформированы параметры кодирования последнего блока элементов. В случае же невыполнения условий сравнений в компараторе 36, сигнал с второго выхода компаратора 36 через элемент

ИЛИ 22, поступая на вход триггера 15. переводит его в тгкое состояние, что разрешается прохождение тактовых импульсов через элемент ИЛИ-И 18 в счетчик 19, а поступая на третий вход блока 3 памяти,

разрешает считывание из этого блока информации. Сигнал же, поступающий на блок элементов И 17, не разрешает считывание начального адреса в счетчик 19, который остается прежним для блока элементов изображения. Конечный адрес этого же блока элементов перестраивается в пределах, регулируемых регистром 26. При невыполнении условий сравнения на блок элементов И 25 поступает разрешающий сигнал и с реги-стра 26 скорректированный конечный адрес блока элементов изображения в регистр 20. Поэтому списывание блока начинается с прежнего адреса блока, а окончание формирования б/ока - по конечному скорректированному адресу, сформированному в пегистро 20. Регистр 26 осуществляет корректировку конечного адреса блока по псевдослучайному закону. Период псевдослучайности выбран очень большим путем

выбора соответствующего числа ячеек регистра 26 сдвига, что обеспечивает многократную пеоестройку конечного адреса .

Фор мула изобретения

Устройство ДЛР кодирования сигналов изображения, содержащее последовательно соединенные дешифратор, аналого-циф- ровой преобразователь (АЦП), блок памяти.

блок вычисления типовых уровней яркости, блок вычисления бинарных параметров, декодер и формирователь кодовых слое, а также блок сравнения, первый и второй выходы которого соединены соответственно с пероым и вторым управляющими входами формирователя сигнала записи/считывания, первый выход которого соединен с первым управляющим входом блока управления, второй выход формирователя сигнала записи/считывания соединен с входом считывания блока памяти и с входами записи блока вычисления типовых уровней яркости и блока вычисления бинарных параметров, второй выход которого соединен с соответствующим входом формирователя кодовых слов, третий выход блока сравнения соединен с управляющим входом формирователя кодовых слов и первыми входами считывания блока вычисления бинарных параметров и блока декодирования, другой выход которого соединен с первым входом блока сравнения, второй выход которого соединен с входом установки в исходное состояние блока декодирования, к третьему управляющему входу формирователя сигна- ла записи/считывания подключен выход кадрового синхроимпульса дешифратора, другой выход которого соединен с управляющим входом синхронизатора, выход которого соединен с тактовыми входами АЦП, блока вычисления типовых уровней яркости, блока памяти, блока вычисления бинарных параметров, блока декодирования, формирователя кодовых слов и формирователя сигнала записи/считывания, третий выход которого соединен с входом записи блока памяти, адресные выходы - с адресными сходами блока памяти, з четвертый выход формирователя сигнала записи считывания соединен с входом установки в ис- ходное состояние блока управления, первый и второй выходы которого соединеКблМК

ны с входом считывания и с входом обнуления блока вычисления бинарных параметров, третий выход блока управления подсоединен к входу считывания блока вычисления типовых уровней яркости и к входу записи блока декодирования, к второму входу считывания которого подключен соответствующий выход блока управления, второй выход блока вычисления типовых уровней яркости соединен с соответствующими входами блока вычисления бинарных параметров, блока управления и блока декодирования, отличающееся тем, что, с целью уменьшения искажений изображения путем согласования параметров кодирования сигналов изображения со зрительным восприятием помех на разных уровнях яркости между вторым выходом блока вычисления типовых уровней и вторым входом блока сравнения введены последовательно соединенные анализатор и формирователь уровня сравнения, при этом вход обнуления анализатора соединен с четвертым выходом формирователя сигнала записи/считывания, а к тактовым входам анализатора и формирователя уровня сравнения подключен выход синхронизатора.

Фиг. 2

От 0лока Ц

L

От &.П

I

hJ

Лпвл.9

U

Фиг J

/77 Отбл-П Отбл.Ю

LJL

Цшг

f

г

ДяЛ|.

, От6л.Ю 0mfa8

ОтДлЬ Отйлд От$л.Ц ОтблЛ в .п

й

JSL

I -

1кбА.7

т

гт

Отбл.Ю Отбл.8

Отбл.6

ОтблК Ф

КдлбиЗ Л$л9 Фиг. б

tJ

FjlT

JSL

т

гт

Отбл.Ю Отбл.8

фиг.5

/г Л ДА 7

KffA..П Фиг.7

Отбл.ЗОтдл-9

LA

Отдл.10

i-Ч,

Л 5л.5,Ь,Ю,ЦК6л.5 Фае. 8

Л,

OmffA.8 OmffA.Jl

Фиг.9

ОтблЗ КйА.Ьикбл.б

Отдл-9

±3

«г

i-Ч,

Выход устройства

| Патент США Ы 4205141, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1992-01-23—Публикация

1989-07-26—Подача