Изобретение относится к технической кибернетике и может быть использовано для решения задач диагностики и контроля, при обработке изображений, в системах переработки информации.

Цель изобретения - повышение быстродействия за счет сжатия обрабатываемой информации.

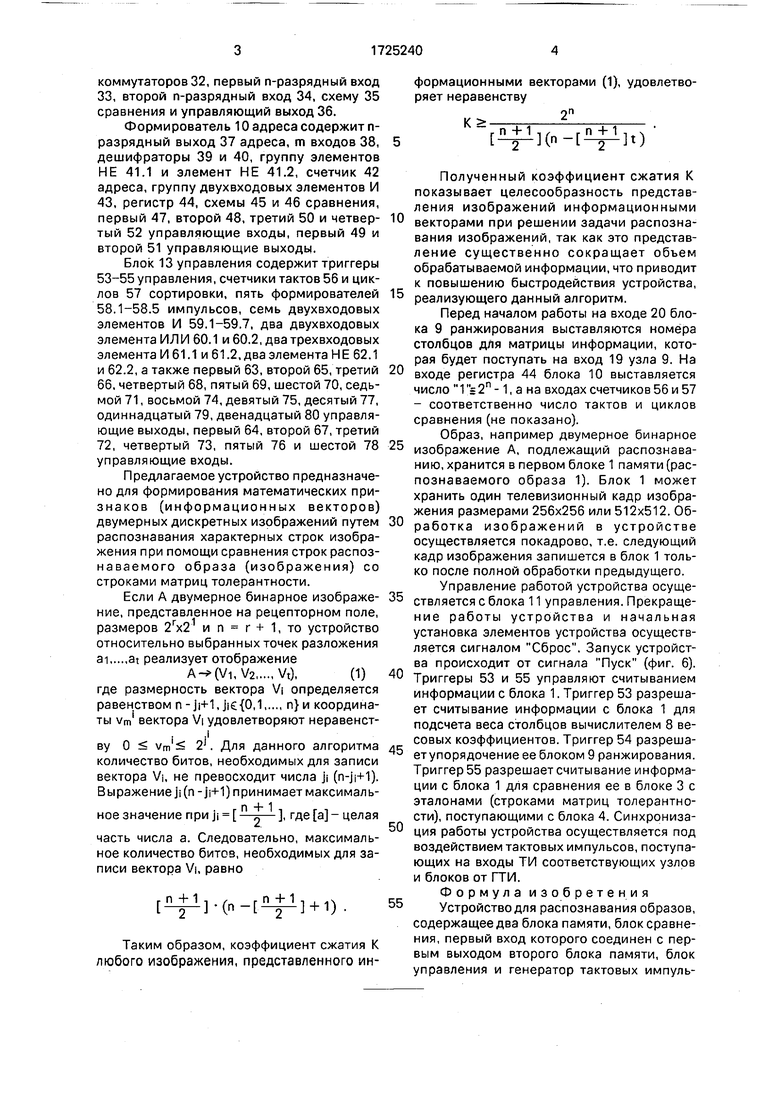

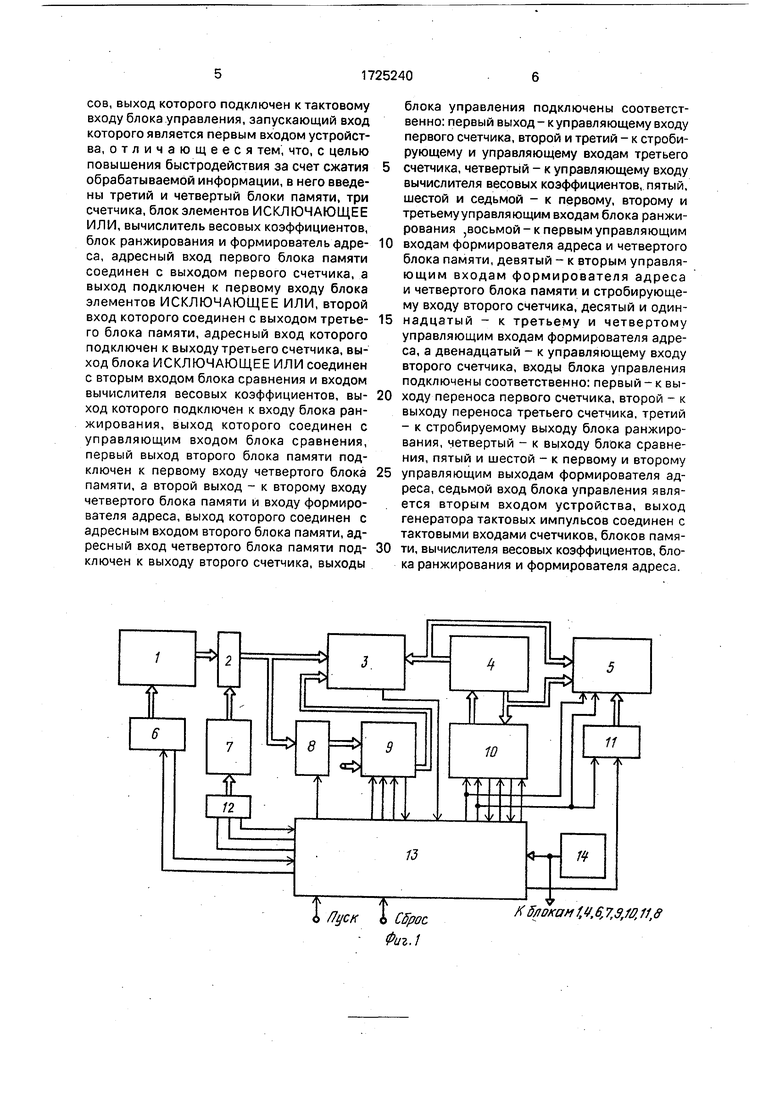

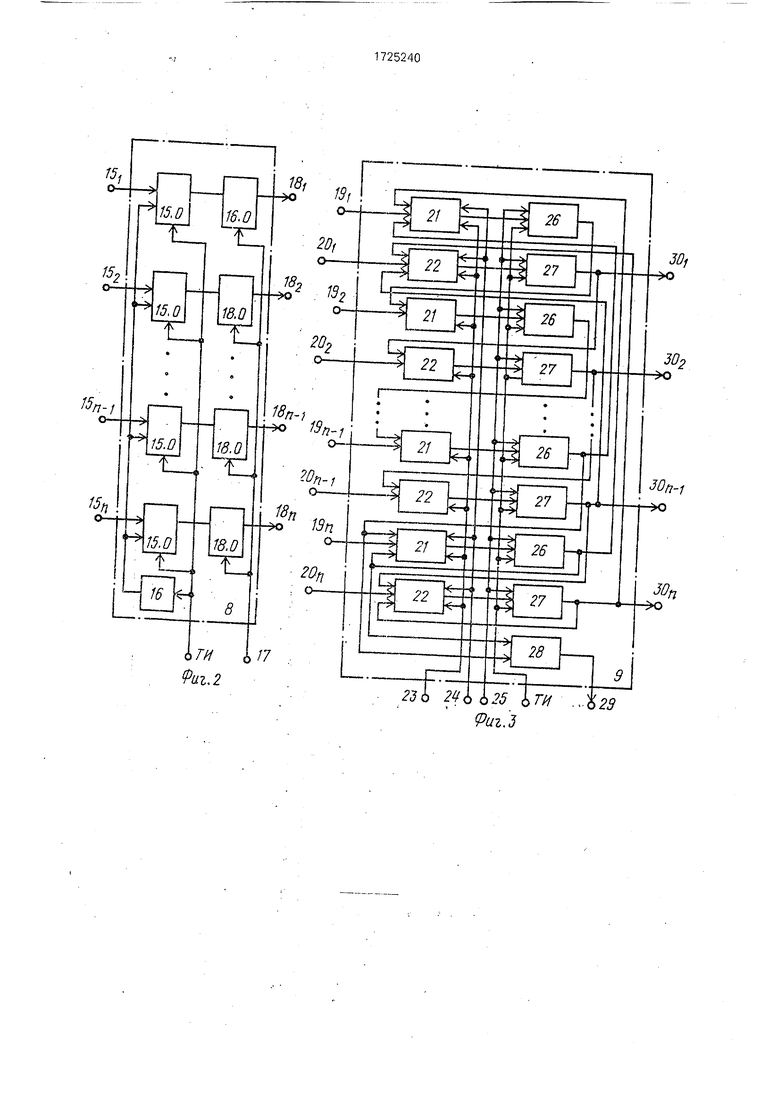

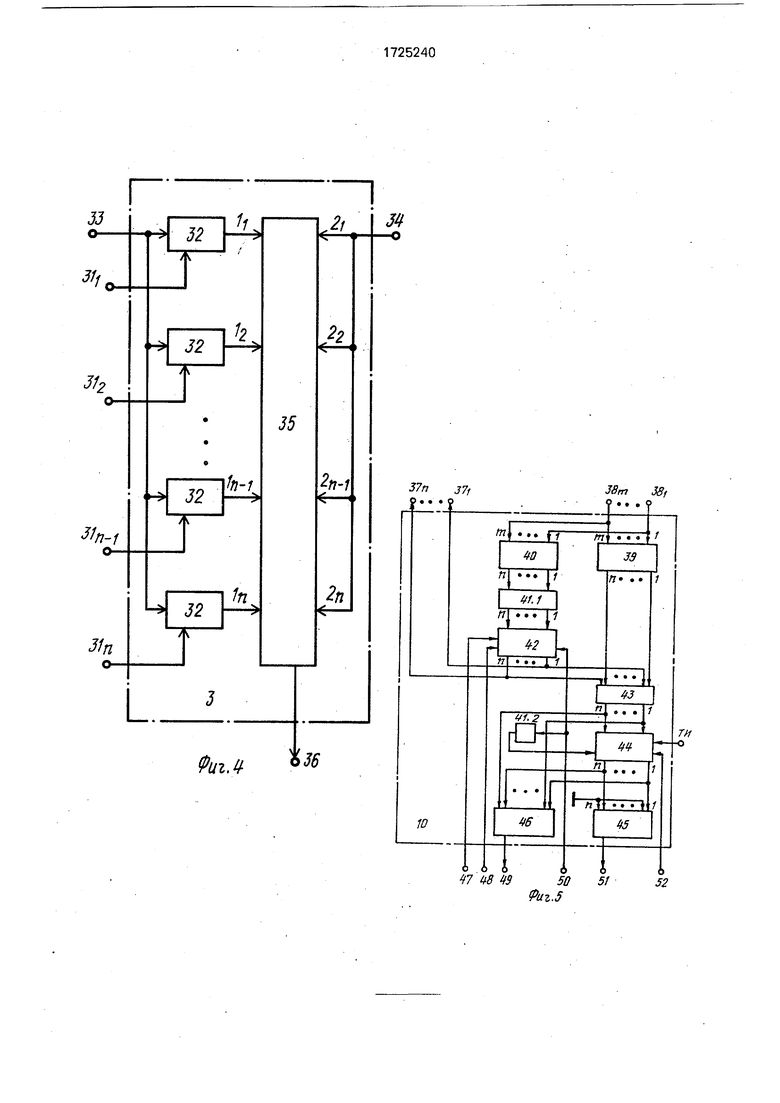

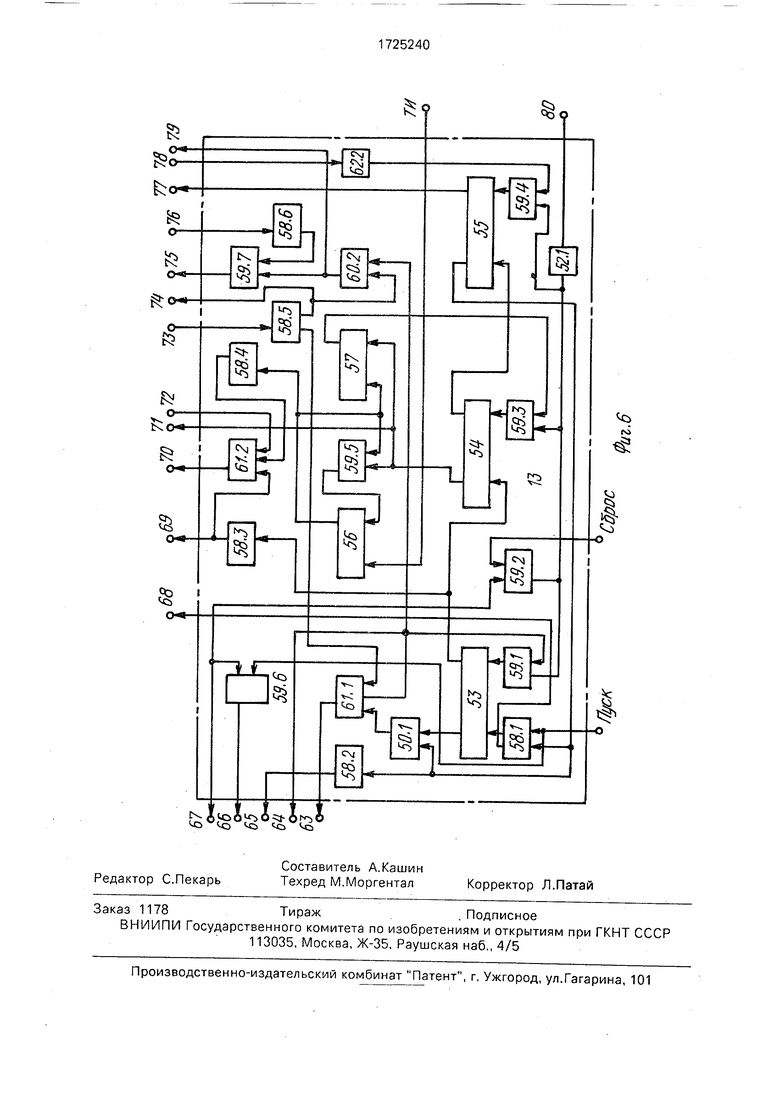

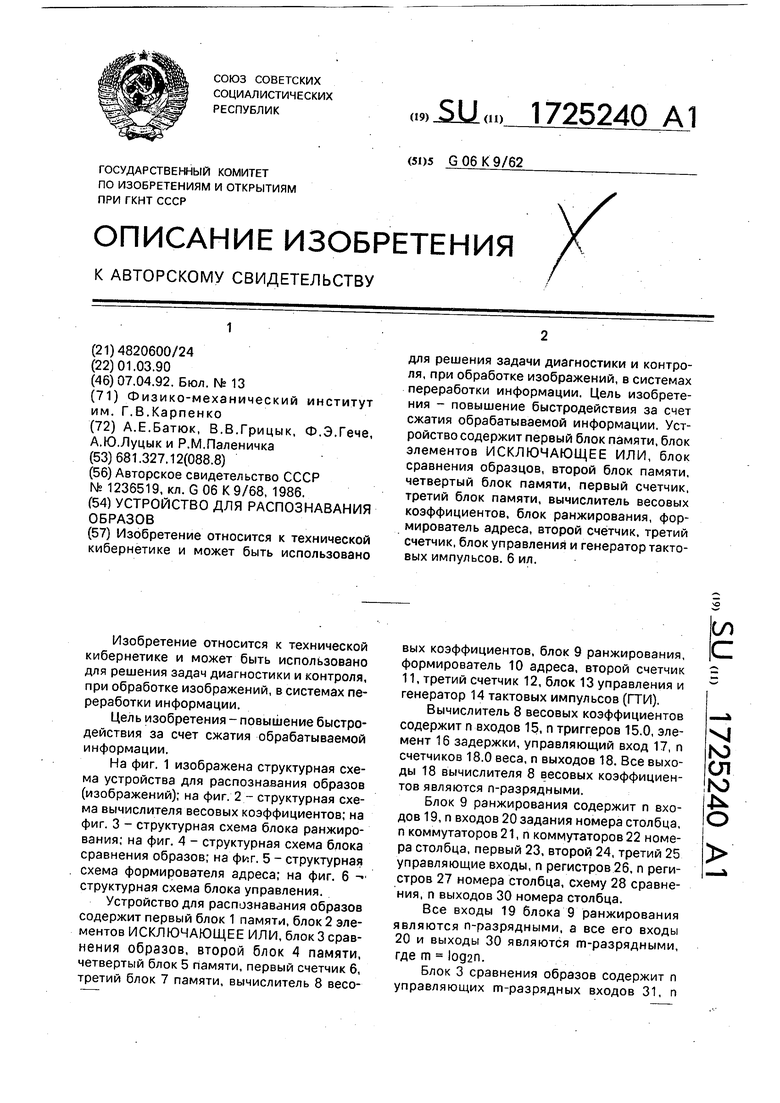

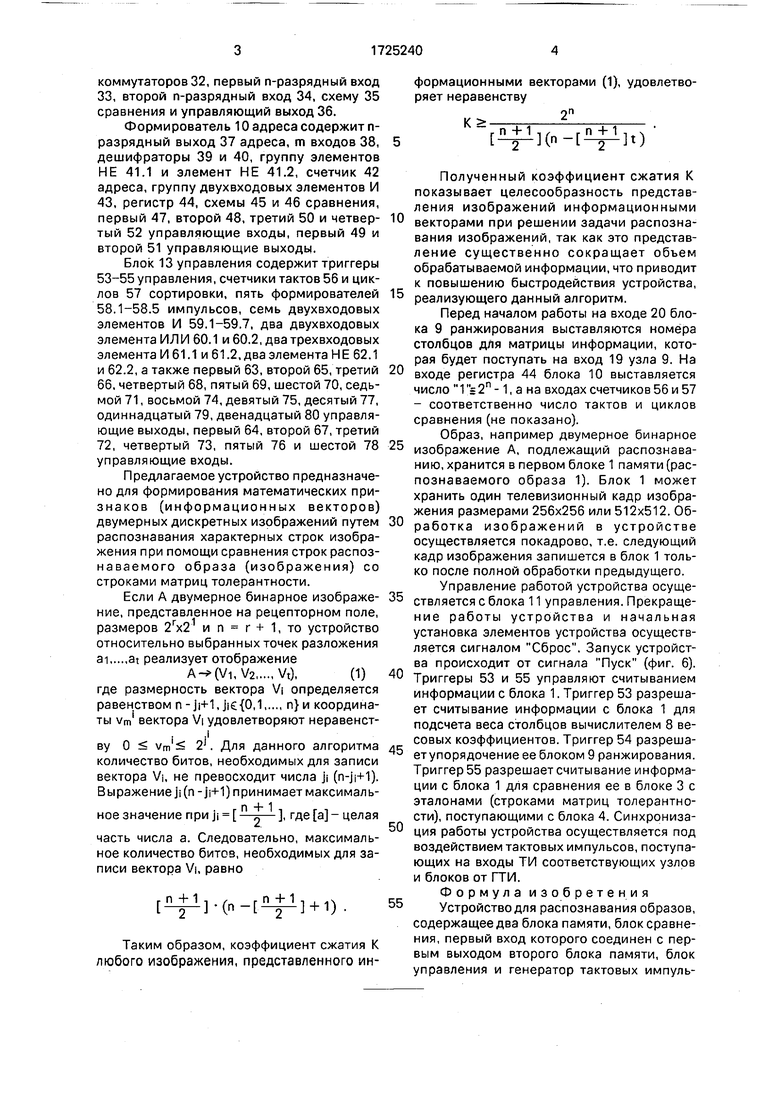

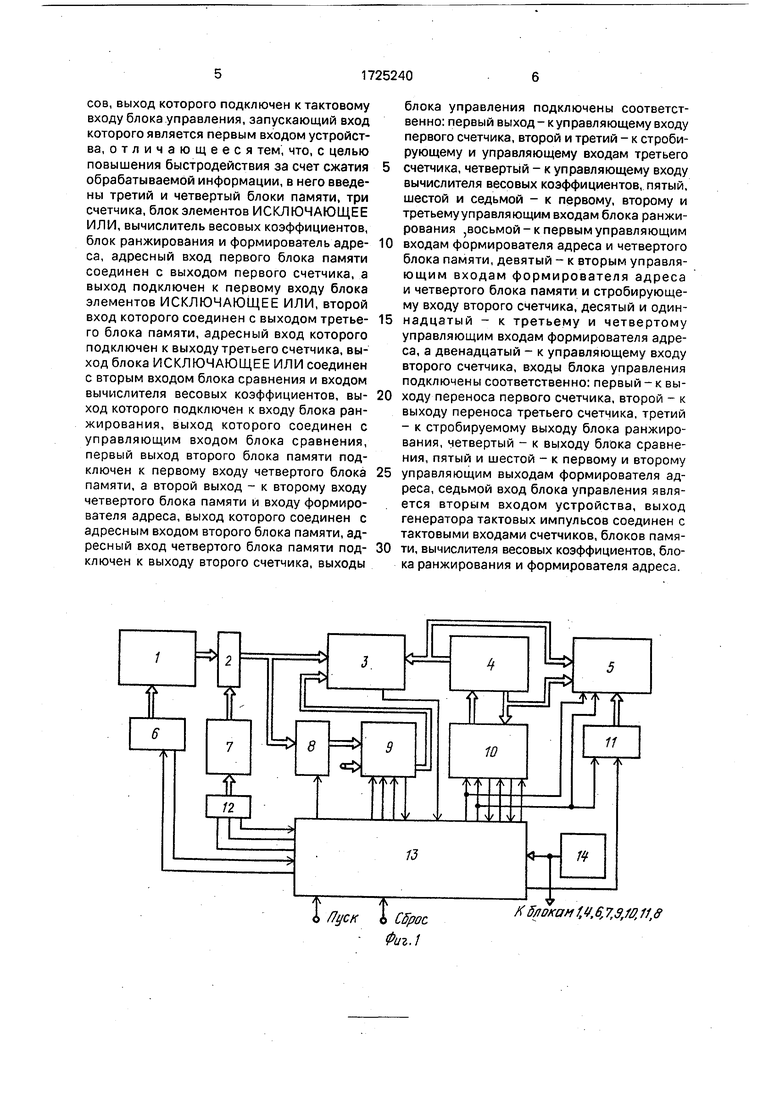

На фиг. 1 изображена структурная схема устройства для распознавания образов (изображений); на фиг. 2 - структурная схема вычислителя весовых коэффициентов; на фиг. 3 - структурная схема блока ранжирования; на фиг. 4 - структурная схема блока сравнения образов; на фиг. 5 - структурная схема формирователя адреса; на фиг. 6 структурная схема блока управления.

Устройство для распознавания образов содержит первый блок 1 памяти, блок 2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 3 сравнения образов, второй блок 4 памяти, четвертый блок 5 памяти, первый счетчик 6, третий блок 7 памяти, вычислитель 8 весовых коэффициентов, блок 9 ранжирования, формирователь 10 адреса, второй счетчик 11, третий счетчик 12, блок 13 управления и генератор 14 тактовых импульсов (ГТИ).

Вычислитель 8 весовых коэффициентов содержит п входов 15, п триггеров 15.0, элемент 16 задержки, управляющий вход 17, п счетчиков 18.0 веса, п выходов 18. Все выходы 18 вычислителя 8 весовых коэффициентов являются п-разрядными.

Блок 9 ранжирования содержит п входов 19, п входов 20 задания номера столбца, п коммутаторов 21, п коммутаторов 22 номера столбца, первый 23, второй 24, третий 25 управляющие входы, п регистров 26, п регистров 27 номера столбца, схему 28 сравнения, п выходов 30 номера столбца.

Все входы 19 блока 9 ранжирования являются n-разрядными, а все его входы 20 и выходы 30 являются т-разрядными, где т Iog2n.

Блок 3 сравнения образов содержит п управляющих m-разрядных входов 31, п

сл

с

XI ю ел

го

4 О

коммутаторов 32, первый n-разрядный вход 33, второй n-разрядный вход 34, схему 35 сравнения и управляющий выход 36.

Формирователь 10 адреса содержит п- разрядный выход 37 адреса, m входов 38, дешифраторы 39 и 40, группу элементов НЕ 41.1 и элемент НЕ 41.2, счетчик 42 адреса, группу двухвходовых элементов И 43, регистр 44, схемы 45 и 46 сравнения, первый 47, второй 48, третий 50 и четвер- тый 52 управляющие входы, первый 49 и второй 51 управляющие выходы.

Блок 13 управления содержит триггеры 53-55 управления, счетчики тактов 56 и циклов 57 сортировки, пять формирователей 58.1-58.5 импульсов, семь двухвходовых элементов И 59.1-59.7, два двухвходовых элемента ИЛ И 60.1 и 60.2, два трехвходовых элемента И 61.1 и 61.2, два элемента НЕ 62.1 и 62.2, а также первый 63, второй 65, третий 66, четвертый 68, пятый 69, шестой 70, седьмой 71, восьмой 74, девятый 75, десятый 77, одиннадцатый 79, двенадцатый 80 управляющие выходы, первый 64, второй 67, третий 72, четвертый 73, пятый 76 и шестой 78 управляющие входы.

Предлагаемое устройство предназначено для формирования математических при- знаков (информационных векторов) двумерных дискретных изображений путем распознавания характерных строк изображения при помощи сравнения строк распоз- наваемого образа (изображения) со строками матриц толерантности.

Если А двумерное бинарное изображе- ние, представленное на рецепторном поле, размеров 2гх21 и п г + 1, то устройство относительно выбранных точек разложения

aiat реализует отображение

A-(Vi,V2Vt),(1)

где размерность вектора Vj определяется равенством п - ji+1, ji€{0,1п}и координаты Vm вектора Vi удовлетворяют неравенству 0 vm 2. Для данного алгоритма количество битов, необходимых для записи вектора Vi, не превосходит числа ji (n-ji+1). Выражение ji(n-ji+1) принимает максимальное значение при ji

п + 1

, где целая

2. -50

часть числа а. Следовательно, максимальное количество битов, необходимых для записи вектора Vi, равно

г П + 1 л /Г П Ь 1 1 I 4

( + 1)

Таким образом, коэффициент сжатия К любого изображения, представленного информационными векторами (1), удовлетворяет неравенству

2п

К

гП+1,хг П + 1 , ч.

-у- (п )

5 10

15 0 5

0

5

0

5

0

5

Полученный коэффициент сжатия К показывает целесообразность представления изображений информационными векторами при решении задачи распознавания изображений, так как это представление существенно сокращает объем обрабатываемой информации, что приводит к повышению быстродействия устройства, реализующего данный алгоритм.

Перед началом работы на входе 20 блока 9 ранжирования выставляются номера столбцов для матрицы информации, которая будет поступать на вход 19 узла 9. На входе регистра 44 блока 10 выставляется число 1 2П - 1, а на входах счетчиков 56 и 57 - соответственно число тактов и циклов сравнения (не показано).

Образ, например двумерное бинарное изображение А, подлежащий распознаванию, хранится в первом блоке 1 памяти (распознаваемого образа 1). Блок 1 может хранить один телевизионный кадр изображения размерами 256x256 или 512x512. Обработка изображений в устройстве осуществляется покадрово, т.е. следующий кадр изображения запишется в блок 1 только после полной обработки предыдущего.

Управление работой устройства осуществляется с блока 11 управления. Прекраще- ние работы устройства и начальная установка элементов устройства осуществляется сигналом Сброс. Запуск устройства происходит от сигнала Пуск (фиг. 6). Триггеры 53 и 55 управляют считыванием информации с блока 1. Триггер 53 разрешает считывание информации с блока 1 для подсчета веса столбцов вычислителем 8 весовых коэффициентов. Триггер 54 разреша- етупорядочение ее блоком 9 ранжирования. Триггер 55 разрешает считывание информации с блока 1 для сравнения ее в блоке 3 с эталонами (строками матриц толерантности), поступающими с блока 4. Синхронизация работы устройства осуществляется под воздействием тактовых импульсов, поступающих на входы ТИ соответствующих узлов и блоков от ГТИ.

Формула изобретения

Устройство для распознавания образов, содержащее два блока памяти, блок сравнения, первый вход которого соединен с первым выходом второго блока памяти, блок управления и генератор тактовых импульсов, выход которого подключен к тактовому входу блока управления, запускающий вход которого является первым входом устройства, отличающееся тем, что, с целью повышения быстродействия за счет сжатия обрабатываемой информации, в него введены третий и четвертый блоки памяти, три счетчика, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вычислитель весовых коэффициентов, блок ранжирования и формирователь адреса, адресный вход первого блока памяти соединен с выходом первого счетчика, а выход подключен к первому входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом третьего блока памяти, адресный вход которого подключен к выходу третьего счетчика, выход блока ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом блока сравнения и входом вычислителя весовых коэффициентов, выход которого подключен к входу блока ранжирования, выход которого соединен с управляющим входом блока сравнения, первый выход второго блока памяти подключен к первому входу четвертого блока памяти, а второй выход - к второму входу четвертого блока памяти и входу формирователя адреса, выход которого соединен с адресным входом второго блока памяти, адресный вход четвертого блока памяти подключен к выходу второго счетчика, выходы

блока управления подключены соответственно: первый выход- куправляющему входу первого счетчика, второй и третий - к строби- рующему и управляющему входам третьего

счетчика, четвертый - к управляющему входу вычислителя весовых коэффициентов, пятый, шестой и седьмой - к первому, второму и третьемууправляющим входам блока ранжирования ,восьмой - к первым управляющим

входам формирователя адреса и четвертого блока памяти, девятый - к вторым управляющим входам формирователя адреса и четвертого блока памяти и стробирующе- му входу второго счетчика, десятый и одиннадцатый - к третьему и четвертому управляющим входам формирователя адреса, а двенадцатый - к управляющему входу второго счетчика, входы блока управления подключены соответственно: первый - к выходу переноса первого счетчика, второй - к выходу переноса третьего счетчика, третий - к стробируемому выходу блока ранжирования, четвертый - к выходу блока сравнения, пятый и шестой - к первому и второму

управляющим выходам формирователя адреса, седьмой вход блока управления является вторым входом устройства, выход генератора тактовых импульсов соединен с тактовыми входами счетчиков, блоков памяти, вычислителя весовых коэффициентов, блока ранжирования и формирователя адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| Устройство для распознавания подвижных объектов | 1988 |

|

SU1695337A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

Изобретение относится к технической кибернетике и может быть использовано для решения задачи диагностики и контроля, при обработке изображений, в системах переработки информации. Цель изобретения - повышение быстродействия за счет сжатия обрабатываемой информации. Устройство содержит первый блок памяти, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок сравнения образцов, второй блок памяти, четвертый блок памяти, первый счетчик, третий блок памяти, вычислитель весовых коэффициентов, блок ранжирования, формирователь адреса, второй счётчик, третий счетчик, блок управления и генератор тактовых импульсов. 6 ил.

6 Лцск А

Пуск 6 Сброс. Фиг.1

К блокам Wf7M1t,ff

25 ЬТИ .23 Риг. З

Г

W 48 Щ50 5f

Риг.5

52

| Устройство для распознавания образов | 1984 |

|

SU1236519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-07—Публикация

1990-03-01—Подача