Изобретение относится к радиотехнике и может быть использовано при создании балансных модуляторов, синхронных детекторов, регуляторов усиления и других высокочастотных устройств в интегральном исполнении.

Известна базовая схема, перемножителя, содержащая Первый- шестой транзисторы, первый и второй резисторы нагрузки, общая точка которых соединена с одним изLвывoдoв источника питания, и генератор тока, включенный Между вторым выводом питания и эмиттерами пятого и шестого транзисторов, объединенные базы первого и четвертого транзисторов являются первым входом пер1гмножителя. объединенные €азы второго и третьего транзисторов - его вторым вХодом,коллекторы первого и третьего транзисторов подключены к выводу первого резистора нагрузки, коллекторь второго и четвертого транзисторов - к выводу второго резистора

нагрузки, базы пятого и шестого транзисторов являются соответственно третьим и четвертым входами перемнржителя, коллектор пятого транзистора соединен с эмиттерами первого и второго транзисторов, а коллекторы шестого - с эмиттерами третьего и .четвертого..

Недостатком известного решения является низкая температурная стабильность коэффициента передачи, ограниченный частотный диапазон из-за влияния емкостей коллекторов и нагрузки, большое число выводов, препятствующее использованию подобных устройств в интегральных схемах со средней и большой степенью интеграции.

Часть указанных недостатков устранена в аналоговом перемножитеде, содержащем первый -девятый транзисторы, первый - третий токозадающие резисторы и каскад динамичес.крй нагрузки, попарно ненные базы первого и четвертого, в также

второго и третьего транзисторов являются симметричным входом для второго сигнала, коллекторы первого м третьего транзисторов подключены к первому входу динамической нагрузки, а коллекторы второго и четвертого - к ее второму входу, базы пятого и шестого транзисторов являются первым симметричным входом перемножителя, коллектор пятого транзистора соединен с эмитте|зами первого и второго транзисторов, а коллектор шестого -т с эмиттерами третьего и четвертого, базы седьмого, восьмого и девятого транзисторов соединены с коллектором девятого и подключены к источнику смещения, змиттеры седьмого, восьмого--и девятого транзисторов соответственно через первый, второй и третий токозадающие резисторы подключены к выводу источника питания, коллекторы седьмого и восьмого транзисторов соединены соответственно с змиттерами пятого и шестого транзисторов.

Входные сопротивления известного устройства по обоим входам сильно зависят от амплитуды входных сигналов, имеют значительную емкостную составляющую, что затрудняет согласование входов с внутренними сопротивлениями источников сигнала, приводит к снижению точности преобразования особенно для широкополосных сигналов,

Целью изобретения является повышение точности преобразования за счет стабилизации входных сопротивлений аналогового перемножителя.

Указанная цель достигается тем, что в аналоговый перемножитель, содержащий с первого по восьмой усилительные транзисторь, с первого по четвертый токозадаюЩие резисторы, блок динамической нагрузки, эмиттеры первого и второго усилительных транзисторов соединены между собой, змиттеры третьего и четвертого усилительных транзисторов соединены между собой, базы первого и четвертого усили-. тельных транзисторов соединены между собой, базы второго и третьего усилительных транзисторов соединены между собой, коллекторы первого и третьего усилительных транзисторов подключены к первому входу блока динамической нагрузки, к второму входу которого подключены коллекторы второго и четвертого усилительных транзисторов, коллектор и база пятого усилительного транзистора соединены с базой шестого усилительного транзистора, коллектор которого подключен к эмиттеру третьего усили тельного транзистора, шина питания блока динамической нагрузки соединена с первой шиной питания аналогового перемножителя, первой и второй выходными шинами которого являются первый и второй выходы блока динамической нагрузки, дополнительно введен блок динамической нагрузки,

первый и второй выходы которого подключены к базам соответственно первого и второго усилительных транзисторов, эмиттер первого усилительного транзистора соединен с первым выводом первого токоза0 дающего резистора, второй вывод которого через второй токозадающий резистор подключен к коллектору пятого усилительного транзистора, первый вход дополнительного блока; динамической нагрузки соединен

5 с первым выводом третьего токозадающего резистора, второй вывод которого через четвертый токозадающий резистор подк)1ючен к коллектору и базе седьмого усилительного транзистора и к базе восьмого

0 усилительного транзистора, коллектор которого соединен с вторым входом дополнительного блока динамической нагрузки, шина питания которого подключена к первой шине питания аналогового перемножителя, к

5 второй шине, питания которого подключен эмиттеры пятого, щестого, седьмого и восьмого усилительных транзисторов, вторые выводы первого и третьего токозадающих резисторов являются соответственно входами первого и второго сигналов - сомножителей аналогового перемножителя,

Техническая сущность предлагаемого решения состоит в способе формирования противофазных токов, когда один из токов

5 (неинвертированный) формируется подключением токораспреде.лительного узла множительной ячейки к источнику сигнала через инвертор с единичным усилением по току, образованным термокомпенсирован0 ным делителем напряжения, состоящим из второго токозадающего резистора и транзистора в диодном включении, и транзистором, включенным по схеме с общим змиттером. Это обеспечивает высокоста5 бильное частотно-независимое входное сопротивление аналогового перемнйжителя, позволяет существенно расширить динамический диапазон входных сигналов, по крайней, мере по первому, сигнальному входу,

0 Это существенно повышает точность преобразования и частотный диапазон аналогового перемножителя.

Известно использование инверторов тока с термокомпенсированным смещением и единичным усилением ло току для пе,рехода от двухполярйого симметричного Сигнала к однополярному несимметричному.

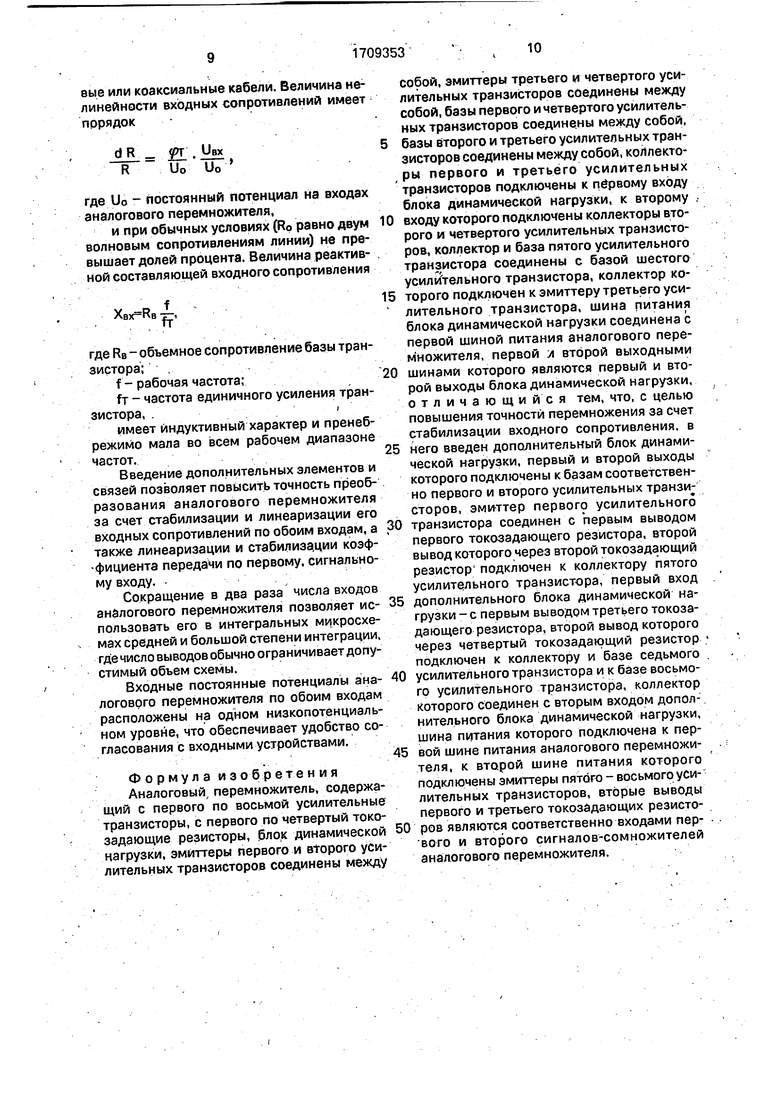

На фиг. 1.изображена принципиальная, схема аналогового перемножителя; на фиг.

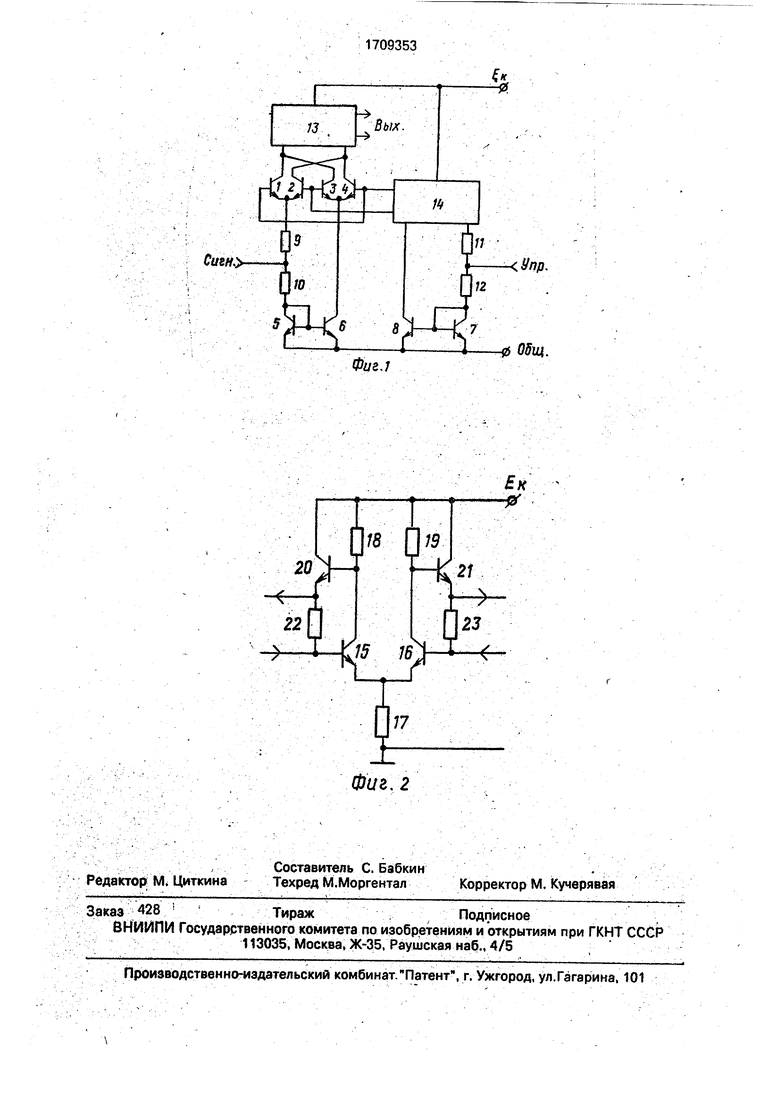

2 - принципиальная схема динамической нагрузки.

Аналоговый перемножитель содержит первый - восьмой транзисторы 1-8, первый - четвертый токозадающие резисторы 9-12, первую 13 и вторую 14 динамические нагрузки, базы первого 1 и четвертого 4 транзисторов подключены к первому выходу второй динамической нагрузки, базу второго 2 и третьего 3 - к ее второму выходу, коллекторы первого 1 и третьего 3 транзисторов соединены с первым входом первой динамической нагрузки 13, коллекторы второго 2 и четвертого 4 - с ее вторым входом, эмиттеры третьего 3 и четвертого 4 транзисторов соединены с коллектором шестого транзистора 6 непосредственно, а эмиттеры первого 1 И второго 2-е коллектором пятого транзистора 5, а также базами пятого транзистора 5 через последовательно соединенные четвертый 12 и третий, 11 токозадающие резисторы подключены к первому входу второй динамической нагрузки 14, коллектор восьмого транзистора 8 соединен с вторым входом второй динамической.нагрузки 14, эмиттеры пятого 5, шестого 6, седьмого 7 и восьмого 8 транзисторов соединены с вЬ1водом источника питания, второй вывод источника питания подключен к выводам первой 13 и второй 14 динамических нагрузок, общая . точка первого 9 и второго 10 токозадающих резисторов является первым, сигнальным входом аналогового перемножитёля, общая точка третьего 11 и четвертого 12 токозадающих резисторов - его вторым, управляющим входом, входами аналогового перемножителя являются выходы первой динамической нагрузки 13.

Динамическая нагрузка содержит дифференциальный усилительный каскад, выполненный на девятом 15 и десятом 16 транзисторах, базы которых являются входами динамической нагрузки. Эмиттеры обьединены и через змиттерный резистор 17 соединены с первым выводом источника питания, а коллекторы через первый 18 и второй 19 коллекторные резисторы подключены к второму выводу источника питания, змиттерные повторители 20,21 своими коллекторами подключены к выводу источника питания, базами - к коллекторам девятого 15 и десятого 16 транзисторов, их эмиттеры, являющиеся выходами динамической нагрузки, соединены с базами девятого 15 и десятого 16 транзисторов соответственно через первый 22 и второй 23 резисторы обратной связи.

Аналоговый перемножитель работает следующим образом.

От первого входа к первому токораспределительному узлу - змиттерам первого 1 и второго 2 транзисторов - через первый токозадающий резистор поступает ток hi. Поскольку входное сопротивление токораспределительного узла много меньше вели чины первого токозадающего резистора 9, величина тока, втекающего в первый токораспределительный узел, оказывается раеной

UBX

liHoiRo

где loi - постоянная составляющая тока;

RO - величина,токозадающего резистора;

Uexi - первое выходное напряжение.

От того же первого входа к второму токораспределительному узлу множительной ячейки - эмиттерам третьего 3 л четвертого 4 транзисторов - через тококомпенсированный делитель напряжения, образованный вторым токозадающим резистором 10 и пятым транзистором 5, включенным в диодном режиме, и инвертор, выполненный на шестом транзисторе 6, поступает ток Ii2. Так как выходное сопротивление тёрмокомпенсированного делителя практически равно величине второго токозадающего резистора 10, а коэффициент передачи по току инвертора с термокомпенсированным делителем напряжения равен единице, величина тока, втекающего во второй токораспределительный узел множительной ячейки, равна

ll2 loi+UBx1/Ro.

От второго входа аналогового перемножителя через третий токозадающий резистор 11 к первому входу второй динамической нагрузки 14 поступает ток 2. Входное сопротивление динамической нагрузки очень мало;

RBX RSI/K,

где RSI - величина сопротивления 22, 23 обратной второй динамической нагрузки 14;

К- коэффициент усиления дифференциального усилителя, выполненного на девятом 15 и десятом 16 транзисторах.

Поэтому величина тока, втекающего в первый вход второй динамической нагрузки, определится выражение

121 loa-UBxa/Ro.

От второго же входа аналогового перемножителя к второму входу второй динамической нагрузки 14 подается ток 122 через термокомпенсированный делитель напряжение, выполненный на четвертом токозадающем резисторе12 и седьмом транзисторе 7, включения в диодном режиме, и инвертор тока, выполненный на восьмом транзисторе 8, Так как козффициент усиления по току инвертора 8 и термокомпенсированного делителя напряжения 12,7 равен единице, величина тока, втекающего во второй динамической нагрузки 14, оказывается равнойI

i22 o2bUBx2/Ro.

Вторая динамическая нагрузка 14, имеющая козффициент передачи

dU

Rs,

где dl-разность входных токов;

dU - разность потенциалов на выходах второй динамической нагрузки 14,

формирует на входах множительной ячейки- базах первого 1, четвертого 4 и второго 2, третьего 3 транзисторов - разность потенциалов, пропорциональную второму входному сигналу

(l22-l2l).

Под действием этбго сигнала перераспределяются между транзисторами первым 1 и вторым 2, а,также третьим 3 и четвертым 4 токи, втекающие соответственно в первый и второй токораспределительные узлы. Для величины токов, протекающих через первый - четвертый транзисторы 1-4 можно записать

1о1 -UBXI/RO.

11

1 „ о1 UBXI/RO.

I IOI- UBXI/RO.

.

loi Uax1/Ro

l4

-eWa/

где (pj - температурный потенциал перехода, равный при Нормальной температуре 25 мВ.

На первый вход первой динамической нагрузки 13 поступают токи первого 1 и третьего 3 транзисторов:

1

UBXI Y1

RO 1 e-U2/ I

на второй вход той же динамической нагрузJO ки 13 поступают токи второго 2 и четвертого 4 транзисторов;

1

1

.

UBXI г 1 :

RO 1 (pT 1 gU2/

2Q Первая динамическая нагрузка, имеющая коэффициент передачи, равный

dU dl

-Rs2,

формирует на своих выходах симмет„- ричные противофазные напряжения с амплитудой

ШUBb,Xl +UBXl th

и.„.-и..,н tei,

или после замены напряжения U2 его 35 значением,найденным ранее,

LW . Rsi

ивых1 +ивх1 тЬ RO/

Ко

Предлагаемый аналоговый перемножиель обладает высокой линейностью по первому, сигнальному входу. Линейность его по второму, управляющему входу соответствует линейности прототипа. Это определяет

основные области испЪльзования предлагаемого решения - балансные модуляторы и смесители, синхронные детекторы, регуляторы усиления различных высокочастотных устройств.

Входное сопротивление аналогового перемножителя по обоим входам практически равно

RBX Ro/2,

стабильно и .частотно-независимо : в широком диапазоне частот, отличается большой линейностью, что обеспечивает-малые рассогласования с выходнымиИсточниками, сигналов, подключенными через полосковые или коаксиальные кабели. Величина нелинейности входных сопротивлений имеет порядок

уУГ . UBX

dR R

Uo Uo

где Uo - постоянный потенциал на входах аналогового перемножителя,

и при обычных условиях (RP равно двум волновым сопротивлениям линии) не превышает долей процента. Величина реактивной составляющей входного сопротивления

-r-i

где RB - объемное сопротивление базы транзистора; ,

f-рабочая частота;

fj - частота единичного усиления транзистора, .

имеет индуктивный характер и пренебрежимо мала во всем рабочем диапазоне частот.

Введение дополнительных элементов и связей позволяет повысить точность преобразования аналогового перемножителя за счет стабилизации и линеаризации его входных сопротивлений по обоим входам, а также линеаризации и стабилизации козффициента передачи по первому, сигнальному входу. Сокращение в два раза числа входов аналогового перемножителя позволяет использовать его в интегральных мцкросхемах средней и большой степени интеграции, гДе число выводов обычно ограничивает допустимый объем схемы.

Входные постоянные потенциалы аналогового перемножителя по обоим входам расположены на одном низкопотенциальном уровне, что обеспечивает удобство согласования с входными устройствами.

Формулаизобретения Аналоговый, перемножитель, содержащий с первого по восьмой усилительные транзисторы, с первого по четвертый токозадающие резисторы, бло,к динамической нагрузки, эмиттеры первого и Btoporo усилительных транзисторов соединены между

собой, змиттеры третьего и четвертого усилительных транзисторов соединены между собой, базы первого и четвертого усилительных транзисторов соединены между собой,

базы второго и третьего усилительных транзисторов соединены между собой, коллекторы первого и третьего усилительных транзисторов подключены к первому входу блока динамической нагрузки, к второму .

входу которого подключены коллекторы второго и четвертого усилительных транзисторов, коллектор и база пятого усилительного транзистора соединены с базой шестого усилительного транзистора, коллектор которого подключен к эмиттеру третьего усилительного транзистора, шина питания блока динамической нагрузки соединена с первой шиной питания аналогового перемножителя, первой л второй выходными

шинами которого являются первый и второй выходы блока динамической нагрузки, отличающийся тем, что, с целью повышения точности перемножения за счет стабилизации входного сопротивления, в

него введен дополнительный блок динамической нагрузки, первый и второй выходы которого подключены к базам соответственно первого и второго усилительных транзи; сторов, первого усилительного

транзистора соединен с первым выводом первого токозадающего резистора, второй вывод которого через второй токозадающий резистор подключен к коллектору пятого усилительного транзистора, первый вход

дополнительного блока динамической нагрузки-с первым вы водом третьего токозадающего резистора, второй вывод которого через четвертый токозадающий резистор подключен к коллектору и базе седьмого

усилительного транзистора и к базе восьмого усилительного транзистора, коллектор которого соединен с вторым входом допол-, нительного блока динамической нагрузки, шина питания которого подключена к первой шине питания аналогового перемножителя, к второй шине питания которого подключены эмиттеры пятого - восьмого усилительных транзисторов, вторые выводы первого и третьего токозадающих резисторов являются соответственно входами пер- вого и второго сигналов-сомножителей аналогового перемножителя.

ftfSM

Упр.

0 Одщ.

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок перемножителей функций | 1987 |

|

SU1506563A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Устройство для выделения максимального сигнала | 1980 |

|

SU959098A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

| ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ | 1991 |

|

RU2094942C1 |

| Аналоговый перемножитель сигналов | 1989 |

|

SU1626257A1 |

| Фазовый дискриминатор | 1991 |

|

SU1800583A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419190C1 |

| Операционный усилитель | 1986 |

|

SU1396242A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности перемножения за счет стабилизации входного сопротивления. Аналоговый перемножитель содержит с первого по восьмой усилительные транзисторы 1-8, с первого по четвертый токозада- ющие резисторы 9-12, блок 13 динамической нагрузки, дополнительный блок 14 динамической нагрузки. Работа аналогового перемножителя по перемноженик) двух сигналов-сомножителей основана на реализации метода переменной крутизны. 2 ил.

Фиг. 2

| Тимонтеев В.Н. | |||

| Величко П.М., Ткачен- ко В.А | |||

| Аналоговые перемножители сигналов в радиоэлектронной аппаратуре | |||

| М.: Радио и связь, 1982 | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1992-01-30—Публикация

1989-08-11—Подача