4

4 4

00

vl

Изобретение относится к области передачи и преобразования сигналов и может быть применено в информационно-измерительных системах. В промыш- ленных информационно-измерительных системах в качестве источника информации используются промьшшенные системы телемеханики, которые передают сигналы с ширртно-импульсной модуля- цией. Для обеспечения возможности ввода таких сигналов в групповой информационный тракт, например связи с ЭВМ, необходимо преобразовать ши- ротно-импульсные сигналы в двоичные коды соответсч вующего формата, запомнить их и на заданном такте ввести в групповой информационный тракт.

Целью изобретения является повышение достоверности передачи инфор- мации.

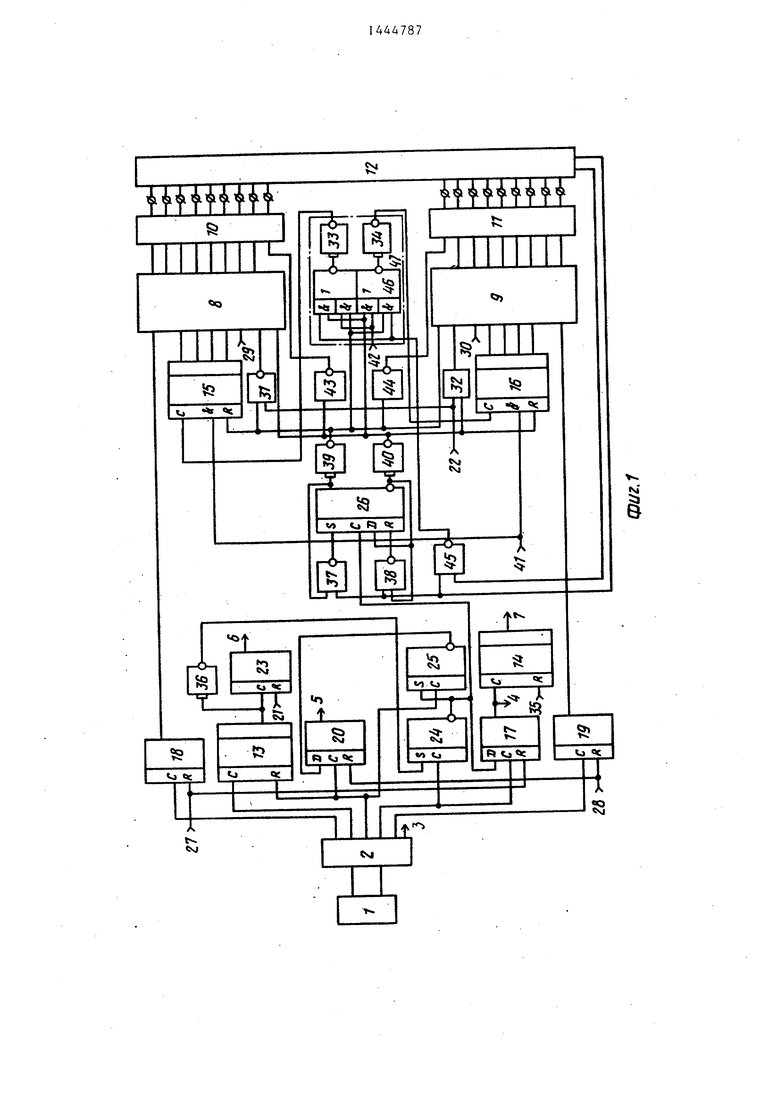

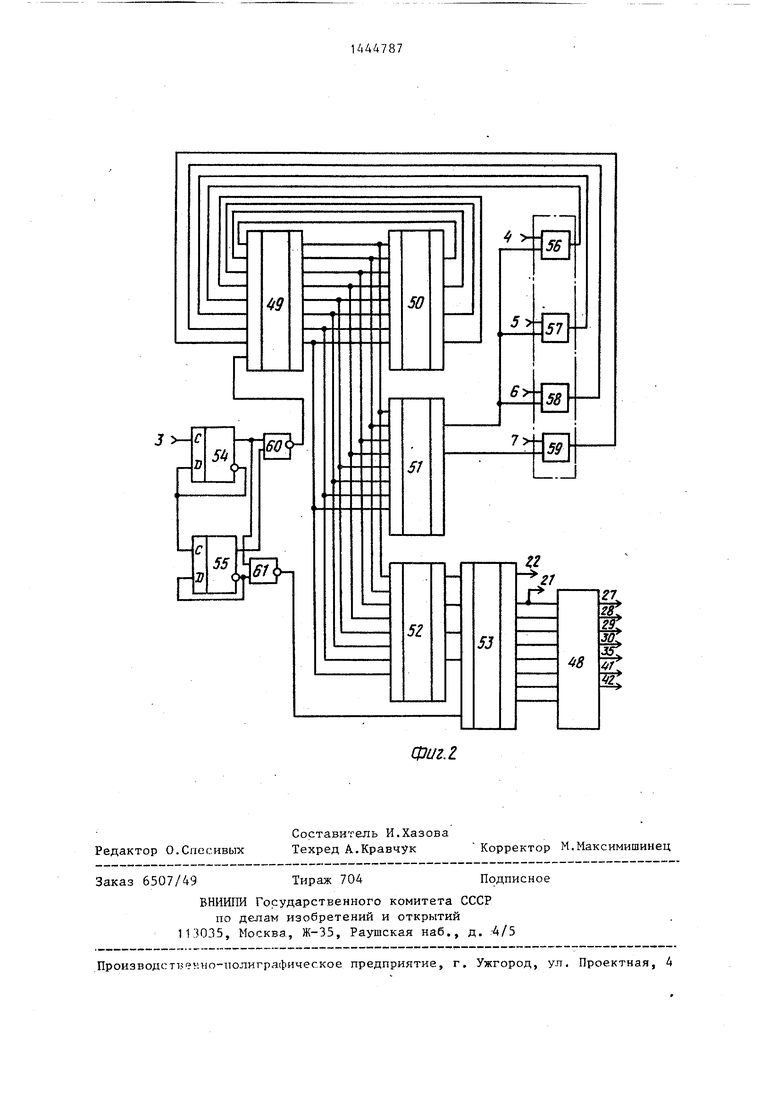

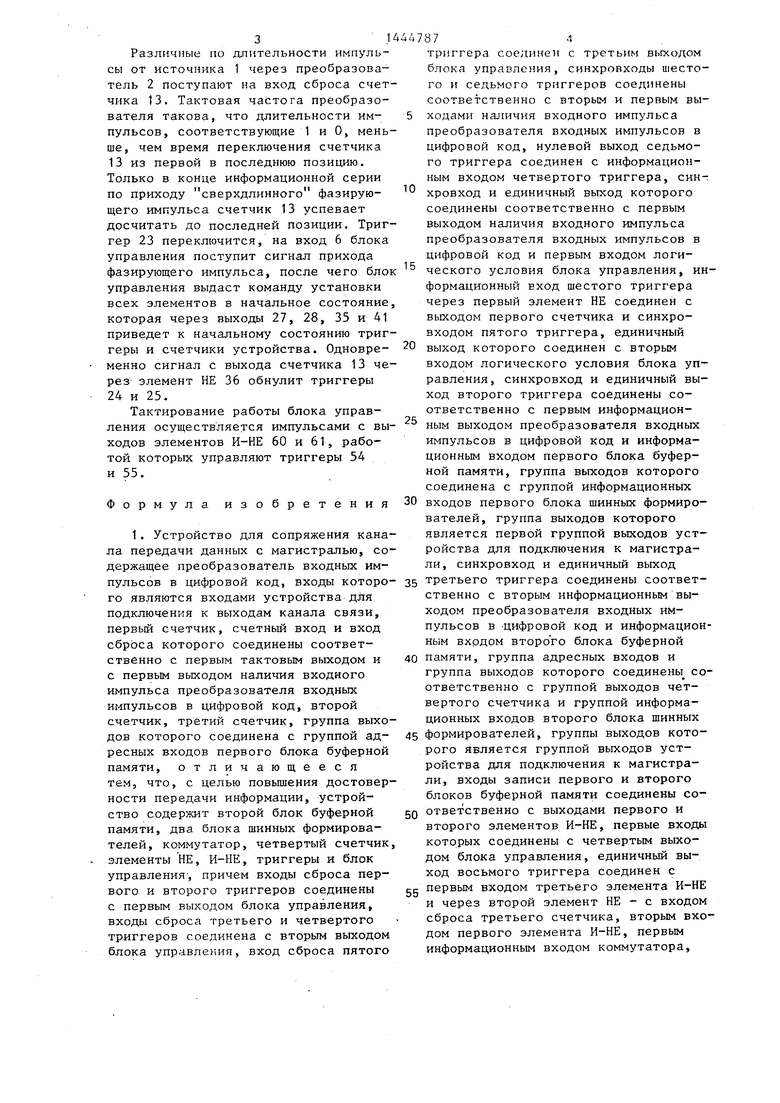

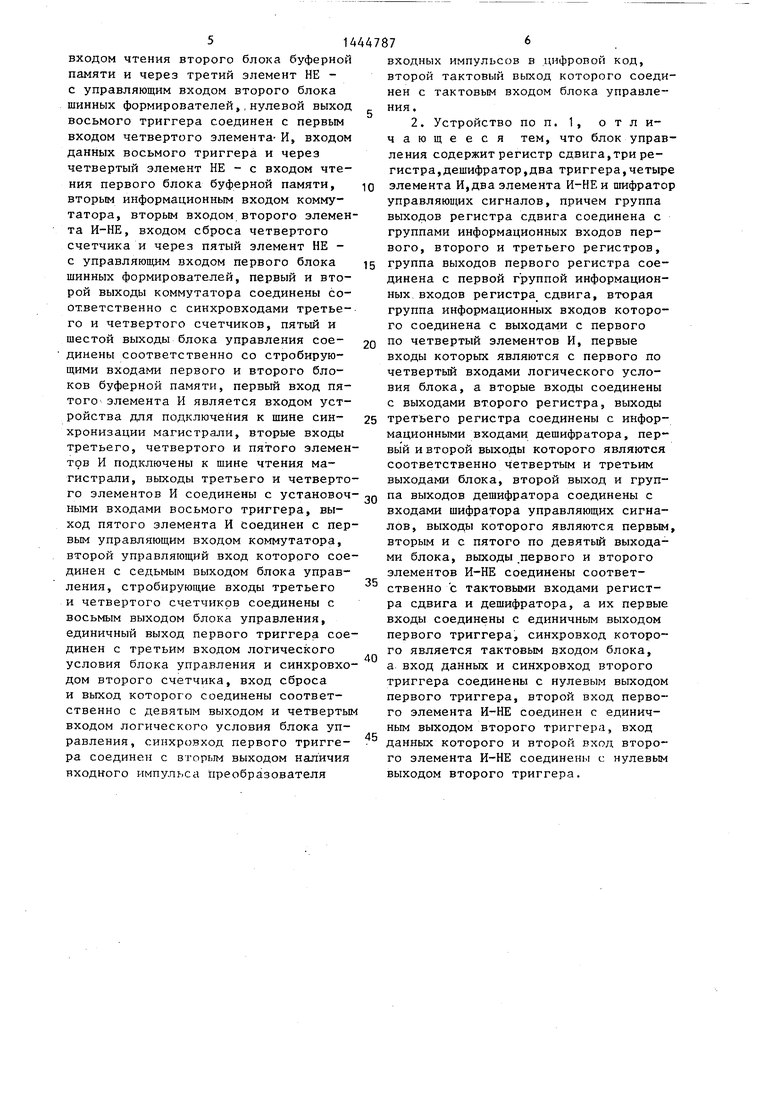

На фиг. 1 показана схема устрой-, ства-, на фиг. 2 - схема блока управления. . .

Устройство содержит источник 1

ъ,входных импульсов (канал связи), преобразователь 2 входных импульсов в цифровой код, входы 3-7 блока управления, блоки 8, 9 буферной памяти, блоки 10, 11 шинных формирователей, магистраль 12, счетчики 13-16, триггеры 17-20, третий и четвертый выходы 21, 22 блока управления, триггеры 23-26, первый, второй, пятый и шестой выходы 27-30 блока управления, элементы И-НЕ 31, 32, элементы НЕ 33, 34, девятый выход 35 блока управления, первый элемент НЕ 36, третий и четвертый элементы И-НЕ 37, 38, второй и четвертый элементы НЕ 39, 40, восьмой и седьмой выходы 41,42 блока управления, пятый и третий элементы НЕ 43, 44, пятый элемен И-НЕ 45, коммутатор 47, состоящий из элемента И-ИЛИ 46 и элементов НЕ 33, 34.

Блок управления.устройства (см. фиг. 2) содержит шифратор 48 управляющих сигналов, регистр 49 сдвига, первый, второй и третий регистры 50, 51, 52 (буферной памяти), дешифратор 53, первый и второй триггеры 54 и 55, первый - четвертый элементы И 56-59, первый и второй элементы И-НЕ 60, 61.

Устройство работает следующим об- разом.

Импульсы с выходов преобразоватв ля 2 через соответствующие триггеры

O 5

0

5

O

5

5

0

5

0

18 и 19 поступают на входы блоков 8 и 9. Блоки 8 и 9 памяти представляют собой последовательно соединенные регистр сдвига, выполненный на микросхеме К155ИР1, и память, выполненную на микросхеме К155РУ2.

Синхронизация работы всех узлов устройства осуществляется блоком управления (см. фиг. 2), основу которого составляет регистр 49 сдвига, к , выходам которого подключены три регистра 50, 51 и 52 памяти и дешифратор 53. Для формирования управляющих воздействий информация о работе элементов и блоков устройства, а так-. же тактовые импульсы поступают на входы элементов И 56-59 и триггера 54. На выходах элементов И 56-59 в моменты совпадения сигналов от блока управления и соответствующих узлов схемы появляются сигналы, которые поступают на соответствующие входы регистра 49 сдвига и задают требуемое управляющее воздействие. Последовательность чередования импульсов на выходах 21,22,27-30, 35,41,42 определяется регистрами 50, 51 и 52 буферной памяти, в которые предварительно записана информация о последовательности чередования сигналов на выходах дешифратора 53. Управляющие сигналы с выходов дешифратора 53 стробир уют моменты переключения основных функциональных элементов и блоков устройства.

Для повышения достоверности передачи сигналов запись информации осуществляется параллельно в первый и второй блоки 8 и 9 одновременно, если сигналов из магистрали 12 не поступало. Разрешение на запись при приходе от блока управления соответствующего сигнала поступает через элементы И-НЕ 31 и 32. Смена же адреса (опять при разрешающем сигнале от блока управления) осуществляется через .коммутатор. Если из магистрали поступают сигналы обращения к устройству, то через элементы 37-40, 43-45 и триггер 2б устройство переводится в состояние, когда в один блок буферной памяти информация будет продолжать записьшаться, а из другого будет поступать в магистраль. Для согласования выходов блоков буферной памяти с магистралью используются блоки шинных формирователей 10 и 11.

3и

Различные по длительности импульсы от источника 1 через преобразователь 2 поступают на вход сброса счетчика 13. Тактовая частота преобразователя такова, что длительности импульсов, соответствующие 1 и О, меньше, чем время переключения счетчика 13 из первой в последнюю позицию. Только в конце информационной серии по приходу сверхдлинного фазирующего импульса счетчик 13 успевает досчитать до последней позиции. Триггер 23 переключится, на вход 6 блока управления поступит сигнал прихода фазирующего импульса, после чего блок управления выдаст команду установки всех элементов в начальное состояние которая через выходы 27, 28, 35 и 41 приведет к начальному состоянию триггеры и счетчики устройства. Одновременно сигнал с выхода счетчика 13 через элемент НЕ 36 обнулит триггеры 24 и 25.

Тактирование работы блока управления осуществляется импульсами с выходов элементов И-НЕ 60 и 61, работой которых управляют триггеры 54 и 55.

Формула изобретения

1. Устройство для сопряжения канала передачи данных с магистралью, содержащее преобразователь входных импульсов в цифровой код, входы которого являются входами устройства для подключения к выходам канала связи, первый счетчик, счетный вход и вход сброса которого соединены соответственно с первым тактовым выходом и с первым выходом наличия входного импульса преобразователя входных импульсов в цифровой код, второй счетчик, третий счетчик, группа выходов которого соединена с группой адресных входов первого блока буферной памяти, отличающееся тем, что, с целью повьпления достоверности передачи информации, устройство содержит второй блок буферной памяти, два блока шинных формирователей, коммутатор, четвертый счетчик, элементы НЕ, И-НЕ, триггеры и блок управления , причем входы сброса первого и второго триггеров соединены с первым выходом блока управления, входы сброса третьего и четвертого триггеров соединена с вторым выходом блока управления, вход сброса пятого

0

Д7874

триггера соединен с третьим выходом блока управления, синхровходы шестого и седьмого триггеров соединены соответственно с вторым и первым выходами наличия входного импульса преобразователя входных импульсов в цифровой код, нулевой выход седьмого триггера соединен с информационным входом четвертого триггера, син- хровход и единичный выход которого соединены соответственно с первым выходом наличия входного импульса преобразователя входных импульсов в цифровой код и первым входом логического условия блока управления, информационный вход шестого триггера через первый элемент НЕ соединен с выходом первого счетчика и синхро- входом пятого триггера, единичный

0 выход которого соединен с вторым

входом логического условия блока управления, синхровход и единичный выход второго триггера соединены соответственно с первым информацион ным выходом преобразователя входных импульсов в цифровой код и информационным входом первого блока буферной памяти, группа выходов которого соединена с группой информационных

0 входов первого блока шинных формирователей, группа выходов которого является первой группой выходов устройства для подключения к магистрали, синхровход и единичный выход

5 третьего триггера соединены соответственно с вторым информационным выходом преобразователя входных импульсов в -цифровой код и информационным входом второго блока буферной

0 памяти, группа адресных входов и

группа выходов которого соединены соответственно с группой выходов четвертого счетчика и группой информационных входов второго блока шинных

5 формирователей, группы выходов которого является группой выходов устройства для подключения к магистрали, входы записи первого и второго блоков буферной памяти соединены соQ ответственно с выходами первого и второго элементов И-НЕ, первые входы которых соединены с четвертым выходом блока управления, единичный выход восьмого триггера соединен с

е первым входом третьего элемента И-НЕ и через второй элемент НЕ - с входом сброса третьего счетчика, вторым входом первого элемента И-НЕ, первым информационным входом коммутатора.

входом чтения второго блока буферной памяти и через третий элемент НЕ - с управляющим входом второго блока шинных формирователей,,нулевой выход восьмого триггера соединен с первым входом четвертого элемента- И, входом данных восьмого триггера и через четвертый элемент НЕ - с входом чтения первого блока буферной памяти, вторым информационным входом коммутатора, вторым входом второго элемента И-НЕ, входом сброса четвертого счетчика и через пятый элемент НЕ - с управляющим входом первого блока шинных формирователей, первый и второй выходы коммутатора соединены соответственно с синхровходами третьего и четвертого счетчиков, пятый и шестой выходы блока управления сое- динены соответственно со стробирую- щими входами первого и второго блоков буферной памяти, первый вход пятого элемента И является входом устройства для подключения к шине син- хронизации магистрали, вторые входы третьего, четвертого и пятого злемен- тфв И подключены к шине чтения магистрали, выходы третьего и четвертого элементов И соединены с установоч- ными входами восьмого триггера, выход пятого элемента И Соединен с первым управляющим входом коммутатора, второй управляющий вход которого соединен с седьмым выходом блока управления, стробирующие входы третьего и четвертого счетчиков соединены с восьмым выходом блока управления, единичный выход первого триггера соединен с третьим входом логического условия блока управления и синхровхо- дом второго счетчика, вход сброса и выход которого соединены соответственно с девятым выходом и четвертым

входом логического условия блока управления, синхровход первого тригге-

ра соединен с вторым выходом наличия входного импульса Преобразователя

5 д

ц

0

входных импульсов в цифровой код, второй тактовый выход которого соединен с тактовым входом блока управления.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит регистр сдвига,три регистра, дешифратор,два триггера,четыре элемента И, два элемента И-НЕ и шифратор управляющих сигналов, причем группа выходов регистра сдвига соединена с группами информационных входов первого, второго и третьего регистров, группа выходов первого регистра соединена с первой группой информационных входов регистра сдвига, вторая группа информационных входов которого соединена с выходами с первого по четвертый элементов И, первые входы которых являются с первого по четвертый входами логического условия блока, а вторые входы соединены с выходами второго регистра, выходы третьего регистра соединены с информационными входами дешифратора, первый и второй выходы которого являются соответственно четвертым и третьим выходами блока, второй выход и группа выходов дешифратора соединены с входами шифратора управляющих сигналов, выходы которого являются первым, вторым и с пятого по девятый выходами блока, выходы первого и второго элементов И-НЕ соединены соответственно с тактовыми входами регистра сдвига и дешифратора, а их первые входы соединены с единичньм выходом первого триггера, синхровход которого является тактовым входом блока, а вход данных и синхровход второго триггера соединены с нулевым выходом первого триггера, второй вход первого элемента И-НЕ соединен с единичным выходом второго триггера, вход данных которого и второй вход второго элемента И-НЕ соединены с нулевым выходом второго триггера.

фиг.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

Изобретение относится к области передачи и преобразования сигналов и может быть применено в информационно-измерительных системах. Целью изобретения является повьшение достоверности передачи информации. Для достижения данной цели в устройство введены второй блок буферной памяти, блоки шинных формирователей, счетчики, триггеры, элементы И-НЕ, исключая тем самым потерю информации при обмене ею с магистралью, а также блок управления, осуществляющий стро- бирование моментов переключения элементов схемы и предотвращающий сбои логических элементов при работе устройства. Применение устройства не дает сбоев при работе и обеспечивает достоверность преобразуемых сигналов, что актуально при эксплуатации в составе промышленных комплексов автоматизированных систем управления. 1 3.п. ф-лы, 2 ил. (Л

| Устройство для ввода информации | 1985 |

|

SU1305692A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Труды ВНИИЖТ | |||

| М.: Транспорт, 1985, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1988-12-15—Публикация

1986-07-28—Подача