Изобретение относится к импульсной технике и может быть использовано в вычислительной технике повышенной производительности.

Целью изобретения является уменьшение асимметрии выходных сигналов путем применения обратной связи между выходными транзисторами схемы.

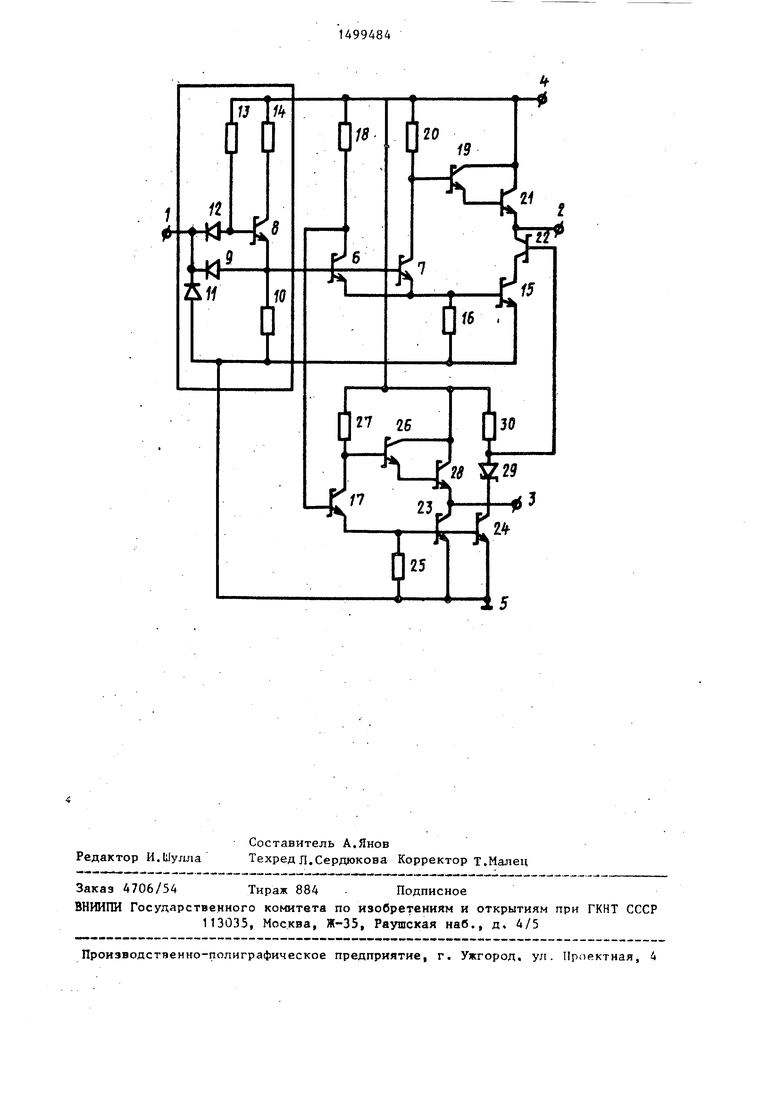

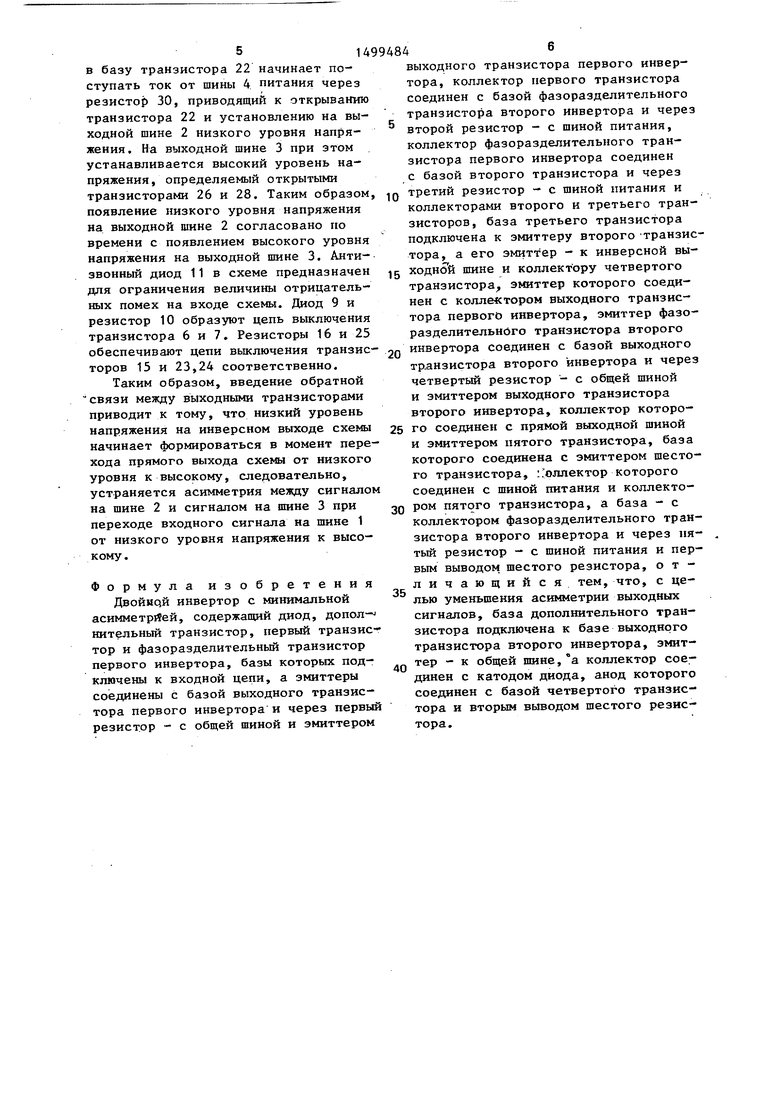

На чертеже представлена электри- чес|сая принципиальная, схема двойного инвертора с минимальной асимметрией.

Двойной инвертор с минимальной асимметрией содержит входную шину 1, -инверсную выходную шину 2, прямую выходную шину 3, шину 4 питания, общую шину 5, первый транзистор 6 и фазо- разделительный транзистор 7 первого инвертора, базы которых соединены вместе и подключены к эмиттеру входного транзистора 8, аноду первого .

диода 9 Шоттки и через седьмой резистор 10 к общей шине 5 и аноду второго диода 11 Шоттки, катод которого подключен к катоду первого диода 9 Шоттки, входной шине 1 и катоду третьего диода 12, анод которого подключен к базе входного транзистора 8 и через восьмой резистор 13 к шине 4 питания и первому выводу девятого резистора 14, второй вывод которого соединен с коллектором входного транзистора 8, эмиттеры первого 6 и фазо- разделительного 7 транзисторов первого инвертора соединены с базой выходного транзистора 15 первого инвертора и через первый резистор 16 с общей шиной 5 и эмиттером выходного тран- зистора 15 первого инвертора, коллектор первого транзистора 6 соединен с базой фазоразделительного транзисто

СО

со

4:: 00 4

31499

pa 17 второго инвертора и через вто- дой резистор 18 с шиной 4 питания, коллектор фазоразделительного транзистора 7 первого инвертора соединен с базой Второго транзистора 19 и через третий резистор 20 с шиной 4 питания и коллекторами второго 19 и третьего 21 транзисторов, база третьего транзистора 21 подключена к эмит- теру второго транзистора 19, а его эмитт6 р - к инверсной выходной шине 2 и коллектору четвертого транзистора 22, эмиттер которого соединен с коллектором выходного транзистора первого инвертора 15, эмиттер фазоразделительного транзистора 17 второго инвертора соединен с базой выходного транзистора 23 второго инвертора и базой дополнительного транзисто- ра 24, эмиттеры которых соединены и подключены к общей шине 5 и через четвертый резистор 25 к эмиттеру фа- зоразделительного транзистора второго инвертора 17, коллектор которого подключен к базе шестого транзистора 26 и через пятый резистор 27 к шине 4 питания, коллектору пятого транзистора 28 и коллектору шестого транзистора 26, эмиттер которого подклюг чен к базе пятого транзистора 28, эмиттер которого подключен к прямой выходной шине 3 и коллектору выходного транзистора 23 второго инвертора.

коллектор дополнительного транзисто-

ра 24 соединен с катодом диода 29, анод которого соединен с базой четвертого транзистора 22 и через шестой резистор 30 с шиной 4 питания.

Двойной инвертор работает следую- щим образом..,

.Если на входную шину 1 подан низкий уровень напряжения, тй диод 12 открыт, а транзисторы 8,6,7 и 15 закрыты, так как отсутствует ток в ба- зовых цепях этих транзисторов. На инверсной выходной шине 2 сформируется высокий уровень напряжения, определяемый открытыми транзисторами 19 и 21. Высокий уровень напряжения на коллекторе закрытого транзистора 6 приводит к появлению тока в базовой цепи транзистора 17. Транзистор 17 . открывается, ч ток начинает протекать через резисчор 27, образующий базовый ток тр.чиг исторов 23 и 24. Открытый транзистор 23 формирует на прямой выходной шипе .) низкий уровень напряжения. Открытий транзпситр 4 и sip

ю 5 20 25 30

35

..д

.,

5

мосмещенный диод 29 формирует на базе транзистора 22 низкий уровень напряжения, равный

AUгy (Эt4

где и, - напряжение на базе транзистора 22; 43 - напряжение на прямосмещенном диоде Шоттки 29; Ujj324 напряжение между коллекто;;ром и эмиттером ОТКРЫТОГО

транзистора 24.

Следовательно, при наличии на шине 1 низкого уровня напряжения на ° шине 2 формируется высокий уровень напряжения, а на шине 3 - низкий уровень напряжения. При изменении на шине 1 напряжения с низкого уровня на высокий диод 12 закрывается, в базу транзистора 8 постуц ет ток от шины 4 через резистор 13, транзистор 8 открывается, начинает протекать ток о через резистор 14 в базу транзисто- :: ро% 6 и 7. Транзисторы. 6 и 7 открываются, в коллекторных цепях ,этих транзисторов появляются токи, определяемые резисторами 18 и 20, которые, поступая в базу транзистора 15, открывают его. Таким образом, на коллекторе транзистора 15 формируется низкий уровень напряжения. Однако на базе транзистора 22 поддерживает- ся уровень напряжения U, определяемый открытым транзистором 24, эмиттер которого соединен с общей шиной 5 и прямосмещенным диодом 29, недостаточный для его отпирания, и, таким образом, на выходной шине 2 продолжает отсутствовать,низкий уровень напряжения. Выключение транзистора 17 приводит.к выключению .транзистора 23, а также выключению транзистора 24, коллекторное напряжение которого отслеживает измё неиие напряжения на коллекторе транзистора 23, т.е. на - выходной шине 3. При достижении на коллекторе транзистора 24 напряжения, равного

Ua UK3ts U53«-UA« « где и - напряжение на коллекторе

транзистора 24;

напряжение между коллектором и эмиттером открытого транзистора 15;

Ugj 21 напряжение прямосмещенного- бляа - эмиттер транзис:1О1 л 22;

и. -J- напряжептте n.i прямосмрщенНОМ ЯНОД(; ) IJor-1-КИ,

в базу транзистора 22 начинает поступать ток от шины 4 питания через резистор 30, приводящий к открыванию транзистора 22 и установлению на выходной шине 2 низкого уровня напряжения. На выходной шине 3 при этом устанавливается высокий уровень напряжения, определяемый открытыми транзисторами 26 и 28. Таким образом появление низкого уровня напряжения на выходной шине 2 согласовано по времени с появлением высокого уровня напряжения на выходной шине 3. Анти- звонный диод 11 в схеме предназначен для ограничения величины отрицательных помех на входе схемы. Диод 9 и резистор 10 образуют цепь выключения транзистора 6 и 7, Резисторы 16 и 25 обеспечивают цепи выключения транзисторов 15 и 23,24 соответственно.

Таким образом, введение обратной связи между выходными транзисторами приводит к тому, что низкий уровень напряжения на инверсном выходе схемы начинает формироваться в момент перехода прямого выхода схемы от низкого уровня к высокому, следовательно, устраняется асимметрия между сигналом на шине 2 и сигналом на шине 3 при переходе входного сигнала на шине 1 от низкого уровня напряжения к высокому .

Формула изобретения

Двойицй инвертор с минимальной асимметрией, содержащий диод, допол- нительный транзистор, первый транзис- тор и фазоразделительный транзистор первого инвертора, базы которых подключены к входной цепи, а эмиттеры соединены с базой выходного транзистора первого инвертора и через первый резистор - с общей шиной и эмиттером

выходного транзистора первого инвертора, коллектор первого транзистора соединен с базой фазоразделительного транзистора второго инвертора и через второй резистор - с шиной питания, коллектор фазоразделительного транзистора первого инвертора соединен с базой второго транзистора и через

Q третий резистор - с шиной питания и коллекторами второго и третьего транзисторов, база третьего транзистора подключена к эмиттеру второго транзистора, а его эмиттер - к инверсной выg ходной шине и коллектору четвертого транзистора, эмиттер которого соединен с колле«тором выходного транзистора первого инвертора, эмиттер фазо- разделительнйго транзистора второго

Q инвертора соединен с базой выходного транзистора второго инвертора и через четвертый резистор - с общей шиной и эмиттером выходного транзистора второго инвертора, коллектор которо5 го соединен с прямой выходной щиной и эмиттером пятого транзистора, база которого соединена с эмиттером шестого транзистора, ::;оллектор которого соединен с шиной питания и коллектоQ ром пятого транзистора, а база - с коллектором фазоразделительного транзистора второго инвертора и через пятый резистор - с шиной питания и первым выводом, шестого резистора, отличающийся тем, что, с целью уменьшения асимметрии выходных сигналов, база дополнительного транзистора подключена к базе выходного транзистора второго инвертора, эмиттер - к общей шине,а коллектор соединен с катодом диода, анод которого соединен с базой четвертого транзистора и вторым выводом шестого резистора ,

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| Схема согласования уровней ТТЛ-ЭСЛ | 1985 |

|

SU1309301A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительной и микропроцессорной технике, в системах повышенной производительности. Целью изобретения является уменьшение асимметрии выходных сигналов путем применения обратной связи между выходными транзисторами. Двойной инвертор содержит входную цепь, два инвертора, база дополнительного транзистора подключена к базе выходного транзистора второго инвертора, эмиттер - к общей шине, коллектор соединен с катодом диода, анод которого соединен с базой транзистора, коллектор которого соединен с инверсной выходной шиной и эмиттером составного транзистора, а его эмиттер - с коллектором выходного транзистора первого инвертора. Анод диода через резистор соединен с шиной питания. 1 ил.

| Патент США № 3962589, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-28—Подача