та следования входных импульсов оказывается меньшей, чем допустимая частота для микросхем, на которых выполнен приоритетный дискриминатор.

Цель изобретения - расширение диапазона частот входных импульсов приоритетного дискриминатора.

Цель изобретения достигается тем, что в устройство 2 дополнительно введены два распределителя импульсов с первой и второй входных шин, три RS-триггера, четыре . формирователя импульсов и четыре элемента ИЛИ; из дополнительно введенных блоков образован дополнительный (параллельный) дискриминатор, благодаря чему оказывается во:зможным попеременное (временное) распараллеливание входных сигналов на два канала, что позволяет во время работы одного и каналов обеспечить подготовку к работе (сброс в исходное .состояние) элементов другого. Благодаря этому расширяется диапазон частот входных импульсов приоритетного дискриминатора.

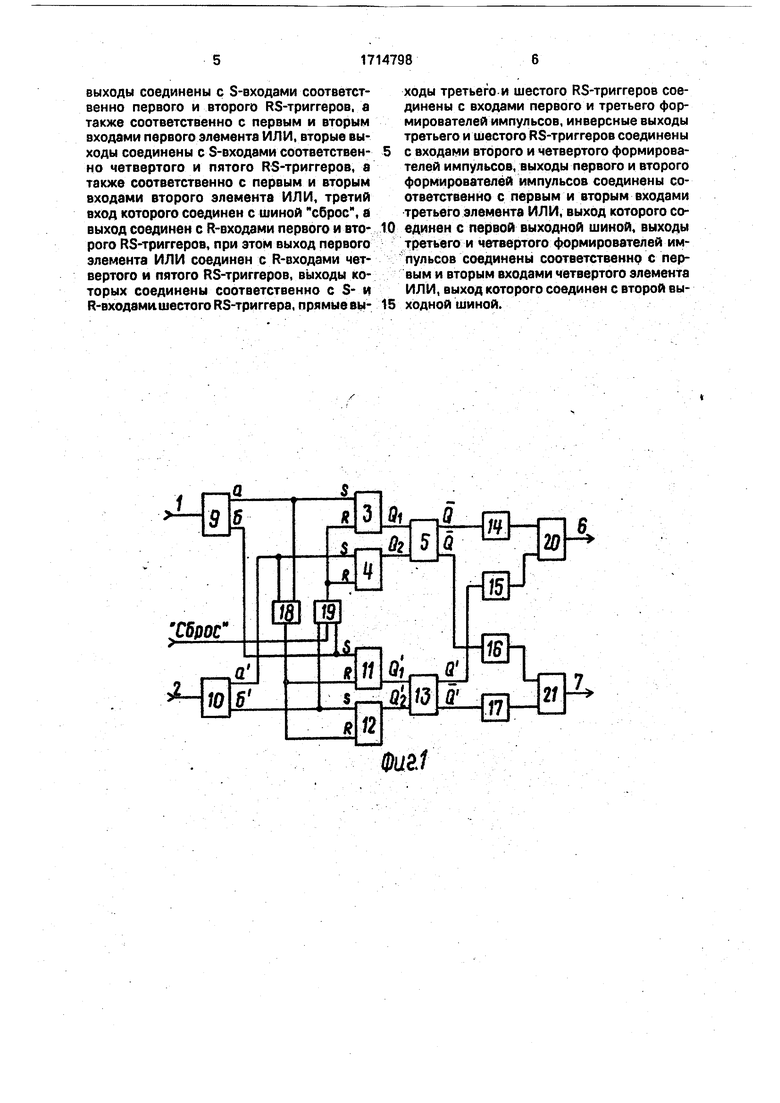

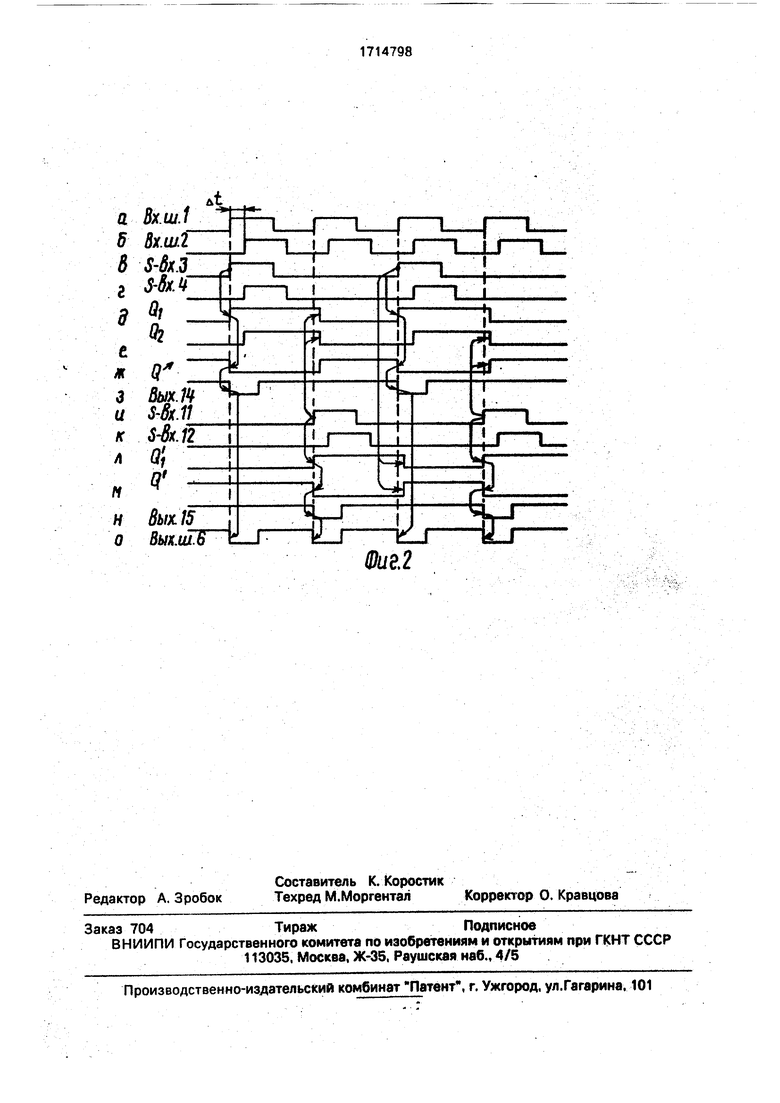

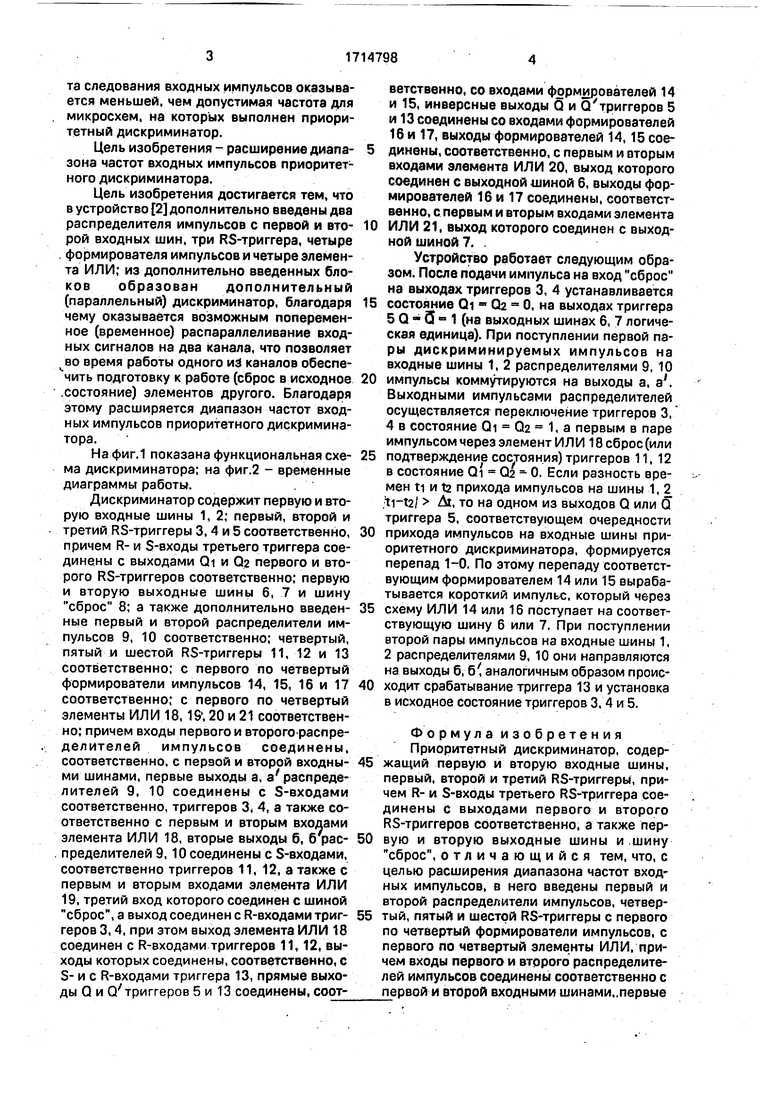

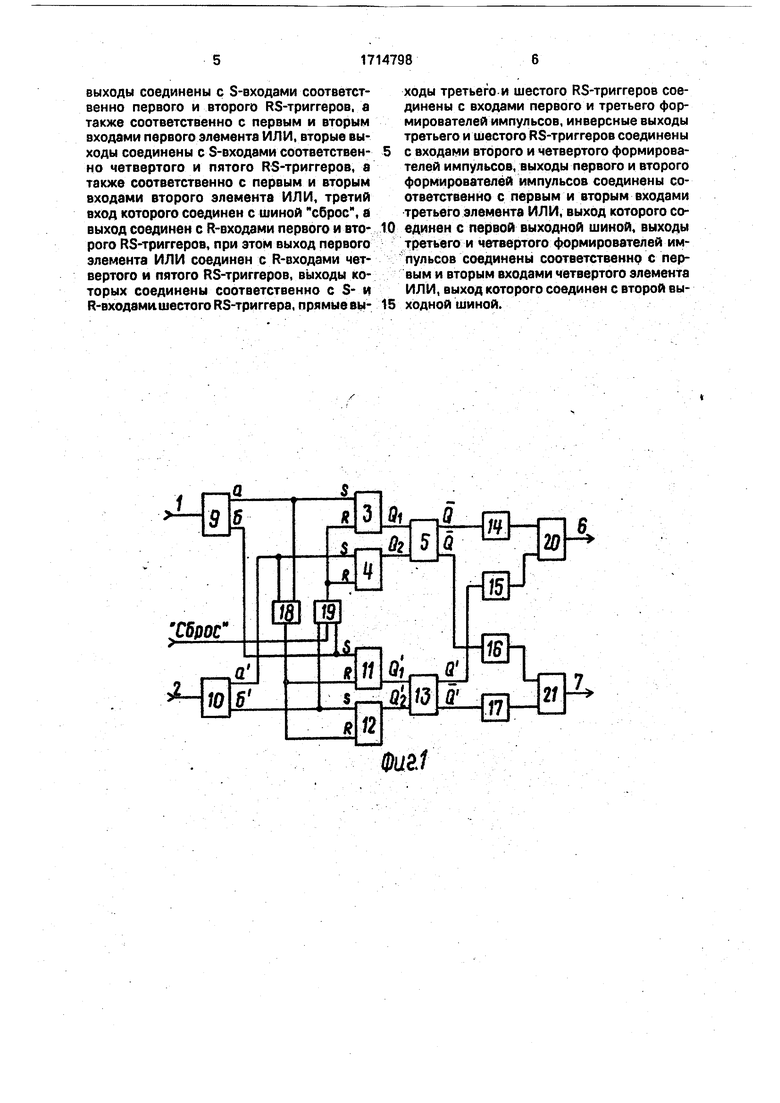

На фиг. 1 показана функциональная схема дискриминатора; на фиг.2 - временные диаграммы работы.

Дискриминатор содержит первую и вторую входные шины 1, 2; первый, второй и третий RS-триггеры 3, 4 и 5 соответственно, причем R- и S-входы третьего триггера соединены с выходами QI и Qa первого и второго RS-триггеров соответственно; первую и вторую выходные шины б, 7 и шину сброс 8; а также дополнительно введенные первый и второй распределители импульсов 9, 10 соответственно; четвертый, пятый и шестой RS-триггеры 11, 12 и 13 соответственно; с первого по четвертый формирователи импульсов 14, 15, 16 и 17 соответственно; с первого по четвертый элементы ИЛИ 18,19,20 и 21 соответственно; причем входы первого и второго распределителей импульсов соединены, соответственно, с первой и второй входными шинами, первые выходы а, а распределителей 9, 10 соединены с S-входами соответственно, триггеров 3, 4, а также соответственно с первым и вторым входами элемента ИЛИ 18, вторые выходы б, б рас. пределителей 9,10 соединены с S-входами, соответственно триггеров 11, 12, а также с первым и вторым входами элемента ИЛИ 19, третий вход которого соединен с шиной сброс, а выход соединен с R-входами триггеров 3,4, при этом выход элемента ИЛИ 18 соединен с R-входами триггеров 11,12, выходы которых соединены, соответственно, с S- и с R-входами триггера 13, прямые выходы Q и Qтриггеров 5 и 13 соединены, соответственно, со входами формирователей 14 и 15, инверсные выходы Q и О триггеров 5 и 13 соединены со входами формирователей 16 и 17, выходы формирователей 14,15 соединены, соответственно, с первым и вторым входами элемента ИЛИ 20, выход которого соединен с выходной шиной 6, выходы формирователей 16 и 17 соединены, соответственно, с первым и вторым входами элемента

0 ИЛИ 21, выход которого соединен с выходной шиной 7. .

Устройство работает следующим образом. После подачи импульса на вход сброс на выходах триггеров 3, 4 устанавливается

5 состояние Qi « 02 О, на выходах триггера 5 Q - 3 1 (на выходных шинах 6, 7 логическая единица). При поступлении первой пары дискриминируемых импульсов на входные шины 1, 2 распределителями 9, 10

0 импульсы коммутируются на выходы а, а . Выходными импульсами распределителей осуществляется переключение триггеров 3, 4 в состояние Qi Qa 1, а первым в паре импульсом через элемент ИЛ И 18 сброс (или

5 подтверждение состояния) триггеров 11,12 в состояние Qi Q2 0. Если разность времен ti и t2 прихода импульсов на шины 1, 2 ;ti-t2/ At, то на одном из выходов Q или Q триггера 5, соответствующем очередности

0 прихода импульсов на входные шины приоритетного дискриминатора, формируется перепад 1-0. По этому перепаду соответствующим формирователем 14 или 15 вырабатывается короткий импуль :, который через

5 схему ИЛИ 14 или 16 поступает на соответствующую шину 6 или 7. При поступлении второй пары импульсов на входные шины 1, 2 распределителями 9, 10 они направляются на выходы б, б , аналогичным образом происходит срабатывание триггера 13 и установка в исходное состояние триггеров 3.4 и 5.

Формулаизобретения Приоритетный дискриминатор, содержащий первую и вторую входные шины, первый, второй и третий RS-триггеры, причем R- и S-входы третьего RS-триггера соединены с выходами первого и второго RS-триггеров соответственно, а также первую и вторую выходные шины и .шину сброс, отличающийся тем, что, с целью расширения диапазона частот входных импульсов, в него введены первый и второй распределители импульсов, четвертый, пятый и шестой RS-триггеры с первого по четвертый формирователи импульсов, с первого по четвертый элеме нты ИЛИ, причем входы первого и второго распределителей импульсов соединены соответственно с

гюрвой и второй входными шинами,.первые

выходы соединены с S-входами соответственно первого и второго RS-триггеров, а также соответственно с первым и вторым входами первого элемента ИЛИ, вторые выходы соединены с S-входами соответственно четвертого и пятого RS-триггеров, а также соответственно с первым и вторым входами второго элемента ИЛИ, третий вход которого соединен с шиной сброс, 6 выход соединен с R-входами первого и второго RS-триггеров, при этом выход первого элемента ИЛИ соединен с R-входами четвертого и пятого RS-триггеров, выходы которых соединены соответственно с S- и R-вxoдaмli шестого RS-триггера, прямые выходы третьего и шестого RS-триггеров соединены с входами первого и третьего формирователей импульсов, инверсные выходы третьего и шестого RS-триггеров соединены с входами второго и четвертого формирователей импульсов, выходы первого и второго формирователей импульсов соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с первой выходной шиной, выходы третьего и четвертого формирователей импульсов соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с второй выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

| Многопрограмный распределитель импульсов | 1987 |

|

SU1443163A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Измеритель коротких интервалов времени | 1980 |

|

SU920629A1 |

| Устройство для измерения скорости звука | 1990 |

|

SU1728672A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Цифровой дискриминатор частоты импульсов | 1988 |

|

SU1582344A1 |

Изобретение относится к импульсной технике и может использоваться при создании измерительных и регулирующих устройств повышенного быстродействия. Цель изобретения - расширение диапазона частот входных импульсных последовательностей - достигается введением распределителей 9, 10 импульсов, триггеров 11-13, формирователей 14-17, импульсов, элементов ИЛИ 18-21 и организацией новых структурных свечей. Устройство также содержит входные шины 1, 2, триггеры 3-5, выходные шины 6. 7 и шину "сброс" 8. 2 ил.feИзобретение относится к импульсной технике и может использоваться присозда-. НИИ измерительных и регулирующих устройств повышенного быстродействия.Известны устройства (схемы совпаде- ний-антисовпадений), например [1], представляющие собой логические устройства, вырабатывающие выходной сигнал, если на его входы сигналы поступают одновременно.Разрешающее время подобных устройств составляет величину порядка одной наносекунды, что не всегда достаточно.Наиболее близ.ким по технической сущности является приоритетный дискримийа- тор [2], содержащий две входные шиныг первый, второй и третий RS-триггеры, причем R- и S-входы третьего RS-триггера соединены с выходами первого и второго RS-триггеров, соответственно, а также первую и вторую выходные шины и шину"сброс". Третий RS-триггер, в исходном состоянии находящийся в неустойчивом состоянии, когда на его R- и S-входы подан логический нуль (на выходах Q и Q логическая единица), обладает временным разрешением At по порядку поступления ИМПУЛЬСОВ на его R- и S-входы примерно в •IQ'^ раз большим, чем быстродействие используемых в нем элементов.Высокое временное разрешение такого устройства при его конструктивной простоте может обеспечить ему широкое применение, однако при высокой частоте следования дискриминируемых импульсов устройство не работоспособно, т.к. использует ручной сброс в исходное состояние. При использовании для установки приоритетного дискриминатора в исходное состояние его выходных или входных сигналов задержка в цепях сброса ограничивает быстродействие устройства. Предельная часто-|Ь. ^ю00

Фаг/

Вх.ш.1 Вхш. S-dx.3

to 75 . 5M.(

Фие.2

| Мелешко Е.А. | |||

| Морозов А.Г | |||

| Схемы совпадения антисовпадений на основе токового ключа./Приборы и техника эксперимента, 1972, № 3, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1992-02-23—Публикация

1989-12-04—Подача