О О

о

Ю

XI

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1989 |

|

SU1676096A1 |

| Синхронный делитель частоты на 47 | 1990 |

|

SU1714806A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

| Синхронный делитель частоты на 55 | 1990 |

|

SU1721825A1 |

| Синхронный делитель частоты на 12 | 1987 |

|

SU1431068A1 |

| Вычитающий декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383492A1 |

| Синхронный делитель частоты | 1986 |

|

SU1429317A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Синхронный делитель частоты на 9 | 1986 |

|

SU1378055A1 |

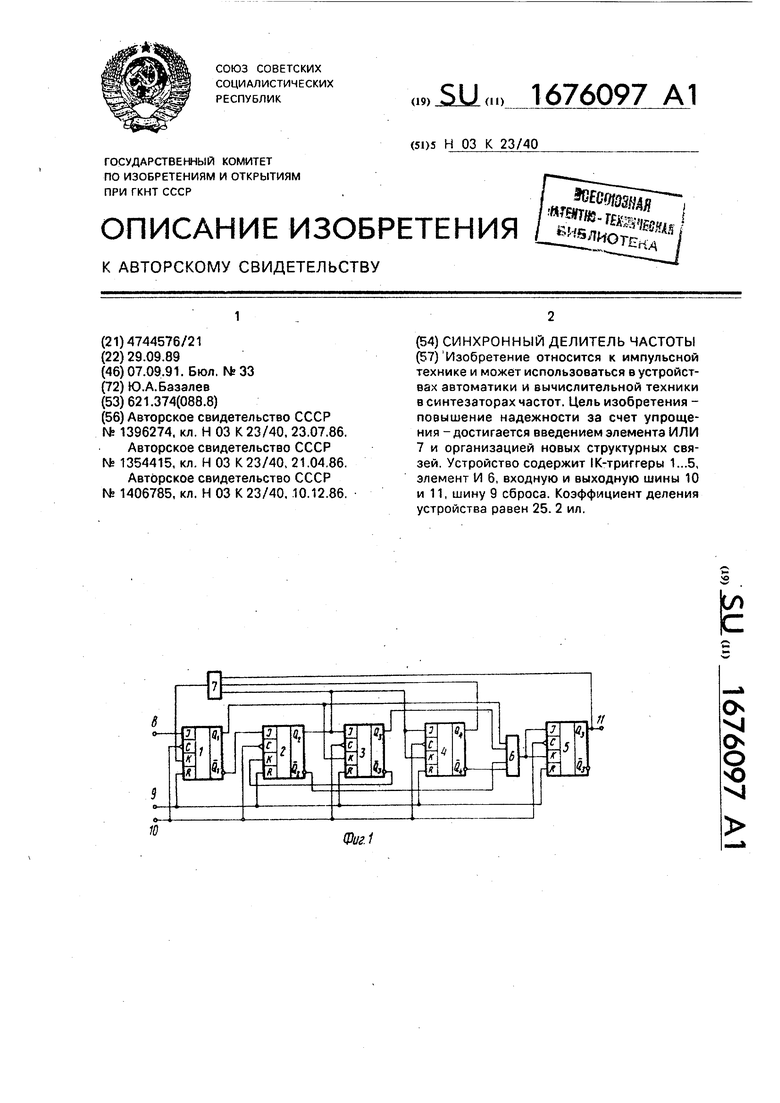

Изобретение относится к импульсной технике и может использоваться в устройствах автоматики и вычислительной техники в синтезаторах частот. Цель изобретения - повышение надежности за счет упрощения -достигается введением элемента ИЛИ 7 и организацией новых структурных связей. Устройство содержит IK-триггеры 1...5, элемент И 6, входную и выходную шины 10 и 11, шину 9 сброса. Коэффициент деления устройства равен 25. 2 ил.

Ю

Фиг1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, в синтезаторах частот в качестве делителя частоты на 25.

Цель изобретения - повышение надежности за счет упрощения.

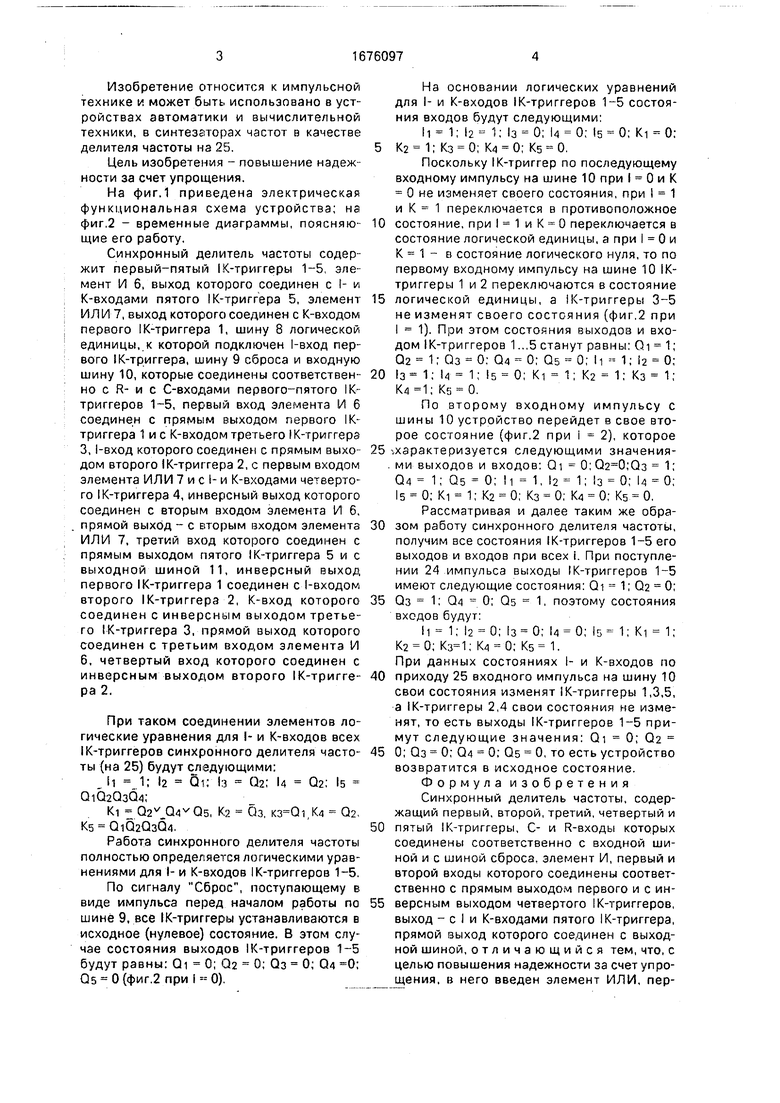

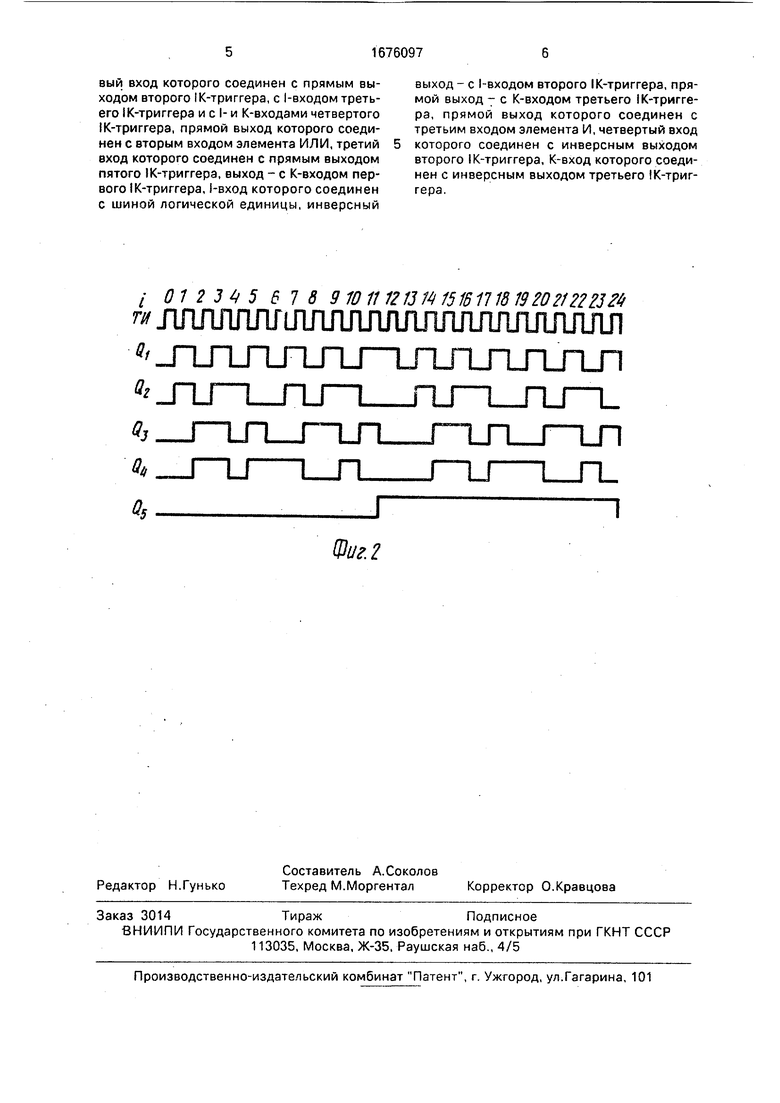

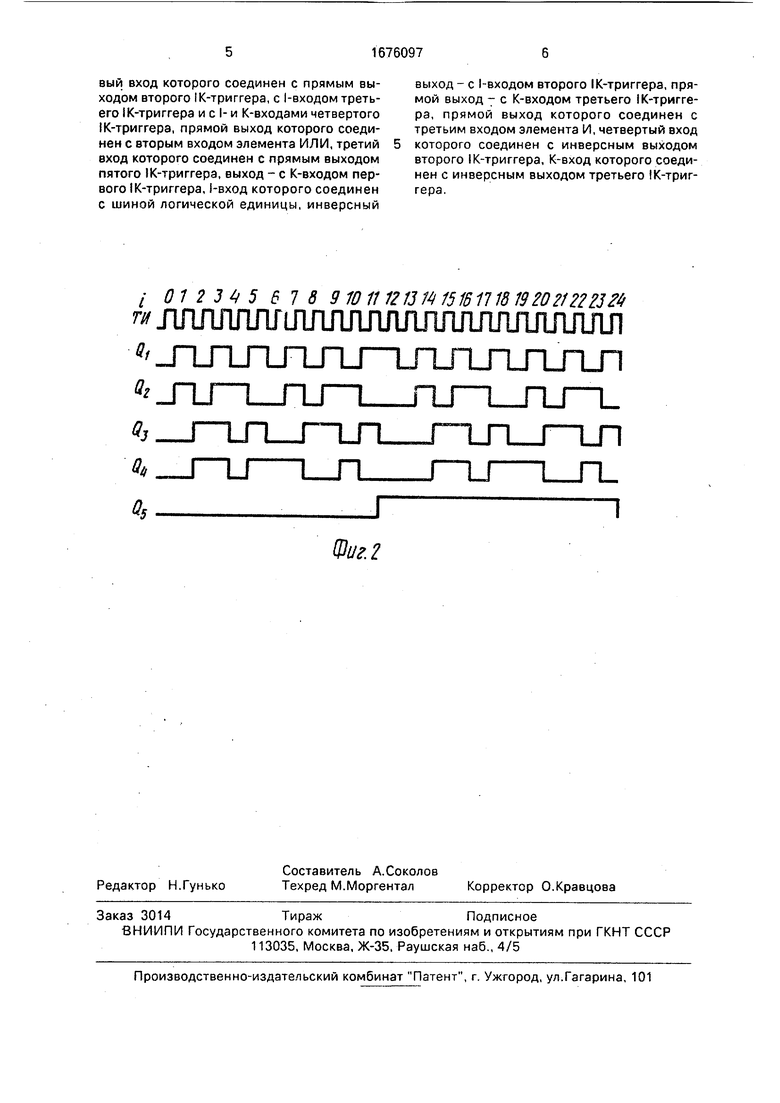

На фиг.1 приведена электрическая функциональная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты содержит первый-пятый IK-триггеры 1-5, элемент И 6, выход которого соединен с I- и К-входами пятого IK-триггера 5, элемент ИЛИ 7, выход которого соединен с К-входом первого IK-триггера 1, шину 8 логической единицы, к которой подключен 1-вход первого IK-триггера, шину 9 сброса и входную шину 10, которые соединены соответственно с R- и с С-входами первого-пятого IK- триггеров 1-5, первый вход элемента И 6 соединен с прямым выходом первого IK- триггера 1 и с К-входом третьего IK-григгера 3,1-вход которого соединен с прямым выходом второго IK-триггера 2, с первым входом элемента ИЛИ 7 и с I- и К-входами четвертого IK-триггера 4, инверсный выход которого соединен с вторым входом элемента И 6, прямой выход - с вторым входом элемента ИЛИ 7, третий вход которого соединен с прямым выходом пятого IK-триггера бис выходной шиной 11, инверсный выход первого IK-триггера 1 соединен с 1-входом второго IK-триггера 2, К-вход которого соединен с инверсным выходом третьего IK-триггера З, прямой выход которого соединен с третьим входом элемента И 6, четвертый вход которого соединен с инверсным выходом второго IK-триггера 2.

При таком соединении элементов логические уравнения для I- и К-входов всех IK-триггеров синхронного делителя частоты (на 25) будут следующими;

И 1; la 6i; з Qz: А Q2; Is 01020з04;

Ki 02 Q4vQs, Ka Оз. ,К4 Ог, K5 QiQ2Q3Q4.

Работа синхронного делителя частоты полностью определяется логическими уравнениями для 1- и К-входов IK-триггеров 1-5.

По сигналу Сброс, поступающему в виде импульса перед началом работы по шине 9, все IK-триггеры устанавливаются в исходное (нулевое) состояние. В этом случае состояния выходов IK-триггеров 1-5 будут равны: Си 0; Qa 0; Оз 0; 04 0; Qs О (фиг.2 при I 0).

На основании логических уравнений для I- и К-входов IK-триггеров 1-5 состояния входов будут следующими:

h 1; 12 1: з 0; М 0; 5 0: Ki 0; К2 1; Кз 0; К4 0; Ks 0.

Поскольку IK-триггер по последующему входному импульсу на шине 10 при I 0 и К 0 не изменяет своего состояния, при I 1 и К 1 переключается в противоположное 0 состояние, при I 1 и К 0 переключается в состояние логической единицы, а при I 0 и К 1 - в состояние логического нуля, то по первому входному импульсу на шине 10 IK- триггеры 1 и 2 переключаются в состояние 5 логической единицы, а IK-триггеры 3-5 не изменят своего состояния (фиг.2 при

1 1), При этом состояния выходов и входом IK-триггеров 1...5 станут равны: Qi 1;

02 1; Оз 0; См 0; Qs 0; 11 1; г 0; 0 1з 1; М 1; Is 0; Ki 1; К2 1; Кз 1;

Ks 0.

По второму входному импульсу с шины 10 устройство перейдет в свое второе состояние (фиг.2 при I 2), которое

5 характеризуется следующими значениями выходов и входов: См 0; 1; 04 1; Qs - 0; h 1, 12 1; з 0; Ц 0; Is 0; Ki 1; К2 0; Кз 0; К« 0; Ks 0. Рассматривая и далее таким же обра0 зом работу синхронного делителя частоты, получим все состояния IK-триггеров 1-5 его выходов и входов при всех I. При поступлении 24 импульса выходы IK-триггеров 1-5 имеют следующие состояния: Qi 1; Q2 0;

5 Оз 1: Q4 0; Qs 1, поэтому состояния входов будут:

И 1; 12 0; з 0; l4 0; I5 1; Ki 1; Ка 0; К4 0; Ks 1. При данных состояниях I- и К-входов по

0 приходу 25 входного импульса на шину 10 свои состояния изменят IK-триггеры 1,3,5, а IK-триггеры 2,4 свои состояния не изменят, то есть выходы IK-триггеров 1-5 примут следующие значения: Си 0; Q2

5 0; Оз 0; Q4 0; Qs 0, то есть устройство возвратится в исходное состояние. Формула изобретения Синхронный делитель частоты, содержащий первый, второй, третий, четвертый и

0 пятый IK-триггеры, С- и R-входы которых соединены соответственно с входной шиной и с шиной сброса, элемент И, первый и второй входы которого соединены соответственно с прямым выходом первого и с ин5 вереным выходом четвертого IK-триггеров, выход - с I и К-входами пятого IK-триггера, прямой выход которого соединен с выходной шиной, отличающийся тем, что, с целью повышения надежности за счет упрощения, в него введен элемент ИЛИ, первый вход которого соединен с прямым выходом второго IK-триггера, с l-входом третьего IK-триггера и с I- и К-входами четвертого IK-триггера, прямой выход которого соединен с вторым входом элемента ИЛИ, третий вход которого соединен с прямым выходом пятого JK-триггера, выход - с К-входом первого IK-триггера, -вход которого соединен с шиной логической единицы, инверсный

/ 012345 е 1 в зюн 1213 м 15КП1Вяюгппзгь

жишплгитпшшл/итшшшши

JTJTJTJnJTJ nJTJTJlJl riJ-l

Фиг. 2

выход- с l-входом второго IK-триггера, прямой выход - с К-входом третьего IK-триггера, прямой выход которого соединен с третьим входом элемента И, четвертый вход которого соединен с инверсным выходом второго IK-триггера, К-вход которого соединен с инверсным выходом третьего IK-триггера.

| Синхронный делитель частоты | 1986 |

|

SU1396274A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты | 1986 |

|

SU1406785A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-07—Публикация

1989-09-29—Подача