ч

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

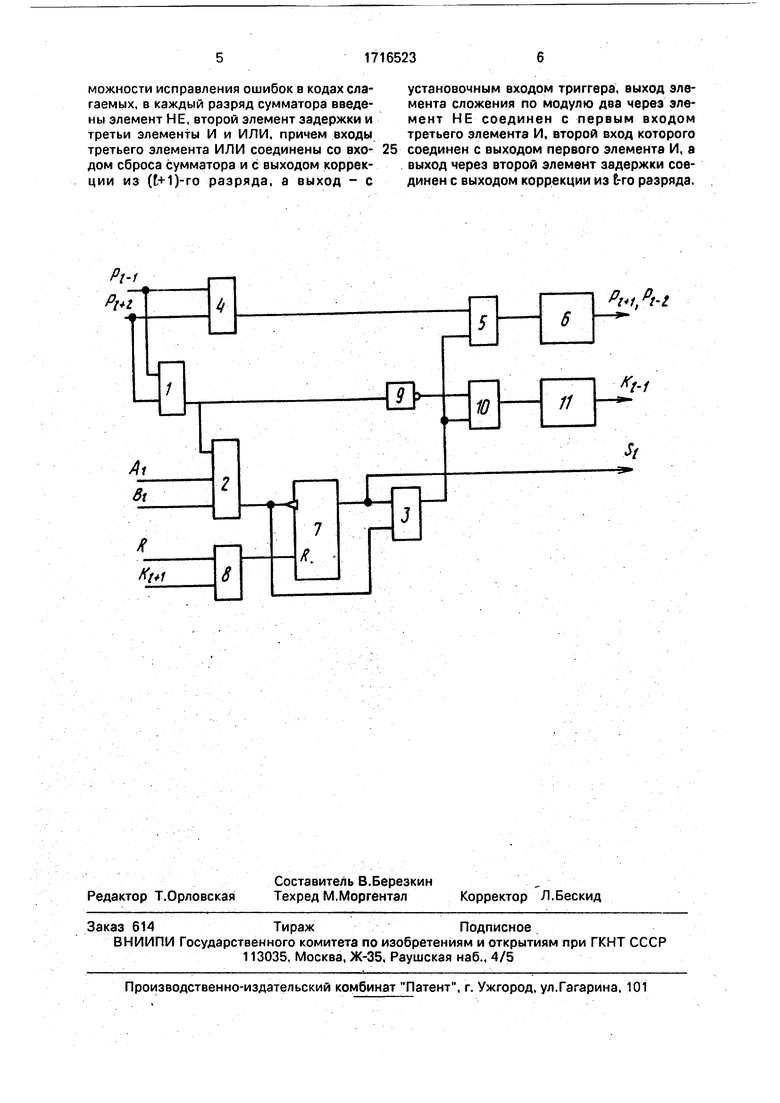

Изобретение относится к области вычислительной техники и может быть использовано при построении цифровых устройств, например вычислительных машин повышенной надежности. Целью изобретения является повышение надежности за счет возможности исправления ошибок в кодах слагаемых, а именно устранение ошибок типа ложная единица в одном из слагаемых в (Ы)-м разряде при сочетании на 6-х разрядах слагаемых двух единиц. В состав каждого разряда сумматора входят элемент сложения 1 по модулю два, три элемента ИЛИ 2, 5, 8, два элемента задержки 6, 11, триггер 7, три элемента ИЗ, 4. 10 и элемент НЕ 9.

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых устройств, например вычислительных машин повышенной надежности.

Целью изобретения является повышение надежности за счет возможности исправления ошибок в кодах слагаемых (ошибок типа ложная единица в одном из слагаемых в (Ы)-м разряде при сочетании на f-x разрядах слагаемых двух единиц).

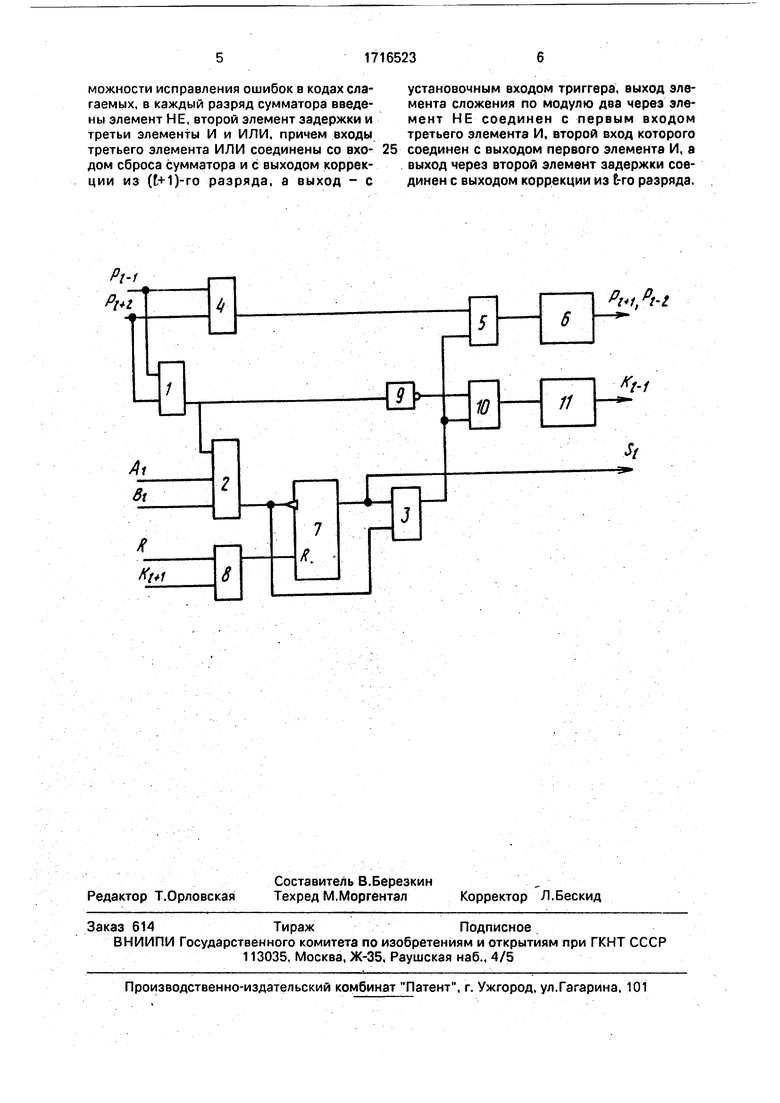

На чертеже показана схема одного Е-го разряда сумматора.

В каждом разряде сумматора элемент сложения 1 по модулю два, выходом подключен к входу элемента ИЛИ 2, выход которого подключен к входу элемента И 3, входы элемента сложения 1 по модулю два соединены с выходами переноса из(С-1)-го

и (t+2)-ro разрядов сумматора и с входами элемента И 4.

Выход элемента ИЛИ 5 подключен к входу элемента задержки 6, выход которого является выходом переноса из t-ro разряда сумматора.

Единичный выход триггера 7 является выходом суммы t-ro разряда сумматора и подключен к входу элемента И 3, выход которого подключен к входу элемента ИЛИ 5.

Выход элемента И 4 подключен к входу элемента ИЛИ 5.

Выход элемента ИЛИ 2 подключен к счетному входу триггера 7, входы элемента ИЛИ 2 подключены к входам разрядов первого (Ас) и второго (60 слагаемых сумматора.

Входы элемента ИЛИ 8 подключены к входу сброса сумматора и выходу коррекций из ()-rp разряда сумматора, а выход - к установочному входу триггера 7. Выход

Оч

ел

ю

С

элемента И 3 подключен к входу элемента И 10, выход элемента сложения 1 по модулю два подключен к входу элемента НЕ 9, выход которого подключен к входу элемента И 10, выход элемента И 10 подключен к входу элемента задержки 11, выход которого является выходом коррекции 1-го разряда сумматора.

Сумматор работает следующим образом.

Перед началом работы поступает сигнал на вход сброса, который, проходя через элемент ИЛИ 8, устанавливает триггеры 7 всех разрядов сумматора в нулевое состояние. При Ар1, . и РрО. , на вход элемента ИЛИ 2 поступает единичный импульс. На выходе элемента ИЛИ 2 образуется импульс, который по заднему фронту перебросит триггер 7 в единичное состояние. Так как выход триггера 7 соединен с выходом разряда суммы, на выходе 1-го разряда сумматора организуется сигнал Si.

Затем поступает второе слагаемое, по заднему фронту сигнала которого триггер 7 перебросится в нулевое состояние, причем образуется импульс на выходе элемента И 3, который поступает через элемент ИЛИ 5 на элемент задержки 6.

Так как отсутствует переносы из (Ы)-го и (Е+2)-го разрядов сумматора, на выходе элемента сложения 1 по модулю два сигнал отсутствует, и поэтому на выходе элемента НЕ 9 сигнал 1, на выходе элемента И 10 образуется импульс, поступающий на элемент задержки 11, на выходе которого обра- зуется сигнал коррекции Ки, поступающий на (Р-1)-й разряд сумматора. Далее на выходе элемента ИЛИ 5 образуется импульс, на выходе элемента задержки 6 образуется импульс, являющийся переносом Ptb(t+1)-u и (Ј-2)-й разряды сумматора. Так как те тц, то сперва образуется сигнал коррекции, а потом сигнал переноса.

В случае АН), , на выходе элемента И 4 образуется импульс, кото- рый через элемент ИЛИ 5 поступает на элемент задержки 6, на выходе которого организуется импульс переноса, сдвинутый на TQ.

В случае АрО, ВрЮ. и обра- зуется сигнал на выходе элемента сложения 1 по модулю два, который, проходя через элемент ИЛИ 3, устанавливает триггер 7 в единичное состояние. На выходе ЗЕПОЯВИТ- ся единичный сигнал. На этом сложение за- канчивается.

Теперь рассмотрим случай исправления входного кода.Предположим,на входы (1+ 2}-ro,(&- ,Јro ( (Е- ,(e-3)-ro,(t-4}-ro

ора подаются слаи (fr-5)-ro разрядов сумма гаемые

А 00101000.... и 6 01001000

Так как для кодов Фибоначчи в минимальной форме за единицей должно следовать минимум Р нулей, в| кодах Фибоначчи при возникновение/звух единиц расценивается как ошибка и требует исправления. Предположим, чтр в слагаемом А ошибка , тогде образование сигналов будет следующее:i

00101190 А

01001000 | В 00000109 Км 00010000 i РЕМ

00000019 1 Ре-2

01110010| .. S

После окончания подучи слагаемых возникает сигнал коррекции рз (t-2)-ro разряда, который сбросит в О триггер 7 (Е-З)-го разряда, тем самым ошибка в (Е-З)-м разряде исправится.|

При коррекции может придти сигнал переноса из других разрядов. Исправится ошибка ложная единица, возникающая только в одном из слагаем ых А или В в (Ы)-м разряде в случае, если коды 1-х разрядов слагаемых А и В равны 1.|

j

Форм у л а изобретения Накапливающий сумматор кодов Фибоначчи, содержащий в каждом 0-м разряде

( n - количество разрядов) элемент

сложения по модулю два,триггер, первый и второй элементы ИЛИ, первый и второй элементы И и первый элемент задержки, причем входы элемента сложения по модулю два соединены с выходами переноса из (Е- 1)-го и (Ј-2)-го разрядов фмматора, первый и второй входы первого э лемента ИЛИ соединены со входами f-x разрядов первого и

второго слагаемых сумма но, третий вход первого s

ора соответствен- лемента ИЛИ соединен с выходом элемента сложения по модулю два, выход первого элемента ИЛИ соединен со счетным входом триггера и с первым входом первого алемента И, выход триггера соединен со вторым входом первого элемента И и с выходов t-ro разряда суммы сумматора, первый и второй входы второго элемента И соединены с соответствующими входами элемента сложения по модулю два, а выход подключен к первому входу второго элемента /1ЛИ, второй вход которого соединен с выходом первого элемента И, а выход соединен со входом первого элемента задержку, выход которого соединён с выходом переноса из t-ro разряда сумматора, отличающийся тем, что, с целью повышения надежности за счет возможности исправления ошибок в кодах слагаемых, в каждый разряд сумматора введены элемент НЕ, второй элемент задержки и третьи элементы И и ИЛИ, причем входы

установочным входом триггера, выход элемента сложения по модулю два через элемент НЕ соединен с первым входом третьего элемента И, второй вход которого

третьего элемента ИЛИ соединены со вхо- 25 соединен с выходом первого элемента И, а дом сброса сумматора и с выходом коррек- выход через второй элемент задержки сое- ции из (t+1)-ro разряда, а выход - с динен с выходом коррекции из t-ro разряда.

установочным входом триггера, выход элемента сложения по модулю два через элемент НЕ соединен с первым входом третьего элемента И, второй вход которого

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-28—Публикация

1990-03-15—Подача