Изобретение относится к вычислительной технике и может быть использовано в составе специализированных вычислительных машин, ориентированных на решение матричных задач.

Цель изобретения - сокращение аппаратурных затрат за счет уменьшения числа входов устройства.

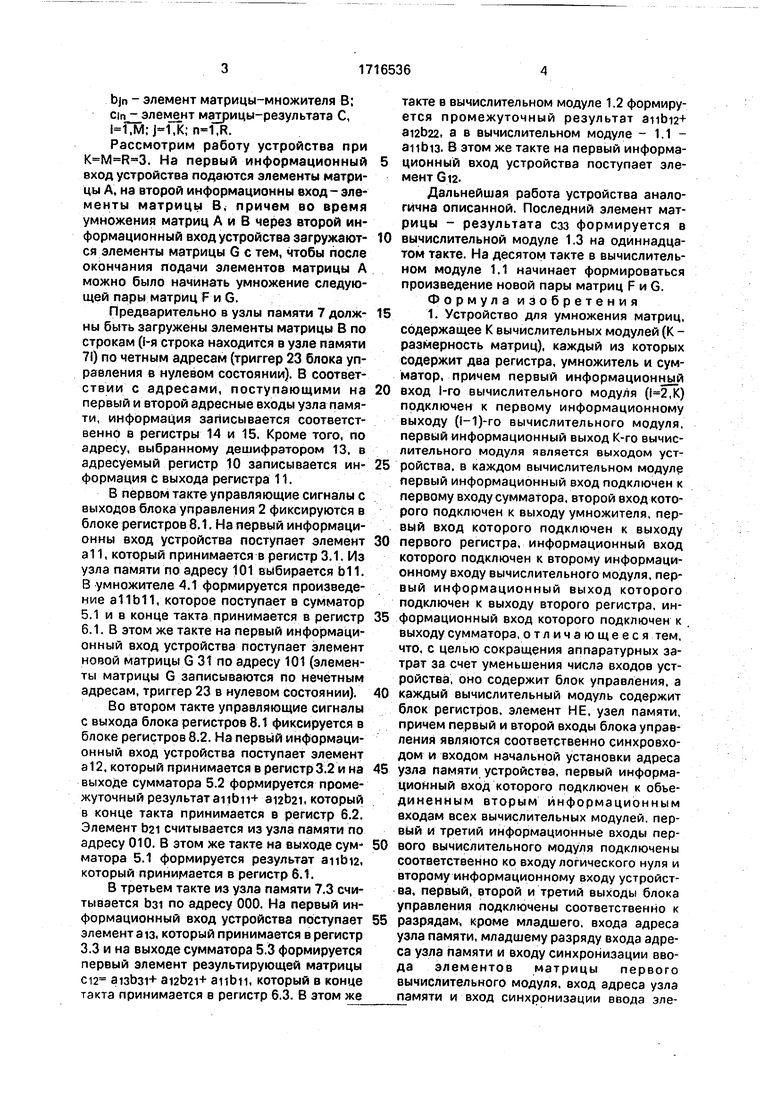

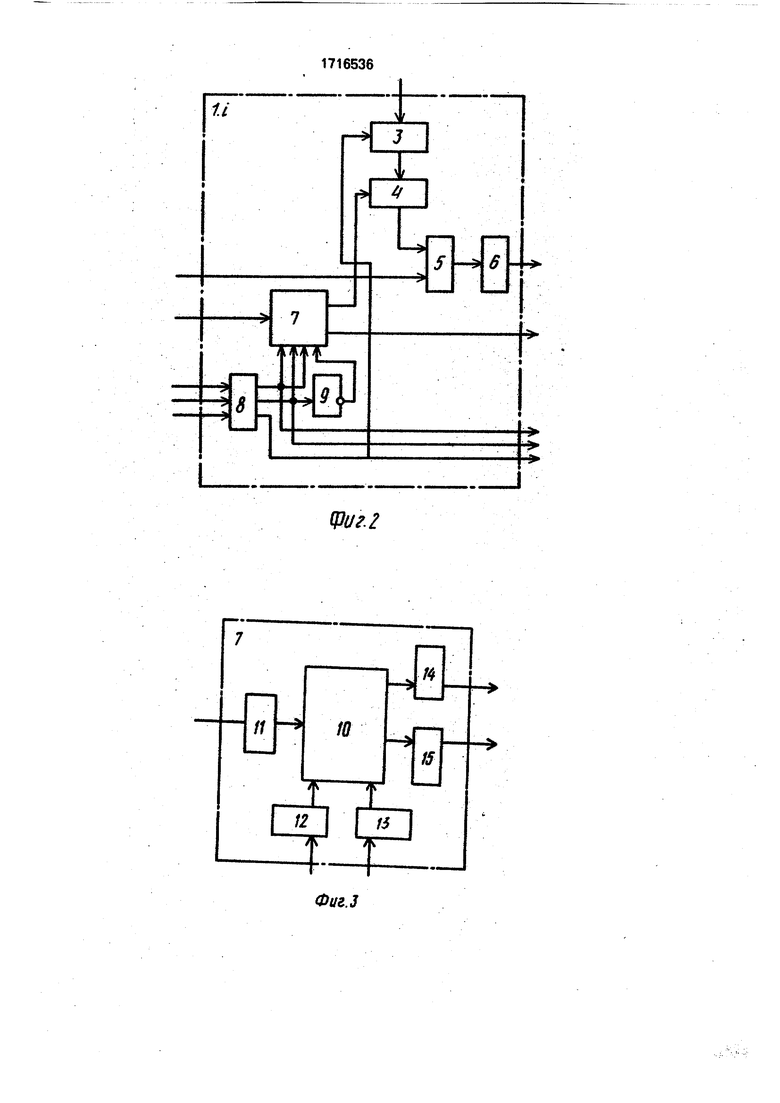

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - функциональная схема вычислительного модуля; на фиг. 3 - пример выполнения узла памяти; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - временные диаграммы, поясняющие работу блока управления.

Устройство (фиг. 1) содержит вычислительные модули 1.1-1,К, где К- размерность

перемножаемых матриц, и блок управления 2. . .... . ....

Каждый вычислительный модуль (фиг. 2) содержит первый регистр 3, умножитель 4, сумматор 5, второй регистр 6, узел памяти 7, блок регистров 8 и элемент НЕ 9.

Узел памяти 7 (фиг.4) содержит адресуемый регистр 10, регистр 11. дешифраторы 12 и 13, регистры 14 и 15.

Блок управления (фиг. 4) содержит регистр 16, элементы ИЛИ 17 и 18, счетчики 19 и 20, дешифраторы 21 и 22, триггер 23.

При реализации умножения матриц устройство вычисляет выражение вида

C-A B ai.bjn} Јcin.

Os

сл со

СКгде сщ X щ, , i 1

ац - элемент матрицы-множимого А;

bjn - элемент матрицы-множителя В;

cin - элемент матрицы-результата С,

l-1,M;J-1,K;n-1,R.

Рассмотрим работу устройства при . На первый информационный вход устройства подаются элементы матрицы А, на второй информационны вход- элементы матрицы В, причем во время умножения матриц А и В через второй информационный вход устройства загружают- ся элементы матрицы G с тем, чтобы после окончания подачи элементов матрицы А можно было начинать умножение следующей пары матриц F и G.

Предварительно в узлы памяти 7 долж- ны быть загружены элементы матрицы В по строкам (i-я строка находится в узле памяти 71) по четным адресам (триггер 23 блока управления в нулевом состоянии). В соответствии с адресами, поступающими на первый и второй адресные входы узла памяти, информация записывается соответственно в регистры 14 и 15. Кроме того, по адресу, выбранному дешифратором 13, в адресуемый регистр 10 записывается ин- формация с выхода регистра 11.

В первом такте управляющие сигналы с выходов блока управления 2 фиксируются в блоке регистров 8.1. На первый информационны вход устройства поступает элемент а11, который принимается в регистр 3.1, Из узла памяти по адресу 101 выбираетсяЫ1. В умножителе 4.1 формируется произведение а11Ы1, которое поступает в сумматор 5.1 и в конце такта принимается в регистр 6.1. В этом же такте на первый информационный вход устройства поступает элемент новой матрицы G 31 по адресу 101 (элементы матрицы G записываются по нечётным адресам, триггер 23 в нулевом состоянии).

Во втором такте управляющие сигналы с выхода блока регистров 8.1 фиксируется в блоке регистров 8.2. На первый информационный вход устройства поступает элемент а 12, который принимается в регистр 3.2 и на выходе сумматора 5.2 формируется промежуточный результат aiibn+ 312021, который в конце такта принимается в регистр 6.2. Элемент 021 считывается из узла памяти по адресу 010. В этом же такте на выходе сум матора 5.1 формируется результат anbi2. который принимается в регистр 6.1.

В третьем такте из узла памяти 7.3 считывается Ьз1 по адресу 000. На первый информационный вход устройства поступает элемент a is, который принимается в регистр 3.3 и на выходе сумматора 53 формируется первый элемент результирующей матрицы ci2 атзЬз1+ ai2b2i+ anbn, который в конце такта принимается в регистр 6.3. В этом же

такте в вычислительном модуле 1.2 формируется промежуточный результат anbi2+ ai2D22, а в вычислительном модуле - 1.1 - aiibia. В этом же такте на первый информационный вход устройства поступает элемент Gl2Дальнейшая работа устройства аналогична описанной. Последний элемент матрицы - результата сзз формируется в вычислительной модуле 1.3 на одиннадцатом такте. На десятом такте в вычислительном модуле 1.1 начинает формироваться произведение новой пары матриц F и G. Формула изобретения 1. Устройство для умножения матриц, содержащее К вычислительных модулей (К - размерность матриц), каждый из которых содержит два регистра, умножитель и сумматор, причем первый информационный вход 1-го вычислительного модуля ,К) подключен к первому информационному выходу ()-1)-го вычислительного модуля, первый информационный выход К-го вычислительного модуля является выходом устройства, в каждом вычислительном модуле первый информационный вход подключен к первому входу сумматора, второй вход которого подключен к выходу умножителя, первый вход которого подключен к выходу первого регистра, информационный вход которого подключен к второму информационному входу вычислительного модуля, первый информационный выход которого подключен к выходу второго регистра, информационный вход которого подключен к выходу сумматора, отличающееся тем, что, с целью сокращения аппаратурных затрат за счет уменьшения числа входов устройства, оно содержит блок управления, а каждый вычислительный модуль содержит блок регистров, элемент НЕ, узел памяти, причем первый и второй входы блока управления являются соответственно синхровхо- дом и входом начальной установки адреса узла памяти устройства, первый информационный вход которого подключен к объединенным вторым йнформациониым входам всех вычислительных модулей, первый и третий информационные входы первого вычислительного модуля подключены соответственно ко входу логического нуля и второму информационному входу устройства, первый, второй и третий выходы блока управления подключены соответственно к разрядам, кроме младшего, входа адреса узла памяти, младшему разряду входа адреса узла памяти и входу синхронизации ввода элементов матрицы первого вычислительного модуля, вход адреса узла памяти и вход синхронизации ввода элементов матрицы i-ro вычислительного модуля подключены к одноименным выходам I- 1 -го вычислительного модуля, в каждом вычислительном модуле разряды входа адреса узла памяти, кроме младшего, млад- ший разряд входа адреса узла памяти и вход синхронизации ввода элементов матрицы подключены к информационным входам со ответственно первого, второго и третьего регистров блока, выход первого регистра которого подключен к объединенным первому и второму входам адреса узла памяти и разрядам, кроме младшего, выхода адреса узла памяти вычислительного модуля, младший разряд которого подключен к младшему разряду первого входа адреса узла памяти, входу элемента НЕ и выходу второго регистра блока, выход третьего регистра которого подключен к синхровходу первого регистра и выходу синхронизации ввода элементов матрицы вычислительного модуля, выход элемента НЕ подключен к младшему разряду второго входа адреса узла памяти, информационный вход которого является третьим информационным входом вычисли- тельного модуля, второй информационный выход которого подключен к первому информационному выходу узла памяти, второй информационный выход которого подключен ко второму входу умножителя,

2. Устройство по п.1. о т л и ч а ю щ е е- с я тем. что блок управления содержит. регистр, два элемента ИЛИ, два счетчика, два дешифратора и триггер, причем первый вход блока управления подключен к синхровходу регистра и первым входам первого и второго элементов ИЛИ, выходы которых подключены к счетным входам соответственно первого и второго счетчиков, объеди- ненные входы установки которых подключены к выходу регистра, информационный вход которого является вторым входом блока управления, первый выход которого подключен к выходу первого счетчика и входу первого дешифратора, выход которого подключен ко второму входу первого элемента ИЛИ, входу обнуления второго счетчика, второму выходу блока управления, третий выход которого подключен к выходу триггера, счетный вход которого подключен ко второму входу второго элемента ИЛИ и выходу второго дешифратора, вход которого подключен к выходу второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1705836A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Генератор функций Уолша | 1984 |

|

SU1241218A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

Изобретение относится к области вычислительной техники и может быть использовано в составе специализированных вычислительных машин. Цель изобретения - сокращение аппаратурных затрат за счет уменьшения числа входов устройства. Цель достигается тем, что в устройство, содержащее линейку из К вычислительных модулей (К - размерность матриц) и блок управления, предварительно записываются элементы матрицы-множителя, а матрица - множимое поступает последовательно на первый информационный вход устройства. Одновременно с вычислением произведения одной пары матриц на второй информационный вход устройства поступают элементы матрицы - множителя следующей пары матриц. 5 ил.

/

Т

V

«н

,...Ј,

«

-

/./Г

Фиг.1

1716536

8

1Ф

::ifnJ

//

to

L J.

П

J

1 -4--J

Фиг.З

t-i

I

Ш

J

Загрузм матрицы

операндам кг-такт , - 7 ..

--4 ( 7 I Z .1

Фиг А

| R.B | |||

| Vrguhart and D | |||

| Wood | |||

| Systolic matrix and vector multiplication methods for signal Processing | |||

| IEE Proceedings, vol | |||

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| F, t 6, Oct | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Матричное устройство для вычисления свертки | 1987 |

|

SU1494018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-28—Публикация

1989-10-17—Подача