Изобретение относится к вычислительной технике и может найти применение при построении арифметических устройств.

Целью изобретения является сокращение количества оборудования.

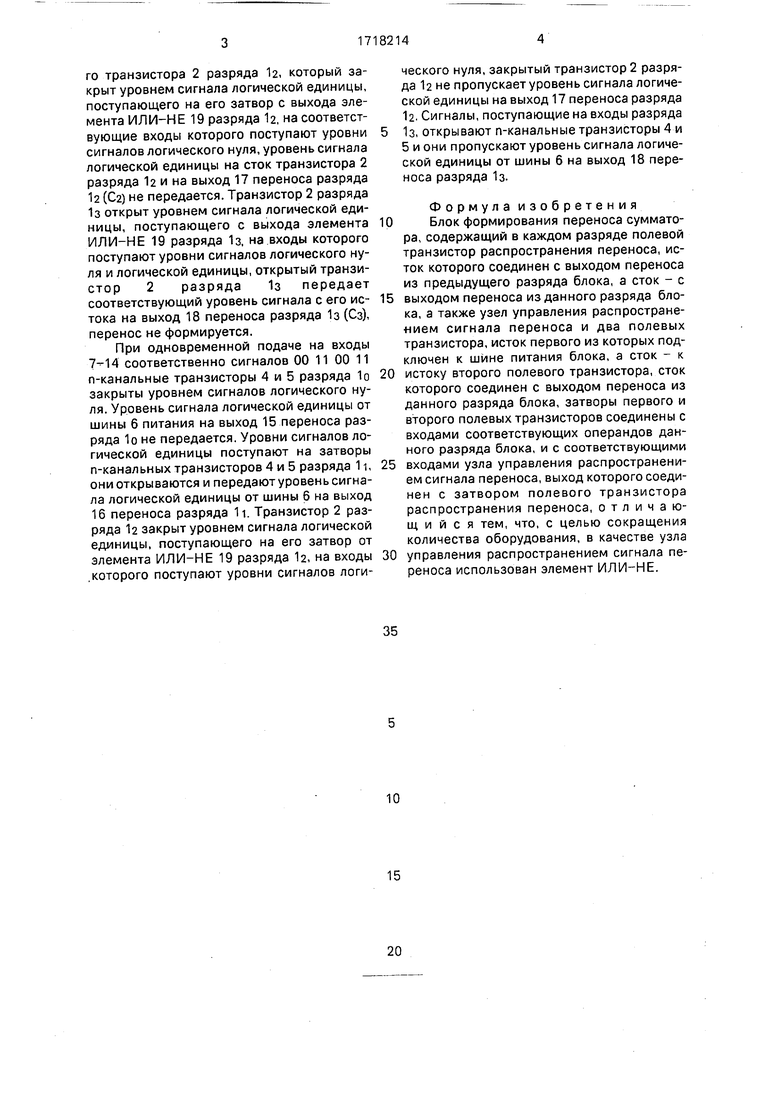

На чертеже приведена схема четырех разрядов (с первого по четвертый) блока.

Каждый разряд 1i (, 1, 2, 3) блока, кроме первого, содержит полевой транзистор 2 (р-канальный МОП-транзистор) распространения переноса, узел 3 управления распространением сигнала переноса и два полевых транзистора 4 и 5 (п-канальные МОП-транзисторы). Первый разряд блока ввиду того, что сигнал входного переноса на блок не подается, содержит только транзисторы 4 и 5. Блок содержит также шину 6 питания Еп и имеет входы 7, 8, 9, 10, 11, 12, 13, 14 операндов А0, В0, Ai, Bi, A2, 62. Аз. Вз и выходы 15, 16,17, 18 переносов С0, Ci, C2, Сз. В качестве узла 3 используется элемент ИЛИ-НЕ 19.

Предлагаемый блок работает следующим образом.

Формирование переносов производится по алгоритму

Ci AiBn/ (AivBQCo

V (Ajv/B2)Cl

()С2.

Рассмотрим два примера функционирования блока.

При одновременном поступлении на входы 7-14 соответственно комбинации 11 01 00 01 n-канальные МОП-транзисторы 4 и 5 разряда 1 ° открыты уровнем сигнала логической единицы, поступающего на их затворы, уровень логической единицы передается на выходы 15 переноса первого разряда Со, а также на исток р-канального транзистора 2 разряда 1i, который, в свою очередь, открыт уровнем сигнала логического нуля, поступающего с выхода элемента ИЛИ-НЕ 19 разряда 1i, на входы которого поступают сигналы логического нуля и логической единицы, транзистор 2 разряда 11 пропускает уровень сигнала логической единицы на выход 16 переноса разряда 11 (Ci), а также на исток р-канально f

fe

00

ю Ј

го транзистора 2 разряда 12, который закрыт уровнем сигнала логической единицы, поступающего на его затвор с выхода элемента ИЛИ-НЕ 19 разряда 12, на соответствующие входы которого поступают уровни сигналов логического нуля, уровень сигнала логической единицы на сток транзистора 2 разряда 12 и на выход 17 переноса разряда

12(С2) не передается. Транзистор 2 разряда

13открыт уровнем сигнала логической единицы, поступающего с выхода элемента ИЛЙ-НЕ 19 разряда 1з, на входы которого поступают уровни сигналов логического нуля и логической единицы, открытый транзистор 2 разряда 1з передает соответствующий уровень сигнала с его ис- тока на выход 18 переноса разряда 1з (Сз), перенос не формируется.

При одновременной подаче на входы 7-14 соответственно сигналов 00 11 00 11 n-канальные транзисторы 4 и 5 разряда 1о закрыты уровнем сигналов логического нуля. Уровень сигнала логической единицы от шины 6 питания на выход 15 переноса разряда 1о не передается. Уровни сигналов логической единицы поступают на затворы n-канальных транзисторов 4 и 5 разряда 11, они открываются и передают уровень сигнала логической единицы от шины 6 на выход 16 переноса разряда 1i. Транзистор 2 разряда 12 закрыт уровнем сигнала логической единицы, поступающего на его затвор от элемента ИЛИ-НЕ 19 разряда 12, на входы .которого поступают уровни сигналов логического нуля, закрытый транзистор 2 разряда 12 не пропускает уровень сигнала логической единицы на выход 17 переноса разряда

12.Сигналы, поступающие на входы разряда

13,открывают n-канальные транзисторы 4 и 5 и они пропускают уровень сигнала логической единицы от шины б на выход 18 переноса разряда 1з.

Ф о р м у л а и з о б р е т е н и я Блок формирования переноса сумматора, содержащий в каждом разряде полевой транзистор распространения переноса, исток которого соединен с выходом переноса из предыдущего разряда блока, а сток - с выходом переноса изданного разряда блока, а также узел управления распространением сигнала переноса и два полевых транзистора, исток первого из которых подключен к шине питания блока, а сток - к истоку второго полевого транзистора, сток которого соединен с выходом переноса из данного разряда блока, затворы первого и второго полевых транзисторов соединены с входами соответствующих операндов данного разряда блока, и с соответствующими входами узла управления распространением сигнала переноса, выход которого соеди- нен с затвором полевого транзистора распространения переноса, отличающийся тем, что, с целью сокращения количества оборудования, в качестве узла управления распространением сигнала переноса использован элемент ИЛИ-НЕ.

L..

18

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Схема формирования переносов сумматора | 1988 |

|

SU1624443A1 |

| Блок формирования переносов параллельного сумматора | 1988 |

|

SU1571576A1 |

| Способ сравнения данных в ячейке ассоциативного запоминающего устройства и модуль сравнения данных в ячейке ассоциативного запоминающего устройства | 2018 |

|

RU2680870C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| Многофазный генератор импульсов | 1974 |

|

SU499652A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| Устройство преобразования уровней логических сигналов на КМОП-транзисторах | 1989 |

|

SU1775853A1 |

| ИНТЕГРАЛЬНАЯ МИКРОСХЕМА РАДИОЧАСТОТНОГО ИДЕНТИФИКАТОРА | 2011 |

|

RU2465645C1 |

Изобретение относится к вычислитель1 ной технике и может найти применение при построении арифметических устройств. Целью изобретения является сокращение количества оборудования. В блоке формирования переноса сумматора в каждом разряде 1 содержится полевой транзистор 2 распространения переноса,узел 3 управления распространением сигнала переноса, в качестве которого использован элемент ИЛИ-НЕ 19, и два полевых транзистора 4 и 5. 1 ил.

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США N: 4471454, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1992-03-07—Публикация

1989-11-23—Подача