С& ГО 4 4 4Ь

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок формирования переносов параллельного сумматора | 1988 |

|

SU1571576A1 |

| Блок формирования переноса | 1989 |

|

SU1679482A1 |

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2020 |

|

RU2749178C1 |

| Блок формирования сквозного переноса в сумматоре | 1979 |

|

SU1042012A1 |

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2017 |

|

RU2664014C1 |

| Динамическая программируемая логическая матрица | 1989 |

|

SU1635217A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Схема сквозного переноса на КМОП-транзисторах | 1988 |

|

SU1529440A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

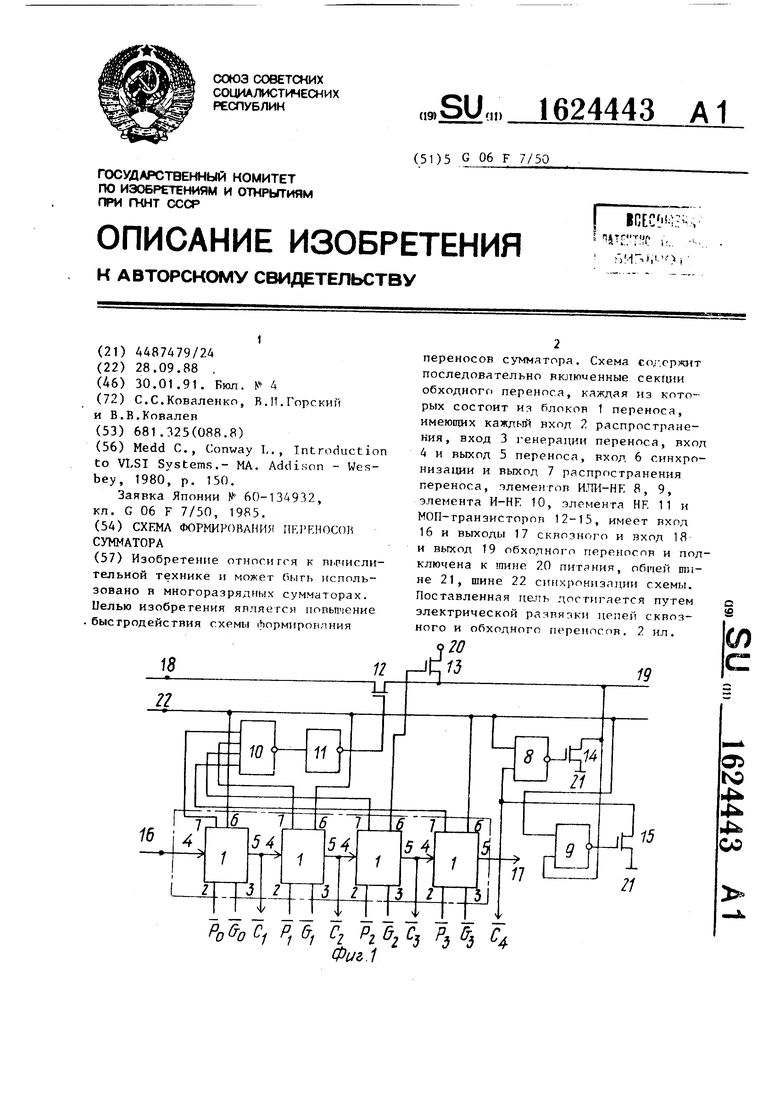

Изобретение относится к вмчисли- тельной технике и может быть использовано в многоразрядных сумматорах. Целью изобретения является повышение .быстродействия схемы Лормироилния переносов сумматора. Схема содержит последовательно включенные секции обходного переноса, каждая из которых состоит из блоков 1 переноса, имеющих каждый вход 2 распространения, вход 3 генерации переноса, вход 4 и выход 5 переноса, вход 6 синхронизации и выход 7 распространения переноса, элементов ИЛИ-НЕ 8, 9, элемента И-НЕ 10, элемента НЕ 11 и МОП-транэисторол 12-15, имеет вход 16 и выходы 17 сквозного и вход 18 и выход 19 обходного переносов и подключена к шине 20 питания, обпей шине 21, шине 22 синхронизации схемы. Поставленная цель достигается путем электрической развязки цепей сквозного и обходного переносов. 2 ил. с Ј

Ро&оС, Р,&, Сг Рг&2С5 Рд % С4 Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в быс гродействутощих многоразрядных сумматорах.

Цель изобретения - повышение быстродействия схемы.

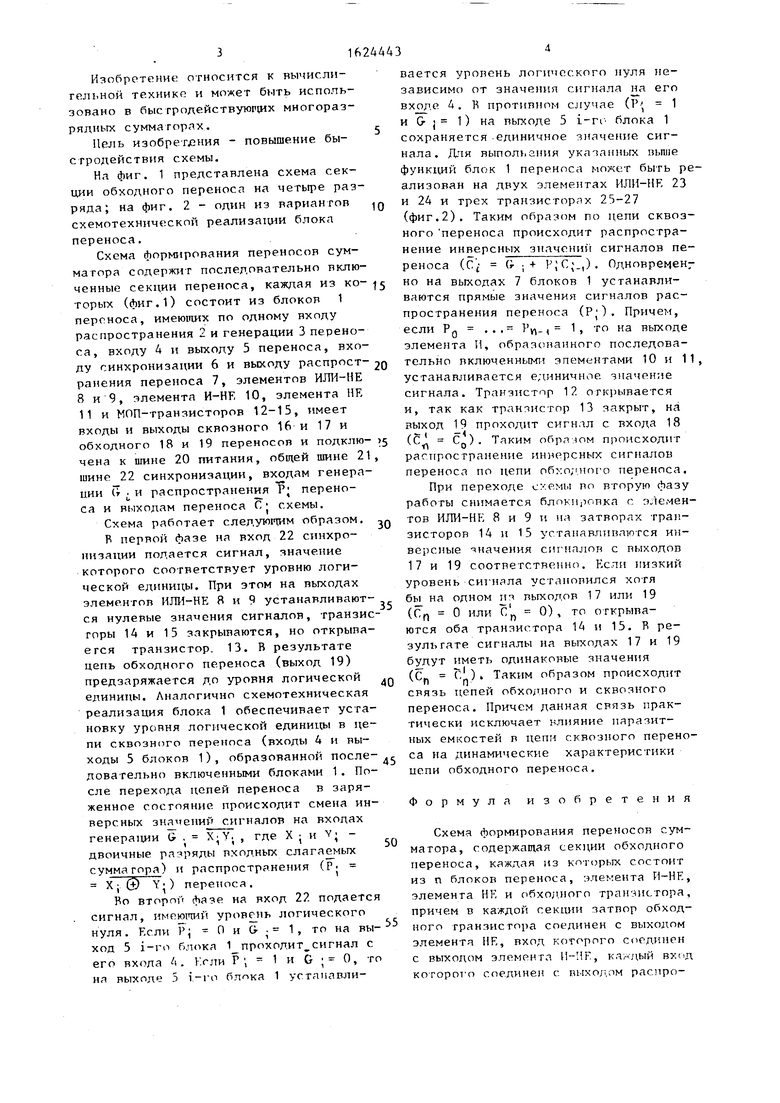

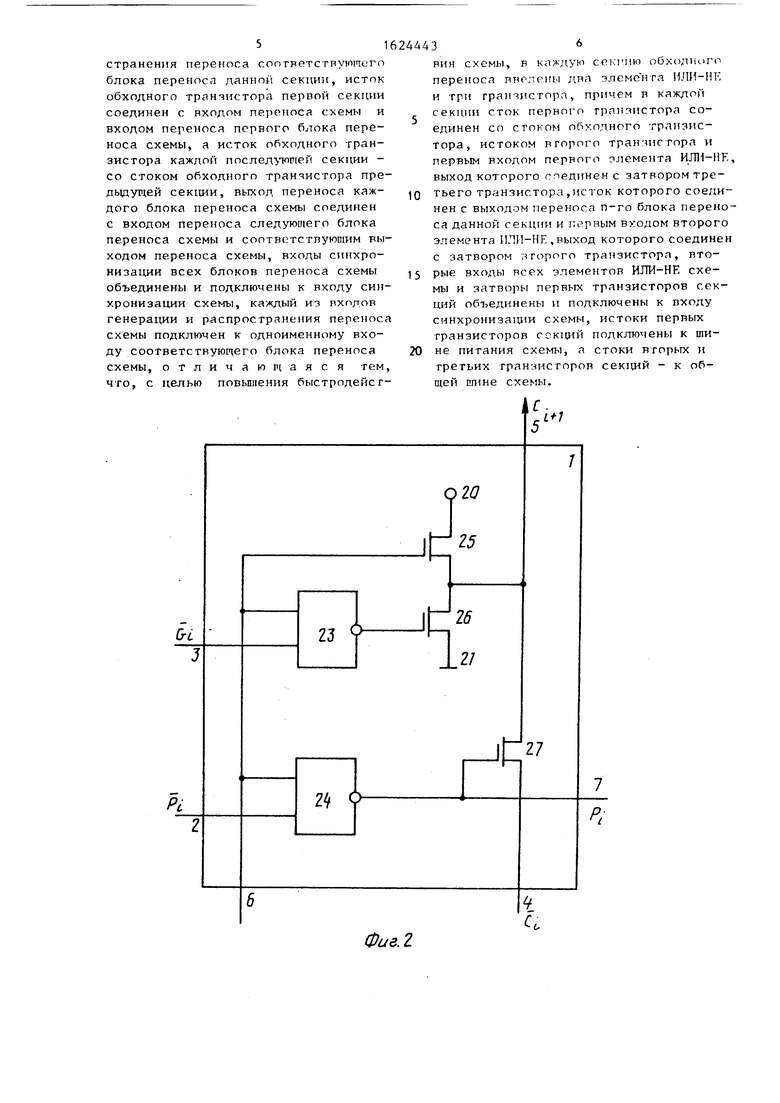

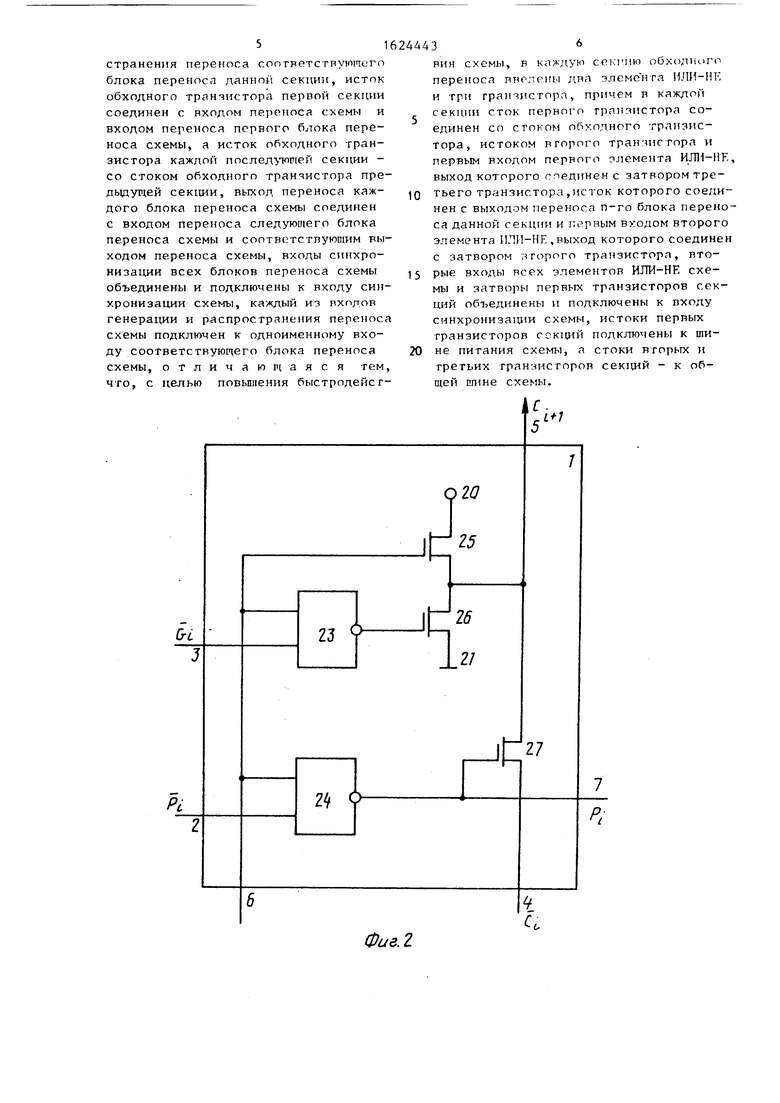

На фиг. 1 представлена схема секции обходного переноса на четыре разряда; на фиг. 2 - один из вариантов схемотехнической реализации блока переноса.

Схема формирования переносов сумматора содержит последовательно включенные секции переноса, каждая из ко- торых (фиг.1) состоит из блоков 1 переноса, имеющих по одному входу распространения 2 и генерации 3 переноса, входу 4 и выходу 5 переноса, входу синхронизации 6 и выходу распрост- ранения переноса 7, элементов ИЛИ-НЕ 8 и 9, элемента И-НЕ 10, элемента НЕ 11 и МОП-транзисторов 12-15, имеет входы и выходы сквозного 16 и 17 и обходного 18 и 19 переносов и подклю- чена к шине 20 питания, общей шине 21 шине 22 синхронизации, входам генерации (V . и распространения Р; переноса и выходам переноса Cj схемы.

Схема работает следующим образом. В первой фазе на вход 22 синхронизации подается сигнал, значение которого соответствует уровню логической единицы. При этом на выходах элементов ИЛИ-НЕ Я и 9 устанавливают

ся нулевые значения сигналов, транзисторы 14 и 15 закрываются, но открывается транзистор. 13. В результате цепь обходного переноса (выход 19) предзаряжается до уровня логической единицы. Аналогично схемотехническая реализация блока 1 обеспечивает установку уровня логической единицы в цепи сквозного переноса (входы 4 и выходы 5 блоков 1), образованной после- довательно включенными блоками 1. После перехода цепей переноса в заряженное состояние происходит смена инверсных значений сигналов на входах генерации G . . , где X j и v - двоичные разряды входных слагаемых сумма гора) и распространения (Р X j (+)Y) переноса.

Но второй фазе на вход 22 подается сигнал, имеющий уровень логического нуля. Если Pj 0 и & . 1, то на выход 5 1-го блока 1 проходит сигнал с его входа 4. Если Р , 1 и G ; 0, то на выходе 5 i-ro 1 устанавли

Q ,

5

вается уровень логического нуля независимо от значения сигнала на его 4. В противном случае (Р 1 и О j 1) на выходе 5 i-П блока 1 сохраняется единичное значение сигнала. Для выпольания укатанных выше функций блок 1 переноса может быть реализован на двух элементах ИЛИ-НЕ 23 и 24 и трех транзисторах 25-27 (фиг.2). Таким образом по цепи сквозного переноса происходит распространение инверсных значений сигналов переноса (C t- (т ; + Р;С;,). Одновременг но на выходах 7 блоков 1 устанавливаются прямые значения сигналов распространения переноса (Р;). Причем, если PQ ... Рм, 1, то на выходе элемента И, образованного последовательно включенными элементами 10 и 11, устанавливается единичное значение сигнала. Транзистор 12 открывается и, так как транзистор 13 закрыт, на выход проходит сигнлл с входа 18 (С CQ). Таким обра-)ом происходит распространение инверсных сигналов переноса по цепи обходного переноса. При переходе схемы во вторую фазу работы снимается блпьировка г эЛемен- тов ИЛИ-НК 8 и 9 и на затворах транзисторов 14 и 15 устанавливаю гея инверсные значения сигналов с выходов 17 и 19 соответственно. Если низкий уровень сигнала установился хотя бы на одном из выходов 17 или 19 (Сп 0 или С п 0), то открываются оба транзистора 14 и 15. В результате сигналы на выходах 17 и 19 будут иметь одинаковые значения (Сп .) Таким образом происходит связь цепей обходного и сквозного переноса. Причем данная связь практически исключает влияние паразитных емкостей в цепи сквозного переноса на динамические характеристики цепи обходного переноса.

Формула изобретения

Схема формирования переносов сумматора, содержащая секции обходного переноса, каждая из которых состоит из п блоков переноса, элемента И-НЕ, элемента НЕ и обходного транзистора, причем в каждой секции затвор обходного транзистора соединен с выходом элемента НЕ, вход которого соединен с выходом эпемента И-MF, каждый вход которого соединен с выходам распро5 ,

странения переноса соответсгвуюишго блока переноса данной секции, исток обходного транзистора первой секции соединен с входом переноса схемы и входом переноса первого блока переноса схемы, а исток обходного транзистора каждой последуюшей секции - со стоком обходного транзистора предыдущей секции, выход переноса каждого блока переноса схемы соединен с входом переноса следующего блока переноса схемы и соответствующим выходом переноса схемы, входы синхронизации всех блоков переноса схемы объединены и подключены к входу синхронизации схемы, каждый из входов генерации и распространения переноса схемы подключен к одноименному входу соответствующего блока переноса схемы, отличающаяся тем, что, с целью повышения быстродейсг

вия схемы, в каждую секгию обходного переноса ввглгны два -элемента ИЛИ-ПК и гри транзистора, причем в каждой секции сток первого транзистора соединен со стоком обходного транзистора, истоком второго транзистора и первым входом первого элемента ИЛИ-НЕ, выход которого соединен с затвором третьего транзистора,исток которого соединен с выходом переноса n-го блока переноса данной секции и первым входом второго элемента ИЛИ-НЕ ,выход которого соединен с затвором згорого транзистора, вто- 5 рые входы всех элементов ИЛИ-НЕ схемы и затворы первых транзисторов секций объединены и подключены к входу синхронизации схемы, истоки первых транзисторов секций подключены к шине питания схемы, а стоки вторых и третьих транзисторов секций - к общей шине схемы.

0

| Medd С., Conway L., Introduction to VLSI Systems.- MA | |||

| Addi.son - Wes- bey, 1980, p | |||

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-30—Публикация

1988-09-28—Подача